Cornell University ECE4760

Real time PIO control

Pi Pico RP2040

The PIO subsystem

The rp2040 has two dedicated I/O processors (PIO) each of which run a striped-down, single cycle, deterministic, assembly language from only 32 words of instruction memory per processor. While this is enough to generate serial protocols, including VGA at 25 million output values/sec, we begin to wonder if it is possible to swap memory on a running PIO in a seamless fashion. This means that memory modifed on-the-fly must not be executed while the program swap is being made, and that the swap is fast enough to not change the deterministic behavior of the PIO.

The DMA subsystem is fast and reasonably deterministic. It can quickly respond to signals from the PIO machines, load code, and reset signal state (clear a PIO input FIFO). As a proof of concept, swapping back and forth between two, two-instruction, program fragments was the simplest scenario I could think of that was testable. Doing the swap and handling the handshaking required chaining most of the DMA channels on the chip. This is clearly not a feasible solution. The DMAcpu machine uses three channels as a general prupose cpu which executes by chaining an arbitrarily long array of DMA control blocks through one physical DMA channel. There is, of course, fetch overhead, but the system is still fairly fast and deterministic. The resulting scheme included:

.wrap_target set pins, 0b10 [1] set pins, 0b00 [2] ; following actual code is loaded on the fly by DMA machine nop nop ; signal DMA machine for new code ; This will STOP the PIO unless the DMA machine reads the FIFO!! push block .wrapThe code which is swapped into the running program in this example follows.

pio_inst[0] = set(pins, 1, inst_delay_long) ; pio_inst[1] = set(pins, 0, 31-inst_delay_long) ; pio_inst[2] = set(pins, 1, inst_delay_short) ; pio_inst[3] = set(pins, 0, 31-inst_delay_short) ;

// define a jump target address label

label(DMA_pgm_addr) ;

// sych with end of pio program

//nop();

pacer(DREQ_PIO0_RX0) ;

// new code to pio

move(pio_inst[0], pio0_hw->instr_mem[offset+2], 2, DMA_SIZE_32, array_read, array_write ) ;

// read FIFO to clear it

// CLEAR aftr write to memory to save time

move(pio0_hw->rxf[0], bit_bucket, 1, DMA_SIZE_32, var_read, var_write );

// synch with pio

pacer(DREQ_PIO0_RX0) ;

// new code to pio

move( pio_inst[2], pio0_hw->instr_mem[offset+2], 2, DMA_SIZE_32, array_read, array_write ) ;

// read FIFO to clear it

move(pio0_hw->rxf[0], bit_bucket, 1, DMA_SIZE_32, var_read, var_write );

// === stop or jump to start of program

label(stop_addr) ;

load_sniff(run) ;

jump_neg(stop_addr, DMA_pgm_addr) ;

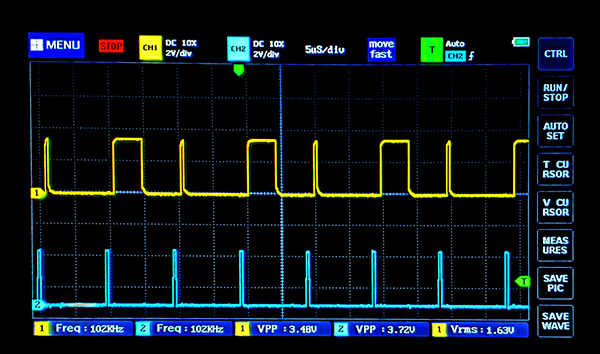

The following image shows the fixed reference pulse on the lower trace and the overlayed long/short pulses on the top trace.

Copyright Cornell University April 24, 2024