# **FIR II IP Core**

**User Guide**

**UG-01072** 2016.05.01 101 Innovation Drive San Jose, CA 95134 www.altera.com

### Contents

| About the FIR II IP Core                             | 1-1 |

|------------------------------------------------------|-----|

| Altera DSP IP Core Features                          |     |

| FIR II IP Core Features                              |     |

| DSP IP Core Device Family Support                    | 1-2 |

| DSP IP Core Verification                             |     |

| FIR II IP Core Release Information                   | 1-3 |

| FIR II IP Core Performance and Resource Utilization  | 1-4 |

| FIR II IP Core Getting Started                       | 2-1 |

| Licensing IP Cores                                   |     |

| OpenCore Plus IP Evaluation                          |     |

| FIR II IP Core OpenCore Plus Timeout Behavior        |     |

| IP Catalog and Parameter Editor                      |     |

| Generating IP Cores                                  |     |

| Files Generated for Altera IP Cores and Qsys Systems |     |

| Simulating Altera IP Cores                           |     |

| Simulating the FIR II IP Core Testbench in MATLAB    |     |

| DSP Builder Design Flow                              | 2-8 |

| FIR II IP Core Parameters                            |     |

| FIR II IP Core Filter Specification                  |     |

| FIR II IP Core Coefficient Settings                  |     |

| FIR II IP Core Coefficients                          |     |

| Loading Coefficients from a File                     |     |

| FIR II IP Core Input and Output Options              |     |

| Signed Fractional Binary                             |     |

| MSB and LSB Truncation, Saturation, and Rounding     |     |

| FIR II IP Core Implementation Options                |     |

| Memory and Multiplier Trade-Offs                     |     |

| FIR II IP Core Reconfigurability                     |     |

| FIR II IP Core Functional Description                | 4-1 |

| FIR II IP Core Interpolation Filters                 | 4-2 |

| FIR Decimation Filters                               |     |

| FIR II IP Core Time-Division Multiplexing            |     |

| FIR II IP Core Multichannel Operation                |     |

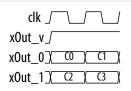

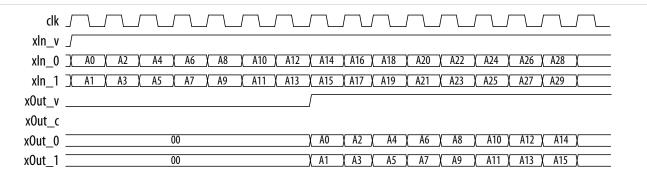

| Vectorized Inputs                                    |     |

| Channelization                                       |     |

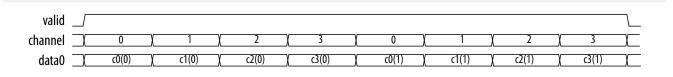

| Channel Input and Output Format                      |     |

| FIR II IP Core Multiple Coefficient Banks            |     |

|                                                      |     |

FIR II IP Core User Guide

| IUC-J |

|-------|

|-------|

| FIR II IP Core Coefficient Reloading  |     |

|---------------------------------------|-----|

| Reconfigurable FIR Filters            |     |

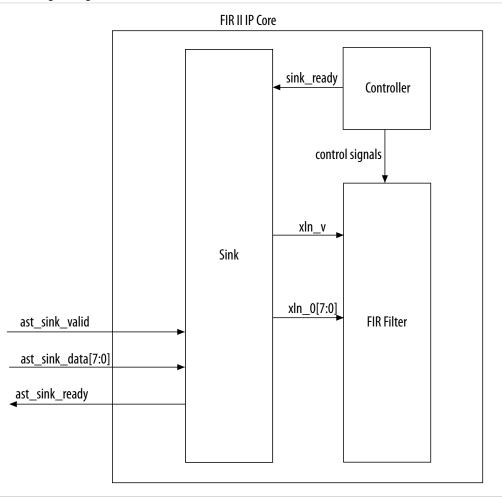

| FIR II IP Core Interfaces and Signals |     |

| Avalon-ST Interfaces in DSP IP Cores  |     |

| FIR II IP Core Avalon-ST Interfaces   |     |

| FIR II IP Core Signals                |     |

|                                       | - 1 |

| Document Revision History             |     |

|                                       |     |

| FIR II IP Core Document Archive       | A-1 |

|                                       |     |

# About the FIR II IP Core

# 2016.05.01 UG-01072 Subscribe Send Feedback

The Altera<sup>®</sup> FIR II IP core provides a fully-integrated finite impulse response (FIR) filter function optimized for use with Altera FPGA devices. The II IP core has an interactive parameter editor that allows you to easily create custom FIR filters. The parameter editor outputs IP functional simulation model files for use with Verilog HDL and VHDL simulators.

You can use the parameter editor to implement a variety of filter types, including single rate, decimation, interpolation, and fractional rate filters.

Many digital systems use signal filtering to remove unwanted noise, to provide spectral shaping, or to perform signal detection or analysis. FIR filters and infinite impulse response (IIR) filters provide these functions. Typical filter applications include signal preconditioning, band selection, and low-pass filtering.

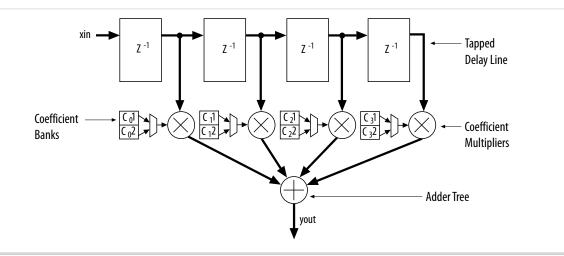

#### Figure 1-1: Basic FIR Filter with Weighted Tapped Delay Line

To design a filter, identify coefficients that match the frequency response you specify for the system. These coefficients determine the response of the filter. You can change which signal frequencies pass through the filter by changing the coefficient values in the parameter editor.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

#### 1-2 Altera DSP IP Core Features

#### **Related Information**

- Introduction to Altera IP Cores Provides general information about all Altera IP cores, including parameterizing, generating, upgrading, and simulating IP.

- Creating Version-Independent IP and Qsys Simulation Scripts Create simulation scripts that do not require manual updates for software or IP version upgrades.

- **Project Management Best Practices** Guidelines for efficient management and portability of your project and IP files.

### Altera DSP IP Core Features

- Avalon<sup>®</sup> Streaming (Avalon-ST) interfaces

- DSP Builder ready

- Testbenches to verify the IP core

- IP functional simulation models for use in Altera-supported VHDL and Verilog HDL simulators

### **FIR II IP Core Features**

- Exploiting maximal designs efficiency through hardware optimizations such as:

- Interpolation

- Decimation

- Symmetry

- Decimation half-band

- Time sharing

- Easy system integration using Avalon Streaming (Avalon-ST) interfaces.

- Memory and multiplier trade-offs to balance the implementation between logic elements (LEs) and memory blocks (M512, M4K, M9K, M10K, M20K, or M144K).

- Support for run-time coefficient reloading capability and multiple coefficient banks.

- User-selectable output precision via truncation, saturation, and rounding.

### **DSP IP Core Device Family Support**

Altera offers the following device support levels for Altera IP cores:

- Preliminary support—Altera verifies the IP core with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. You can use it in production designs with caution.

- Final support—Altera verifies the IP core with final timing models for this device family. The IP core meets all functional and timing requirements for the device family. You can use it in production designs.

About the FIR II IP Core

#### Table 1-1: DSP IP Core Device Family Support

| Device Family              | Support    |

|----------------------------|------------|

| Arria <sup>®</sup> II GX   | Final      |

| Arria II GZ                | Final      |

| Arria V                    | Final      |

| Arria 10                   | Final      |

| Cyclone <sup>®</sup> IV    | Final      |

| Cyclone V                  | Final      |

| MAX <sup>®</sup> 10 FPGA   | Final      |

| Stratix <sup>®</sup> IV GT | Final      |

| Stratix IV GX/E            | Final      |

| Stratix V                  | Final      |

| Other device families      | No support |

### **DSP IP Core Verification**

Before releasing a version of an IP core, Altera runs comprehensive regression tests to verify its quality and correctness. Altera generates custom variations of the IP core to exercise the various parameter options and thoroughly simulates the resulting simulation models with the results verified against master simulation models.

### **FIR II IP Core Release Information**

Use the release information when licensing the IP core.

#### Table 1-2: Release Information

| Item          | Description |

|---------------|-------------|

| Version       | 16.0        |

| Release Date  | May 2016    |

| Ordering Code | IP-FIRII    |

| Product ID    | 00D8        |

| Vendor ID     | 6AF7        |

Altera verifies that the current version of the Quartus Prime software compiles the previous version of each IP core. Altera does not verify that the Quartus Prime software compiles IP core versions older than the previous version. The *Altera IP Release Notes* lists any exceptions.

#### **Related Information**

• Altera IP Release Notes

About the FIR II IP Core

1-4

• Errata for FIR II IP core in the Knowledge Base

### FIR II IP Core Performance and Resource Utilization

#### Table 1-3: FIR II IP Core Performance—Arria V Devices

| Typical ever | acted performanc | e using the Quarty | s Drime coftware | with Arria V | (5AGXFB3H4F40C4). |

|--------------|------------------|--------------------|------------------|--------------|-------------------|

| i ypicai exp | ecteu periormane | e using the Quarte | is Finne sonware | with Allia v | (JAGAFDJ14F40C4). |

|         | Pa    | arameters          |                             | ALM   | DSP    | Men  | nory | Re      | gisters   | f <sub>MAX</sub> |

|---------|-------|--------------------|-----------------------------|-------|--------|------|------|---------|-----------|------------------|

| Channel | Wires | Filter Type        | Coefficients                | ALM   | Blocks | M10K | M20K | Primary | Secondary | (MHz)            |

| 8       | 2     | Decimation         | _                           | 1,607 | 24     | 0    |      | 1,232   | 64        | 30<br>8          |

| 8       | 2     | Decimation         | Write                       | 2,120 | 24     | 0    | —    | 1,298   | 141       | 30<br>8          |

| 8       | 2     | Fractional<br>Rate | _                           | 1,395 | 16     | 0    | _    | 2,074   | 99        | 28<br>1          |

| 8       | 2     | Fractional<br>Rate | Write                       | 1,745 | 16     | 0    | —    | 2,171   | 91        | 28<br>2          |

| 8       | 2     | Fractional<br>Rate | —                           | 1,493 | 16     | 0    |      | 2,167   | 117       | 28<br>0          |

| 8       | 2     | Fractional<br>Rate | Write                       | 1,852 | 16     | 0    | —    | 2,287   | 116       | 27<br>0          |

| 8       | 2     | Interpolation      | —                           | 1,841 | 32     | 0    | _    | 2,429   | 52        | 28<br>2          |

| 8       | 2     | Interpolation      | Write                       | 1,994 | 32     | 0    |      | 2,826   | 41        | 27<br>8          |

| 8       | 2     | Interpolation      | Multiple<br>banks           | 2,001 | 32     | 0    |      | 2,737   | 74        | 27<br>9          |

| 8       | 2     | Interpolation      | Multiple<br>banks;<br>Write | 2,700 | 32     | 0    |      | 2,972   | 130       | 28<br>2          |

| 8       | 2     | Single rate        | _                           | 932   | 20     | 0    | _    | 318     | 20        | 27<br>8          |

| 8       | 2     | Single rate        | Write                       | 1,057 | 20     | 0    | _    | 713     | 3         | 27<br>9          |

| 8       | 1     | Decimation         | —                           | 329   | 3      | 1    |      | 321     | 33        | 30<br>1          |

| 8       | 1     | Decimation         | Write                       | 430   | 3      | 1    | —    | 366     | 34        | 30<br>7          |

| 8       | 1     | Decimation         | Multiple<br>banks           | 395   | 3      | 3    |      | 483     | 44        | 31<br>0          |

About the FIR II IP Core

|                   | Pa    | arameters          |                             |     | DSP    | Memory |      | Registers |           | f <sub>MAX</sub> |

|-------------------|-------|--------------------|-----------------------------|-----|--------|--------|------|-----------|-----------|------------------|

| Channel           | Wires | Filter Type        | Coefficients                | ALM | Blocks | M10K   | M20K | Primary   | Secondary | (MHz)            |

| 8                 | 1     | Decimation         | Multiple<br>banks;<br>Write | 510 | 3      | 3      |      | 472       | 40        | 29<br>1          |

| 8                 | 1     | Fractional<br>Rate | _                           | 661 | 5      | 4      |      | 877       | 75        | 31<br>0          |

| 8                 | 1     | Fractional<br>Rate | Write                       | 788 | 5      | 4      | —    | 936       | 98        | 30<br>9          |

| 8                 | 1     | Interpolation      | _                           | 381 | 5      | 0      | _    | 442       | 32        | 27<br>8          |

| 8                 | 1     | Interpolation      | Write                       | 514 | 5      | 0      | _    | 540       | 27        | 27<br>8          |

| 8                 | 1     | Single Rate        | _                           | 493 | 10     | 0      | _    | 191       | 20        | 27<br>8          |

| 8                 | 1     | Single Rate        | Write                       | 633 | 10     | 0      | _    | 588       | 1         | 27<br>8          |

| 1                 | _     | Decimation         | _                           | 220 | 3      | 0      | _    | 158       | 27        | 31<br>0          |

| 1 super<br>sample | _     | Decimation         | —                           | 404 | 20     | 0      | _    | 400       | 41        | 30<br>5          |

| 1 super<br>sample | _     | Decimation         | Write                       | 505 | 20     | 0      | _    | 785       | 35        | 30<br>8          |

| 1                 | _     | Decimation         | Write                       | 318 | 3      | 0      | _    | 208       | 26        | 30<br>9          |

| 1 Half<br>Band    | _     | Decimation         | _                           | 234 | 3      | 0      | _    | 192       | 34        | 30<br>8          |

| 1 Half<br>Band    | _     | Decimation         | Write                       | 320 | 3      | 0      |      | 232       | 27        | 30<br>9          |

| 1                 | _     | Fractional<br>Rate | —                           | 297 | 3      | 0      |      | 504       | 57        | 31<br>0          |

| 1                 | _     | Fractional<br>Rate | Write                       | 391 | 3      | 0      |      | 563       | 56        | 31<br>0          |

| 1 Half<br>Band    | _     | Fractional<br>Rate |                             | 196 | 2      | 0      | _    | 251       | 5         | 27<br>7          |

| 1 Half<br>Band    | _     | Fractional<br>Rate | Write                       | 266 | 2      | 0      | _    | 301       | 15        | 28<br>0          |

| 1                 | _     | Interpolation      | —                           | 266 | 5      | 0      | _    | 290       | 30        | 27<br>8          |

About the FIR II IP Core

**Altera Corporation**

#### 1-6 FIR II IP Core Performance and Resource Utilization

|                   | Ра    | arameters     |                             | ALM | DSP    | Men  | nory | Re      | gisters   | f <sub>MAX</sub> |

|-------------------|-------|---------------|-----------------------------|-----|--------|------|------|---------|-----------|------------------|

| Channel           | Wires | Filter Type   | Coefficients                | ALM | Blocks | M10K | M20K | Primary | Secondary | (MHz)            |

| 1 super<br>sample | -     | Interpolation | —                           | 717 | 32     | 0    | —    | 903     | 45        | 30<br>8          |

| 1 super<br>sample | _     | Interpolation | Write                       | 842 | 32     | 0    | —    | 1,281   | 48        | 30<br>8          |

| 1                 | _     | Interpolation | Write                       | 405 | 5      | 0    | _    | 380     | 15        | 27<br>8          |

| 1 Half<br>Band    | _     | Interpolation | _                           | 254 | 3      | 0    |      | 293     | 8         | 31<br>0          |

| 1 Half<br>Band    | —     | Interpolation | Write                       | 333 | 4      | 0    | —    | 314     | 10        | 30<br>9          |

| 1                 | _     | Single rate   | _                           | 93  | 10     | 0    | _    | 129     | 27        | 29<br>9          |

| 1 super<br>sample | _     | Single rate   | —                           | 262 | 20     | 0    | _    | 307     | 41        | 30<br>9          |

| 1 super<br>sample | _     | Single rate   | Write                       | 373 | 20     | 0    | _    | 687     | 40        | 30<br>2          |

| 1                 | _     | Single rate   | Write                       | 228 | 10     | 0    |      | 519     | 16        | 30<br>0          |

| 1 Half<br>Band    | _     | Single rate   | —                           | 189 | 5      | 0    | _    | 254     | 63        | 30<br>9          |

| 1 Half<br>Band    | _     | Single rate   | Write                       | 272 | 5      | 0    | _    | 496     | 29        | 31<br>0          |

| 1                 | _     | Single rate   | Multiple<br>banks           | 109 | 10     | 0    | _    | 199     | 29        | 28<br>3          |

| 1                 | _     | Single rate   | Multiple<br>banks;<br>Write | 395 | 10     | 0    | —    | 361     | 19        | 28<br>2          |

#### Table 1-4: FIR II IP Core Performance—Cyclone V Devices

Typical expected performance using the Quartus Prime software with Cyclone V (5CGXFC7D6F31C6) devices.

|         | Ра    | arameters   |              | ALM   |        | A I M | DSP  | Men     | nory      | Re      | gisters | f <sub>MAX</sub> |

|---------|-------|-------------|--------------|-------|--------|-------|------|---------|-----------|---------|---------|------------------|

| Channel | Wires | Filter Type | Coefficients |       | Blocks | M10K  | M20K | Primary | Secondary | (MHz)   |         |                  |

| 8       | 2     | Decimation  | —            | 1,607 | 24     | 0     | _    | 1,231   | 46        | 27<br>3 |         |                  |

| 8       | 2     | Decimation  | Write        | 2,092 | 24     | 0     | _    | 1,352   | 63        | 27<br>3 |         |                  |

About the FIR II IP Core

|         | Ра    | arameters          |                             | ALM   | DSP    | Men  | nory | Re      | gisters   | f <sub>MAX</sub> |

|---------|-------|--------------------|-----------------------------|-------|--------|------|------|---------|-----------|------------------|

| Channel | Wires | Filter Type        | Coefficients                | ALM   | Blocks | M10K | M20K | Primary | Secondary | (MHz)            |

| 8       | 2     | Fractional<br>Rate | _                           | 1,852 | 16     | 0    | _    | 3,551   | 309       | 25<br>4          |

| 8       | 2     | Fractional<br>Rate | Write                       | 2,203 | 16     | 0    | _    | 3,675   | 269       | 25<br>5          |

| 8       | 2     | Fractional<br>Rate | _                           | 1,951 | 16     | 0    | _    | 3,543   | 421       | 22<br>7          |

| 8       | 2     | Fractional<br>Rate | Write                       | 2,301 | 16     | 0    | _    | 3,601   | 476       | 25<br>0          |

| 8       | 2     | Interpolation      | _                           | 1,840 | 32     | 0    |      | 2,431   | 48        | 25<br>5          |

| 8       | 2     | Interpolation      | Write                       | 1,988 | 32     | 0    |      | 2,813   | 57        | 25<br>2          |

| 8       | 2     | Interpolation      | Multiple<br>banks           | 2,006 | 32     | 0    | _    | 2,711   | 98        | 25<br>3          |

| 8       | 2     | Interpolation      | Multiple<br>banks;<br>Write | 2,704 | 32     | 0    |      | 2,990   | 100       | 25<br>0          |

| 8       | 2     | Single rate        | _                           | 934   | 20     | 0    |      | 317     | 19        | 25<br>2          |

| 8       | 2     | Single rate        | Write                       | 1,053 | 20     | 0    | _    | 704     | 12        | 25<br>1          |

| 8       | 1     | Decimation         | —                           | 474   | 3      | 1    | _    | 541     | 50        | 27<br>5          |

| 8       | 1     | Decimation         | Write                       | 559   | 3      | 1    | —    | 574     | 58        | 27<br>3          |

| 8       | 1     | Decimation         | Multiple<br>banks           | 544   | 3      | 3    |      | 691     | 83        | 27<br>5          |

| 8       | 1     | Decimation         | Multiple<br>banks;<br>Write | 636   | 3      | 3    |      | 677     | 82        | 27<br>5          |

| 8       | 1     | Fractional<br>Rate | —                           | 1,165 | 5      | 4    |      | 1,715   | 205       | 27<br>5          |

| 8       | 1     | Fractional<br>Rate | Write                       | 1,287 | 5      | 4    | —    | 1,770   | 198       | 27<br>5          |

| 8       | 1     | Interpolation      | —                           | 381   | 5      | 0    | _    | 433     | 42        | 24<br>8          |

**Altera Corporation**

|                   | Pa    | arameters          |              |     | DSP    | DSP Memory |   |         | Registers |                           |  |

|-------------------|-------|--------------------|--------------|-----|--------|------------|---|---------|-----------|---------------------------|--|

| Channel           | Wires | Filter Type        | Coefficients | ALM | Blocks | M10K       |   | Primary | Secondary | f <sub>MAX</sub><br>(MHz) |  |

| 8                 | 1     | Interpolation      | Write        | 513 | 5      | 0          | — | 540     | 26        | 25<br>0                   |  |

| 8                 | 1     | Single Rate        | _            | 493 | 10     | 0          |   | 191     | 18        | 24<br>9                   |  |

| 8                 | 1     | Single Rate        | Write        | 624 | 10     | 0          |   | 563     | 26        | 25<br>1                   |  |

| 1                 | —     | Decimation         | _            | 219 | 3      | 0          |   | 159     | 23        | 28<br>9                   |  |

| 1 super<br>sample | —     | Decimation         | —            | 404 | 20     | 0          | — | 398     | 43        | 28<br>8                   |  |

| 1 super<br>sample | —     | Decimation         | Write        | 503 | 20     | 0          |   | 774     | 46        | 25<br>6                   |  |

| 1                 | -     | Decimation         | Write        | 312 | 3      | 0          | — | 208     | 26        | 28<br>9                   |  |

| 1 Half<br>Band    | _     | Decimation         | _            | 234 | 3      | 0          | _ | 192     | 29        | 28<br>9                   |  |

| 1 Half<br>Band    | -     | Decimation         | Write        | 323 | 3      | 0          | _ | 228     | 32        | 28<br>8                   |  |

| 1                 | _     | Fractional<br>Rate | _            | 422 | 3      | 0          | _ | 723     | 94        | 31<br>0                   |  |

| 1                 | -     | Fractional<br>Rate | Write        | 516 | 3      | 0          | _ | 787     | 86        | 29<br>2                   |  |

| 1 Half<br>Band    | _     | Fractional<br>Rate | _            | 195 | 2      | 0          |   | 251     | 12        | 26<br>1                   |  |

| 1 Half<br>Band    | -     | Fractional<br>Rate | Write        | 267 | 2      | 0          | — | 299     | 15        | 25<br>2                   |  |

| 1                 | -     | Interpolation      | _            | 262 | 5      | 0          | _ | 296     | 25        | 25<br>2                   |  |

| 1 super<br>sample | -     | Interpolation      | _            | 708 | 32     | 0          | _ | 914     | 34        | 27<br>2                   |  |

| 1 super<br>sample | _     | Interpolation      | Write        | 841 | 32     | 0          |   | 1,297   | 32        | 25<br>9                   |  |

| 1                 | -     | Interpolation      | Write        | 400 | 5      | 0          |   | 382     | 12        | 25<br>8                   |  |

| 1 Half<br>Band    | _     | Interpolation      | —            | 288 | 3      | 0          |   | 456     | 13        | 29<br>0                   |  |

About the FIR II IP Core

| - | _  |

|---|----|

| 1 | -Q |

|   | -  |

|                   | Parameters |               | ALM                         | DSP |        | Memory |      | Registers |           |         |

|-------------------|------------|---------------|-----------------------------|-----|--------|--------|------|-----------|-----------|---------|

| Channel           | Wires      | Filter Type   | Coefficients                | ALM | Blocks | M10K   | M20K | Primary   | Secondary | (MHz)   |

| 1 Half<br>Band    | -          | Interpolation | Write                       | 331 | 4      | 0      | _    | 315       | 9         | 29<br>0 |

| 1                 | _          | Single rate   | _                           | 87  | 10     | 0      |      | 142       | 14        | 25<br>3 |

| 1 super<br>sample | —          | Single rate   | _                           | 258 | 20     | 0      |      | 315       | 33        | 26<br>0 |

| 1 super<br>sample | _          | Single rate   | Write                       | 369 | 20     | 0      |      | 704       | 23        | 27<br>4 |

| 1                 | _          | Single rate   | Write                       | 227 | 10     | 0      |      | 535       | 0         | 25<br>1 |

| 1 Half<br>Band    | _          | Single rate   | _                           | 187 | 5      | 0      |      | 273       | 44        | 28<br>8 |

| 1 Half<br>Band    | _          | Single rate   | Write                       | 274 | 5      | 0      |      | 506       | 19        | 27<br>5 |

| 1                 | _          | Single rate   | Multiple<br>banks           | 110 | 10     | 0      |      | 187       | 41        | 25<br>5 |

| 1                 |            | Single rate   | Multiple<br>banks;<br>Write | 375 | 10     | 0      | _    | 349       | 32        | 25<br>5 |

#### Table 1-5: FIR II IP Core Performance—Stratix V Devices

| Typical expected p | erformance using the | <b>Ouartus</b> Prime software with | Stratix V (5SGSMD4H2F35C2) devices. |

|--------------------|----------------------|------------------------------------|-------------------------------------|

|                    |                      |                                    |                                     |

| Parameters |       | ALM DSP            |              | Memory |        | Registers |      | f <sub>MAX</sub> |           |         |

|------------|-------|--------------------|--------------|--------|--------|-----------|------|------------------|-----------|---------|

| Channel    | Wires | Filter Type        | Coefficients |        | Blocks | M10K      | M20K | Primary          | Secondary | (MHz)   |

| 8          | 2     | Decimation         | _            | 1,609  | 24     |           | 0    | 1,231            | 60        | 45<br>0 |

| 8          | 2     | Decimation         | Write        | 2,319  | 24     | —         | 0    | 2,077            | 66        | 45<br>0 |

| 8          | 2     | Fractional<br>Rate | _            | 1,350  | 16     |           | 0    | 2,099            | 88        | 44<br>8 |

| 8          | 2     | Fractional<br>Rate | Write        | 1,771  | 16     |           | 0    | 2,291            | 78        | 45<br>0 |

| 8          | 2     | Fractional<br>Rate | -            | 1,457  | 16     |           | 0    | 2,213            | 88        | 44<br>4 |

| 8          | 2     | Fractional<br>Rate | Write        | 1,873  | 16     | —         | 0    | 2,418            | 89        | 45<br>0 |

About the FIR II IP Core

#### 1-10 FIR II IP Core Performance and Resource Utilization

| _       |         |                    |                             |       |        |      |      |           |           | 2010.05.0        |

|---------|---------|--------------------|-----------------------------|-------|--------|------|------|-----------|-----------|------------------|

|         | P       | arameters          |                             | ALM   | DSP    |      | nory | Registers |           | f <sub>MAX</sub> |

| Channel | l Wires | Filter Type        | Coefficients                |       | Blocks | M10K | M20K | Primary   | Secondary | (MHz)            |

| 8       | 2       | Interpolation      | _                           | 1,777 | 32     | _    | 0    | 2,303     | 15        | 44<br>4          |

| 8       | 2       | Interpolation      | Write                       | 2,081 | 32     | —    | 0    | 3,009     | 26        | 45<br>0          |

| 8       | 2       | Interpolation      | Multiple<br>banks           | 1,825 | 32     | —    | 0    | 2,473     | 39        | 43<br>0          |

| 8       | 2       | Interpolation      | Multiple<br>banks;<br>Write | 2,652 | 32     |      | 0    | 2,842     | 236       | 42<br>4          |

| 8       | 2       | Single rate        | _                           | 920   | 20     | —    | 0    | 332       | 2         | 44<br>4          |

| 8       | 2       | Single rate        | Write                       | 1,359 | 20     | -    | 0    | 1,323     | 1         | 45<br>0          |

| 8       | 1       | Decimation         | _                           | 340   | 3      | _    | 0    | 324       | 25        | 45<br>0          |

| 8       | 1       | Decimation         | Write                       | 463   | 3      | -    | 0    | 457       | 29        | 45<br>0          |

| 8       | 1       | Decimation         | Multiple<br>banks           | 466   | 3      | -    | 0    | 569       | 42        | 45<br>0          |

| 8       | 1       | Decimation         | Multiple<br>banks;<br>Write | 577   | 3      | _    | 0    | 567       | 41        | 45<br>0          |

| 8       | 1       | Fractional<br>Rate | _                           | 709   | 5      | -    | 0    | 870       | 45        | 45<br>0          |

| 8       | 1       | Fractional<br>Rate | Write                       | 852   | 5      | -    | 0    | 991       | 65        | 45<br>0          |

| 8       | 1       | Interpolation      | _                           | 216   | 5      | -    | 0    | 197       | 13        | 45<br>0          |

| 8       | 1       | Interpolation      | Write                       | 361   | 5      | -    | 0    | 290       | 22        | 45<br>0          |

| 8       | 1       | Single Rate        | _                           | 483   | 10     | -    | 0    | 212       | 4         | 44<br>7          |

| 8       | 1       | Single Rate        | Write                       | 783   | 10     | —    | 0    | 894       | 4         | 45<br>0          |

| 1       | -       | Decimation         | —                           | 215   | 3      | —    | 0    | 175       | 10        | 45<br>0          |

About the FIR II IP Core

1-11

|                   | Ра    | arameters          |              | 01.04 | DSP    | Men  | nory | Re      | gisters   | f <sub>MAX</sub> |

|-------------------|-------|--------------------|--------------|-------|--------|------|------|---------|-----------|------------------|

| Channel           | Wires | Filter Type        | Coefficients | ALM   | Blocks | M10K | M20K | Primary | Secondary | (MHz)            |

| 1 super<br>sample | _     | Decimation         | _            | 547   | 20     | _    | 0    | 1,167   | 88        | 45<br>0          |

| 1 super<br>sample | _     | Decimation         | Write        | 989   | 20     | _    | 0    | 2,214   | 105       | 45<br>0          |

| 1                 | _     | Decimation         | Write        | 331   | 3      |      | 0    | 310     | 7         | 45<br>0          |

| 1 Half<br>Band    |       | Decimation         | —            | 226   | 3      |      | 0    | 206     | 16        | 45<br>0          |

| 1 Half<br>Band    |       | Decimation         | Write        | 343   | 3      |      | 0    | 327     | 18        | 45<br>0          |

| 1                 | _     | Fractional<br>Rate | _            | 252   | 3      | _    | 0    | 318     | 21        | 44<br>5          |

| 1                 |       | Fractional<br>Rate | Write        | 353   | 3      |      | 0    | 380     | 13        | 45<br>0          |

| 1 Half<br>Band    |       | Fractional<br>Rate | _            | 140   | 2      |      | 0    | 185     | 13        | 45<br>0          |

| 1 Half<br>Band    | _     | Fractional<br>Rate | Write        | 214   | 2      | _    | 0    | 235     | 21        | 45<br>0          |

| 1                 | _     | Interpolation      | _            | 168   | 5      | _    | 0    | 127     | 19        | 45<br>0          |

| 1 super<br>sample |       | Interpolation      | —            | 573   | 32     |      | 0    | 1,084   | 51        | 44<br>6          |

| 1 super<br>sample |       | Interpolation      | Write        | 870   | 32     |      | 0    | 1,774   | 136       | 45<br>0          |

| 1                 | _     | Interpolation      | Write        | 313   | 5      |      | 0    | 196     | 5         | 45<br>0          |

| 1 Half<br>Band    | _     | Interpolation      | _            | 253   | 3      | _    | 0    | 292     | 9         | 45<br>0          |

| 1 Half<br>Band    | —     | Interpolation      | Write        | 370   | 4      | —    | 0    | 418     | 9         | 45<br>0          |

| 1                 | _     | Single rate        | _            | 226   | 10     | _    | 0    | 706     | 31        | 44<br>7          |

| 1 _<br>ssample    | —     | Single rate        | —            | 468   | 20     | —    | 0    | 1,354   | 53        | 45<br>0          |

| 1 _<br>ssample    | _     | Single rate        | Write        | 927   | 20     | _    | 0    | 2,267   | 203       | 45<br>0          |

About the FIR II IP Core

**Altera Corporation**

#### 1-12 FIR II IP Core Performance and Resource Utilization

| Parameters     |       | ALM         | DSP                         | DSP Mer |        | Re   | Registers |         |           |                           |

|----------------|-------|-------------|-----------------------------|---------|--------|------|-----------|---------|-----------|---------------------------|

| Channel        | Wires | Filter Type | Coefficients                | ALM     | Blocks | M10K | M20K      | Primary | Secondary | f <sub>MAX</sub><br>(MHz) |

| 1              | _     | Single rate | Write                       | 524     | 10     | -    | 0         | 1,391   | 31        | 50<br>0                   |

| 1 Half<br>Band | _     | Single rate | _                           | 195     | 5      | _    | 0         | 270     | 50        | 45<br>0                   |

| 1 Half<br>Band | _     | Single rate | Write                       | 351     | 5      | _    | 0         | 645     | 28        | 45<br>0                   |

| 1              | _     | Single rate | Multiple<br>banks           | 250     | 10     | _    | 0         | 716     | 93        | 44<br>9                   |

| 1              | _     | Single rate | Multiple<br>banks;<br>Write | 671     | 10     |      | 0         | 1,228   | 50        | 45<br>0                   |

About the FIR II IP Core

## FIR II IP Core Getting Started

### **Licensing IP Cores**

The Altera IP Library provides many useful IP core functions for your production use without purchasing an additional license. Some Altera MegaCore<sup>®</sup> IP functions require that you purchase a separate license for production use. However, the OpenCore<sup>®</sup> feature allows evaluation of any Altera IP core in simulation and compilation in the Quartus<sup>®</sup> Prime software. After you are satisfied with functionality and performance, visit the Self Service Licensing Center to obtain a license number for any Altera product.

#### Figure 2-1: IP Core Installation Path

*C* <*IP core name* > - Contains the IP core source files

**Note:** The default IP installation directory on Windows is *drive*:*lalteraversion number*; on Linux the IP installation directory is *<i>chome directorylalteraversion number*.

#### **OpenCore Plus IP Evaluation**

Altera's free OpenCore Plus feature allows you to evaluate licensed MegaCore IP cores in simulation and hardware before purchase. You only need to purchase a license for MegaCore IP cores if you decide to take your design to production. OpenCore Plus supports the following evaluations:

- Simulate the behavior of a licensed IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

OpenCore Plus evaluation supports the following two operation modes:

- Untethered—run the design containing the licensed IP for a limited time.

- Tethered—run the design containing the licensed IP for a longer time or indefinitely. This requires a connection between your board and the host computer.

ISO 9001:2008 Registered

part of Inte

<sup>© 2016</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

#### 2-2 FIR II IP Core OpenCore Plus Timeout Behavior

Note: All IP cores that use OpenCore Plus time out simultaneously when any IP core in the design times out.

#### **Related Information**

- Altera Licensing Site

- Altera Software Installation and Licensing Manual

#### FIR II IP Core OpenCore Plus Timeout Behavior

All IP cores in a device time out simultaneously when the most restrictive evaluation time is reached. If a design has more than one IP core, the time-out behavior of the other IP cores may mask the time-out behavior of a specific IP core .

For IP cores, the untethered time-out is 1 hour; the tethered time-out value is indefinite. Your design stops working after the hardware evaluation time expires. The Quartus Prime software uses OpenCore Plus Files (**.ocp**) in your project directory to identify your use of the OpenCore Plus evaluation program. After you activate the feature, do not delete these files..

When the evaluation time expires, the ast\_source\_data signal goes low.

#### **Related Information**

AN 320: OpenCore Plus Evaluation of Megafunctions

#### **IP Catalog and Parameter Editor**

The IP Catalog displays the installed IP cores available for your design. Double-click any IP core to launch the parameter editor and generate files representing your IP variation. Use the following features to help you quickly locate and select an IP core:

- Filter IP Catalog to Show IP for active device family or Show IP for all device families. If you have no project open, select the Device Family in IP Catalog.

- Type in the Search field to locate any full or partial IP core name in IP Catalog.

- Right-click an IP core name in IP Catalog to display details about supported devices, open the IP core's installation folder, and click links to IP documentation.

- Click Search for Partner IP, to access partner IP information on the Altera website.

The parameter editor prompts you to specify an IP variation name, optional ports, and output file generation options. The parameter editor generates a top-level Qsys system file (**.qsys**) or Quartus Prime IP file (**.qip**) representing the IP core in your project. You can also parameterize an IP variation without an open project.

The IP Catalog is also available in Qsys (**View** > **IP Catalog**). The Qsys IP Catalog includes exclusive system interconnect, video and image processing, and other system-level IP that are not available in the Quartus Prime IP Catalog. For more information about using the Qsys IP Catalog, refer to *Creating a System with Qsys* in Volume 1 of the *Quartus Prime Handbook*.

#### Related Information Creating a System with Qsys

**FIR II IP Core Getting Started**

2-3

### **Generating IP Cores**

You can quickly configure a custom IP variation in the parameter editor. Use the following steps to specify IP core options and parameters in the parameter editor:

#### Figure 2-2: IP Parameter Editor

| 👗 IP Parameter Editor - unsaved.gsyst (/users/jbrossar/150_migrate_upgrade_test/uns                                  | saved.gsys) <@sj-slscf2680-02>                                                                                  |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Eile Edit System Generate View Tools Help                                                                            |                                                                                                                 |

| 🚑 Parameters 🛛 🗕 🗖 🗖                                                                                                 | Details 🕸 Block Symbol 🕸 _ 🗃 🛃 and parameter                                                                    |

| System: unsaved Path: xcvr_fpll_a10_0                                                                                | details                                                                                                         |

| Arria 10 fPLL<br>altera_xcvr_fpll_a10                                                                                | Arria 10 fPLL                                                                                                   |

| Dynamic Reconfiguration Generation Options Advanced Parameters                                                       | Name altera_xcvr_fpll_a10                                                                                       |

| PLL Master Clock Generation Block                                                                                    | Version 15.1                                                                                                    |

| T General                                                                                                            | Author Altera Corporation                                                                                       |

| FPLL Mode: Transceiver                                                                                               | Description Arria 10 FPLL.                                                                                      |

|                                                                                                                      | Group Interface Protocols/Tran                                                                                  |

| Dasit                                                                                                                | Data Sheet <u>http://www.altera.com/li</u>                                                                      |

| Enable fractional mode                                                                                               | User Guide https://documentation.a                                                                              |

| Enable manual counter configuration                                                                                  | Release Notes https://documentation.a                                                                           |

| Enable ATX to FPLL cascade clock input port                                                                          |                                                                                                                 |

| * Reference Clock                                                                                                    | S                                                                                                               |

| Desired reference clock frequency: 100.0 MHz                                                                         | of Presets 🕴 🗕 🗖 🗖                                                                                              |

| Actual reference clock frequency. 100.0 VMHz                                                                         |                                                                                                                 |

| Number of PL Area New IP Variation <@sj-slscf2680-02> Selected rater Your IP settings will be saved in a .qsys file. | C X 6 for xcvr_fpll_a10_0                                                                                       |

| Selected refer                                                                                                       |                                                                                                                 |

| Create IP Variation                                                                                                  | k New to create a preset.                                                                                       |

| Bandwidth: Entity name: unnamed                                                                                      | GX 2500Mbps Bonded                                                                                              |

| Save in folder: /users/jbrossar/150_migrate_upgrade_test                                                             | GX 2500Mbps Single Channel                                                                                      |

| Target Device                                                                                                        | GX 2500Mbps xN Non-Bonded                                                                                       |

|                                                                                                                      | PCIe Gen1 and Gen2 Multi Lane 100Mhz                                                                            |

| Type Family. Arria 10                                                                                                | PCle Gen1 and Gen2 Single Lane 100Mhz                                                                           |

| Device: 10AS016C3U19E2LG                                                                                             |                                                                                                                 |

| Info: Your IP will be saved in /users/jbrossar/150_migrate_upgrade_test/unname                                       | d.qsys                                                                                                          |

|                                                                                                                      |                                                                                                                 |

|                                                                                                                      | ly Update Delete New                                                                                            |

|                                                                                                                      | OK Concrete HDI Finish                                                                                          |

| 0 Errors, 0 Warn                                                                                                     | Generate HDL Finish                                                                                             |

|                                                                                                                      | i de la companya de l |

| Specify your IP variation name App                                                                                   | ply preset parameters for                                                                                       |

|                                                                                                                      |                                                                                                                 |

| and target device spe                                                                                                | cific applications                                                                                              |

- In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core to customize. The parameter editor appears.

- Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named *your\_ip>.qsys*. Click OK. Do not include spaces in IP variation names or paths.

- **3.** Specify the parameters and options for your IP variation in the parameter editor, including one or more of the following:

- Optionally select preset parameter values if provided for your IP core. Presets specify initial parameter values for specific applications.

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for processing the IP core files in other EDA tools.

Note: Refer to your IP core user guide for information about specific IP core parameters.

- 4. Click Generate HDL. The Generation dialog box appears.

- **5.** Specify output file generation options, and then click **Generate**. The IP variation files synthesis and/or simulation files generate according to your specifications.

- **6.** To generate a simulation testbench, click **Generate** > **Generate Testbench System**. Specify testbench generation options, and then click **Generate**.

- 7. To generate an HDL instantiation template that you can copy and paste into your text editor, click **Generate** > **Show Instantiation Template**.

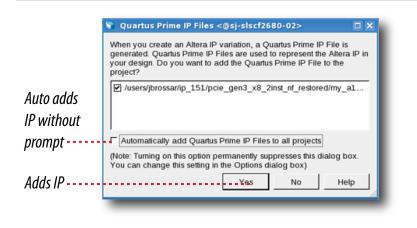

- 8. Click Finish. Click Yes if prompted to add files representing the IP variation to your project. Optionally turn on the option to Automatically add Quartus Prime IP Files to All Projects. Click Project > Add/Remove Files in Project to add IP files at any time.

#### Figure 2-3: Adding IP Files to Project

**Note:** For Arria 10 devices, the generated **.qsys** file must be added to your project to represent IP and Qsys systems. For devices released prior to Arria 10 devices, the generated **.qip** and **.sip** files must be added to your project for IP and Qsys systems.

The generated **.qsys** file must be added to your project to represent IP and Qsys systems.

- **9.** After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

- **Note:** Some IP cores generate different HDL implementations according to the IP core parameters. The underlying RTL of these IP cores contains a unique hash code that prevents module name collisions between different variations of the IP core. This unique code remains consistent, given the same IP settings and software version during IP generation. This unique code can change if you edit the IP core's parameters or upgrade the IP core version. To avoid dependency on these unique codes in your simulation environment, refer to *Generating a Combined Simulator Setup Script*.

**Altera Corporation**

FIR II IP Core Getting Started

#### **Related Information**

- IP User Guide Documentation

- Altera IP Release Notes

#### Files Generated for Altera IP Cores and Qsys Systems

The Quartus Prime software generates the following output file structure for IP cores and Qsys systems. The generated **.qsys** file must be added to your project to represent IP and Qsys systems. For devices released prior to Arria 10 devices, the generated **.qip** and **.sip** files must be added to your Quartus Prime Standard Edition project to represent IP and Qsys systems

#### Figure 2-4: Files generated for IP cores and Qsys Systems

| <project directory=""></project>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre> <your_ip>.qip or .qsys - System or IP integration file</your_ip></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <pre>— <pre>your_ip&gt; - IP core variation files</pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

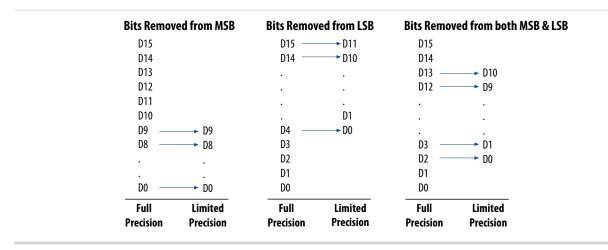

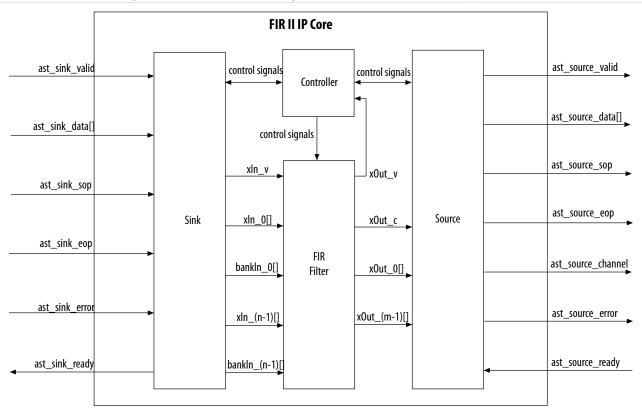

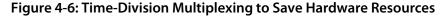

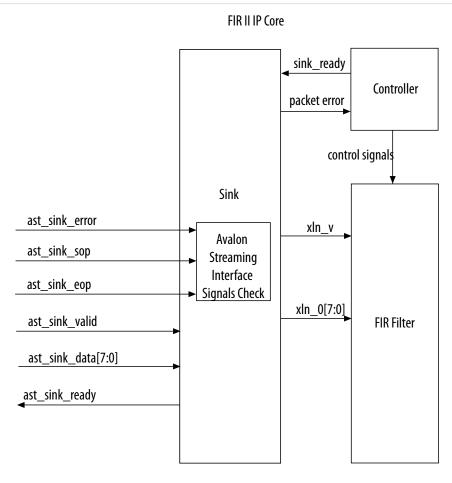

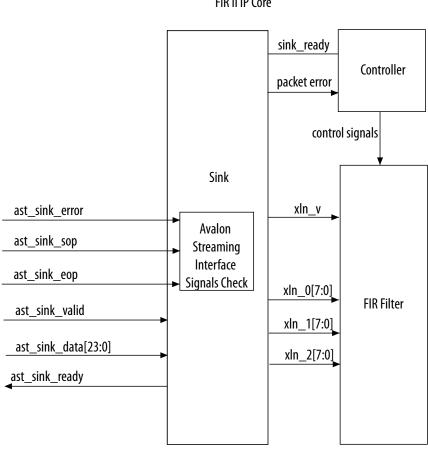

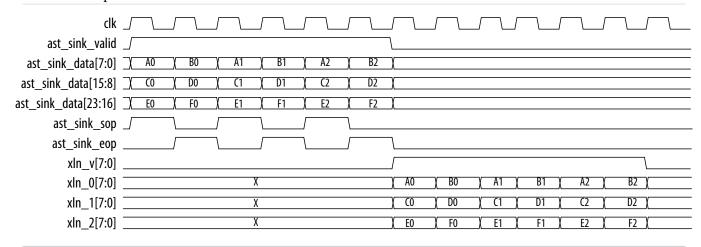

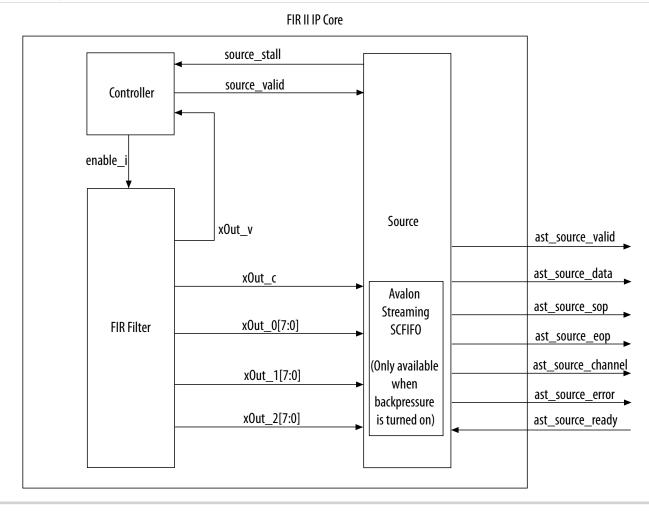

| <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |