Abstract:

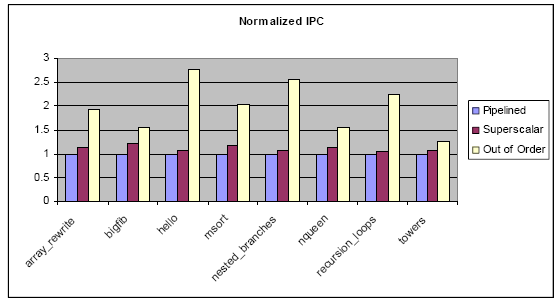

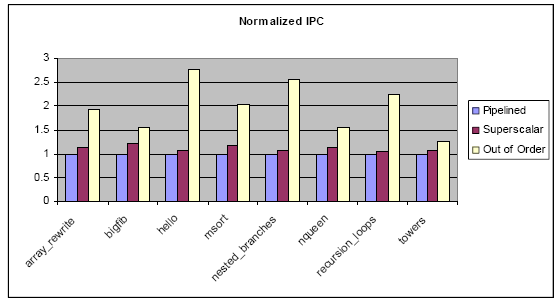

Microprocessors have evolved greatly over the past few decades from single cycle state

machines, to pipelined architectures, to wide issue superscalar processors to out of order

execution engines. This project implements one such out-of-order processor using the MIPS

instruction set architecture taught in ECE314 and ECE475. Because each of those classes

culminates in a microprocessor design in Verilog HDL, those implementations provide a good

performance baseline for comparison of this design. This microprocessor was designed to

exploit instruction level parallelism as much as possible while still maintaining reasonable

amount of logic per clock cycle. Ultimately the design implemented is capable of fetching,

decoding, renaming, issuing, executing, and retiring up to four instructions per clock cycle with

speculative execution; this results in a performance improvement of almost 3x over the two-way

superscalar MIPS processor implemented in ECE475. Upon successful implementation, the

processor was variably configured to try and gauge the effects of each component on

performance.