## ADAPTIVELY NETWORKED EXTENDABLE MULTIPROCESSOR ARCHITECTURE

A Design Project Report Presented to the Engineering Division of the Graduate School Cornell University in Partial Fulfillment of the Requirements of the Degree of Master of Engineering (Electrical)

> by Idan Beck Project Advisor: Bruce Land Degree Date: January 2008

#### Abstract

Master of Electrical Engineering Program Cornell University Design Project Report

#### **Project Title:**

Adaptively Network Extendible Multiprocessor Architecture

#### Author:

Idan Beck

#### Abstract:

This project consisted of the design of a fully integrated extendible multiprocessor architecture and system. This included the design of the compiler, assembler, linker, boot loader, and handshake interfacing protocols for peripheral modules which all may or may not lie on differing clock domains. The architecture is a single simple cycle RISC CPU with independent data and instruction memories such that it is as close to pure RISC as possible. The network layer works under the CPU transparently in a self-timed fashion utilizing a handshake. Network communication is solely based on instruction dispatching where each CPU is essentially capable of writing to another CPU's instruction memory. The network is also adaptive utilizing a unique register-thru design and message passing algorithm which allows each node on the network to behave either as a packet switched network or an evolved circuit switched network and a broadcast can be used to reset the network.

Report Approved by Project Advisor:\_\_\_\_\_ Date:\_\_\_\_\_

#### Executive Summary

This project aims to try and provide a new approach to multiprocessor systems, which are known to be hard to design as well as program. One of the biggest problems with multiprocessor systems is the "memory wall" where multiple processors must share a certain amount of bandwidth to memory. My project provides a viable alternative to distributed shared memory models with a more cluster oriented design where each node in a multiprocessor network owns its own data and instruction memory.

Additionally a different approach was provided to the network through the design of a self optimizing asynchronous network, which can operate transparently below a synchronous CPU through a handshake. This same handshake protocol is also implemented in the system on a whole where it would be possible to interface any of the different modules designed for this project through this interface and it would work correctly. The network additionally implements a message passing algorithm, which sends out a message in the same fashion as a wave "crest" and in this way the network optimizations actually will burn in the paths over time to optimize commonly used path ways.

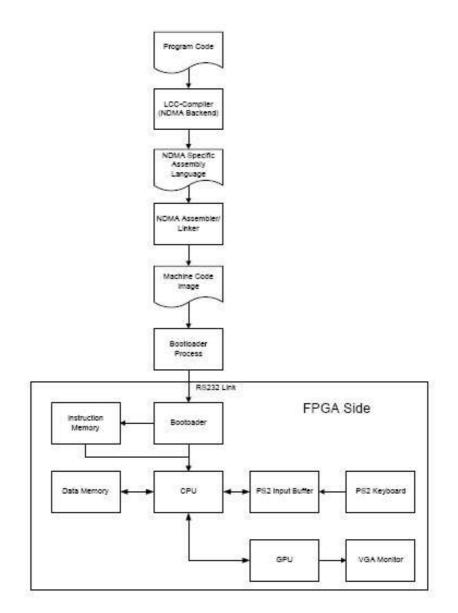

The design of a complete system on chip integration chain was accomplished. A new CPU architecture was designed, which implements all of the above as well as being as RISC as possible. The compiler, assembler/linker and bootloader software and hardware was designed for the CPU as well. Although minor bugs still exist in the system it was demonstrated to operate for significantly complex programs and test the functionality of the whole system including the CPU, IO, and software supporting systems.

A large portion of this project was oriented around making programming of multiprocessor environments easier by utilizing this new architecture and system topology. This involved the design of new programming conventions and methodologies that had to be supported both on the hardware and software side.

The design was then implemented in simulation first to validate the functionality and claims but also it was implemented onto an Altera CycloneII FPGA on a Terasic DE2 board. This configuration allowed access to the crucial hardware needed to validate the design, such as a VGA monitor, PS2 keyboard, and RS232 serial connection. The design also included modules that would have enabled the use of the LCD display and audio codec.

## Contents

| 1        | Intr | roduction 3                                                                                                                                                  |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  | Project Overview and Specifications                                                                                                                          |

|          | 1.2  | Rationale and Motivations                                                                                                                                    |

| <b>2</b> | Har  | dware 5                                                                                                                                                      |

|          | 2.1  | NDMA CPU Architecture                                                                                                                                        |

|          |      | 2.1.1 First Pass $\ldots \ldots $            |

|          |      | 2.1.2 Memory Hierarchy                                                                                                                                       |

|          |      | 2.1.3 Datapath                                                                                                                                               |

|          |      | 2.1.4 Instruction Set $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots $                                                               |

|          | 2.2  | Network Layer                                                                                                                                                |

|          |      | 2.2.1 Message Passing $\ldots \ldots \ldots$ |

|          |      | 2.2.2 Adaptive Network                                                                                                                                       |

|          |      | 2.2.3 Network Driven Operation CPU Side                                                                                                                      |

|          |      | 2.2.4 Network Driven Operation Network Side                                                                                                                  |

|          |      | 2.2.5 Network Programming Conventions                                                                                                                        |

| 3        | Soft | tware 22                                                                                                                                                     |

|          | 3.1  | LCC NDMACompiler Back end 22                                                                                                                                 |

|          |      | 3.1.1 Pseudo Instructions                                                                                                                                    |

|          |      | 3.1.2 String Resources                                                                                                                                       |

|          |      | 3.1.3 Unsupported Instructions                                                                                                                               |

|          |      | 3.1.4 Stack Pointer                                                                                                                                          |

|          |      | 3.1.5 Usage                                                                                                                                                  |

|          | 3.2  | NDMA Assembler-Linker                                                                                                                                        |

|          |      | 3.2.1 Linker                                                                                                                                                 |

|          |      | 3.2.2 Assembler                                                                                                                                              |

|          |      | 3.2.3 Directives                                                                                                                                             |

|          |      | 3.2.4 Normal Type Instructions                                                                                                                               |

|          |      | 3.2.5 J Type Instructions                                                                                                                                    |

|          |      | 3.2.6 Special J Type Instructions                                                                                                                            |

|          |      | 3.2.7 Network Instructions                                                                                                                                   |

|          |      | 3.2.8 PseudoInstructions                                                                                                                                     |

|          |      | 3.2.9 Conventions                                                                                                                                            |

|          | 3.3  | NDMA Bootloader                                                                                                                                              |

|          |      | 3.3.1 Usage                                                                                                                                                  |

|          | 3.4 NDMA Merge                               | 43        |  |  |  |  |  |  |  |

|----------|----------------------------------------------|-----------|--|--|--|--|--|--|--|

|          | 3.5 NDMA Suite                               | 44        |  |  |  |  |  |  |  |

|          | 3.5.1 Usage                                  | 44        |  |  |  |  |  |  |  |

| 4        | Results and Analysis                         | 44        |  |  |  |  |  |  |  |

|          | 4.1 NDMA System Single Core                  | 45        |  |  |  |  |  |  |  |

|          | 4.1.1 Open Issues                            | 48        |  |  |  |  |  |  |  |

|          | 4.2 NDMA Multi-core and Network Layer        | 49        |  |  |  |  |  |  |  |

| <b>5</b> | Conclusion                                   |           |  |  |  |  |  |  |  |

| 6        | Acknowledgments                              |           |  |  |  |  |  |  |  |

| 7        | Appendix A: Visual Nodes, Project Simulation |           |  |  |  |  |  |  |  |

|          | 7.1 Quad-List                                | 56        |  |  |  |  |  |  |  |

| 8        | Appendix B: NDMA Test Programs               | 57        |  |  |  |  |  |  |  |

| 9        | Appendix C: NDMA ISA                         |           |  |  |  |  |  |  |  |

| 10       | Appendix D: Index of Figures                 | 72        |  |  |  |  |  |  |  |

| 11       | Appendix E: Project Facts and Statistics     | <b>72</b> |  |  |  |  |  |  |  |

## 1 Introduction

#### **1.1** Project Overview and Specifications

This project consisted of the design of several components which, when put together, constitute a complete computer system. The approach used was modular in such a way that it could be possible to replicate these components to design a scalable system. Each component employs a uniform set of protocols which then allows the components to be connected in any assortment and allow the system to be scalable and parallel.

This was done through a new RISC CPU architecture complete with the compiler and assembler-linker required to run decently complex programs on the CPU. Also a boot loader was designed as to allow the CPU to be programmed and used in a variety of situations. However, security was not a main focus since this was beyond the scope of my project.

The CPU design is a new network driven architecture (NDMA) which allows each CPU to network with others in such a way that allows scalable multiprocessing. This would allow systems to be designed with parallelism in mind. The architecture was designed in such a way that the network component could then be used to drive the CPU itself. Many designs use a network by passing messages which are then interpreted by the CPU. This has the advantage of seamlessly passing data quickly between different processors. However, send a packet of data to a CPU which doesn't know what to do with it and it will simply look like noise. The design implemented in this project does not send data but rather sends instructions where all data must be encoded in pieces of code which the receiving CPU will then execute allowing increased flexibility in how parallel programs are designed.

Several other systems had to be designed for it to be possible for the observation that the project is actually working. This included the integration chain for the NDMA processor which I called the NDMA Suite. The Suite consists of the NDMA compiler back end for LCC, NDMA Merge which allows multiple assembly files to be integrated, the NDMA Assembler-Linker, and the NDMA Bootloader. Also some APIs were written for the GPU, PS2 Input Buffer, and network layer. Throughout the system interfaces must be upheld for asynchronous operation since many of the systems lived in different clock domains. In fact, the network layer was designed in such a way that it was self timed while the data that it received would be put through a controller which would clock the data so that it could be correctly passed to the CPU. This was possible through the use of the same handshaking protocol utilized system wide.

It can be noticed in the design that over time the design tended to evolve. This resulted in some redundancy in the design but it was deemed negligible and if needed this could be very quickly cleaned up. Cleaning up this redundancy would simplify the hardware design and make the design quicker to implement on an FPGA or increased simplicity of this design ever went to layout.

Since most of this design project was original there were not many alternatives to the design choices I made and their implementation details. On the other hand it would have been best if I could have found an open CPU core that provided the integration chain as well (such as bootloader, assembler etc). This was not easy to find and I justified my original design by the fact that I am in fact creating open source intellectual property through this project which is potentially useful for others.

With the above said I did not go ahead and write the compiler from scratch but rather used LCC which is an open source retargetable ANSI C compiler. Since this was open source the decision was valid. The other option would have been to write my own compiler and this combined with all of the other work I had to do with not a realistic goal even in the time that I had to work on this project.

Overall looking back at the design decisions I think that considering the scope and size of this project that it was very well planned out and that all of the requirements and specifications were met that I originally set out to accomplish. The hardware and simulations very much agree while the only thing that was not achieved in hardware was not originally speculated in the original design and only realized in simulation. This is explained more in the following report and specifically in the last part of the Results and Analysis.

#### **1.2** Rationale and Motivations

The original idea behind this project originated in the realization that current computer models today do not take much advantage of parallelism yet being parallel systems. The truth is that a common computer system consists of a main CPU but many of the other components and ASICs in a computer system also have a certain amount of computing power that is not utilized during the normal average operation of the machine.

One of the best examples of this is of a theoretical system that consists

of a video card, a sound card, and a central CPU. If the demands of the system are such that the sound card or the video card are only being used to their full potential half of the time then we can clearly see that there could be a similar system designed that could somehow parallelize the resources such that when the system does not require the video card for its designated purpose it could then the resource can be shifted and used for a different purpose. For example, using this scheme, it would be possible to design audio cards that expose their DSP capabilities and video cards that expose their SIMD capabilities through some kind of interface which allows the system to reconfigure itself on the fly.

With this kind of system in mind I designed a CPU Architecture that was network driven. This CPU is then capable of either executing it's instruction memory as is initialized by a standard boot loader or it can also dispatch instructions to other CPUs and likewise receive instructions from other CPUs. The idea behind this is that a CPU can then be "told" what to do and then reply with actions as well. These capabilities were also built into the assembler such that through standard coding practice these capabilities can be accessed although most of the APIs must be written in assembly since the data sent through the pipes should be instruction based since the network layer and the CPU are completely transparent to one another and the only way communication can occur is through full 32 bit instructions.

## 2 Hardware

#### 2.1 NDMA CPU Architecture

The project did not require a completely new architecture however it was noticed that the amount of changes required to a currently existing would warrant the development of a new CPU architecture and the design of the CPU from scratch. Also it was exciting to be able to decide on the design and to be able to integrate the network driven operation all the way into the design instead of a surface based approach. Another advantage of this was to be able to call the CPU original intellectual property. While the initial design of the CPU was motivated by the MIPS architecture only the OP code pairings are really preserved. There is no branch or load delay slot but the register designations are also preserved since it simplified the development of the compiler. These design decisions are also supported by the assembler

although these changes are minimal from the assembler's perspective.

#### 2.1.1 First Pass

The NDMA CPU Architecture is a 32 bit MIPS motivated single cycle CPU with individual data and instruction memories. The instruction memory is a dual port memory to allow for reading and writing on the same cycle and the data memory is single port. Also no cache is designed.

The most noticeable thing about this design is that it is a single cycle CPU. The idea behind this was to design a CPU that was as close to RISC as possible. For this reason there exists the individual data and instruction memories. The point of the architecture was not to make it fast but rather to make it RISC and easy to manipulate as to demonstrate the network side of things. However it was seen that this design, from an embedded standpoint, was rather sufficiently well performing.

#### 2.1.2 Memory Hierarchy

There were a few issues that arose regarding the memory hierarchy. First of all it can be noticed that there is no cache. The scope of this project did not require the design of a full cache as the design of one is non-trivial and would have required a large amount of debugging and development. Regardless of this fact since the CPU was going to be implemented on an FPGA where it was likely that the memory would be able to be clocked faster than the CPU itself it was unnecessary to develop a cache.

There was a large issue regarding the memory as well regarding the block sizes of the memory. The CPU designed was a 32 bit architecture and in turn required 32 bit memory line sizes. The way that these were implemented was through Altera M4K blocks of 32 bit width. This meant that it was impossible to allow unaligned memory access and required a good amount of compiler/assembler cooperation which is explained below. The reason that 8 bit width was not used, which would have enabled unaligned memory access, was because only 8 bits per cycle could have been accessed. It would have been possible to design a more complex memory module that would have consisted of 4 8 bit memory banks which would be striped but it was deemed enough to have 32 bit blocks and revisit and fix the inefficiencies at a later time.

A large difference in the memory hierarchy of this CPU and a MIPS CPU

for example is that there are independent data and instruction memories. The reason for this lies in a concept of resource redistribution over a network and system on chip design methodology. Also this was an idea motivated by finding a different approach to distributed shared memory. Each CPU has it's own instruction memory that can be manipulated by external CPUs as well as it's own data memory that only it can manipulate. Otherwise external CPUs may destroy data unknowingly by overwriting it. In this way each CPU has at least one resource that it owns exclusively.

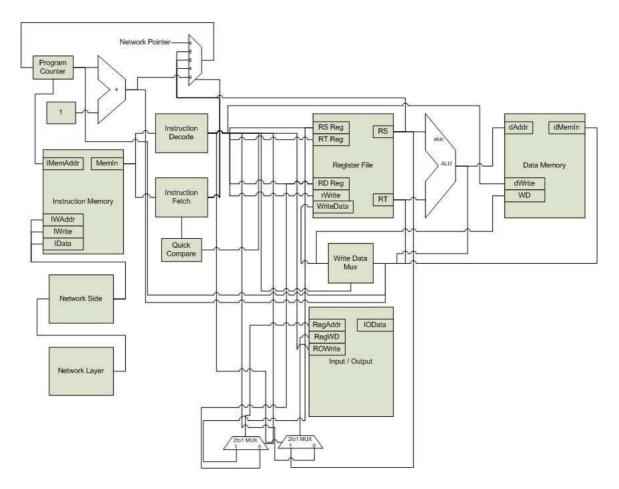

#### 2.1.3 Datapath

Below is shown a simplified datapath diagram of the NDMA architecture. Figure 1 is more for reference than an accurate design diagram (since it is missing many of the signal names) but it shows how this is a general single cycle CPU datapath. This looks very much like a normal single cycle CPU datapath except for the Input / Output module and the network driven side. It is not completely shown in this diagram how the network side is integrated into the instruction memory using an network instruction memory controller and how this is also integrated into the register file. These design details are described in the network portion of this section.

This is a single cycle CPU for the reasons mentioned above. At any moment the network side can interrupt the operation of the CPU and instead of focusing this project on how to properly manage the pipeline when dealing with such collisions I thought it would be better to focus on the systems development (compiler, assembler, bootloader) and on the network driven operation. It was also decided that the implementation of pipelining could always be done later and would be easier to integrate once the network driven architecture was more set in stone.

#### 2.1.4 Instruction Set

There is nothing revolutionary or new about the basis of the core design. The instruction set and core architecture was at first based on the MIPS instruction set. Not to mention that most of the core instructions in a CPU look very similar such as the ADD instruction. For this reason I used the MIPS base set as a launching point since I had some supporting examples that were a nice reference. However, there are many outstanding differences between the NDMA architecture and the MIPS architecture which qualify it

Figure 1: Network Driven Microprocessor Architecture Datapath

as a different architecture.

First of all it can be noticed that there are no branch delay slots. The reason behind eliminating branch delay slots was the fact that network based CPUs would need to strictly control the operation of the dispatched code on a different CPU and that collisions between branch delay slot instructions and network driven instructions may become an issue. It is likely possible to reintroduce the branch delay slot but the compiler/assembler would need to be smarter in this regard and since most of the network driven code is being hand written in assembly at this time it seemed better to get rid of the branch delay slot completely.

Another similar difference is the lack of load delay slots. There is some

redundant hardware currently that forces a NOP after a load but removing this does not affect the operation what so ever. The lack of load delay slots is motivated by a similar reason to the lack of branch delay slots. However it is also a result of independent instruction and data memories. The motivation of the independent data / instruction memories was an idea motivated by resource distribution on a network. This is explained above in the memory hierarchy section. This actually ends up being a positive effect of the memory hierarchy which simplifies the compiler design.

At first the instruction set was very similar to the core MIPS instruction set but over time new instructions were introduced and old ones taken out to make way for network oriented instructions. I wanted to make sure that although network and CPU instructions should never be decoded in the same space they should still not overlap as much as possible. This was more for debugging purposes but since there are so few exclusively network driven instructions there was not much issue with this.

Of the new instructions introduced into the ISA are the input / output instructions: IN, OUT, and OUTI. Also the CPU side network instructions: SID, BCST, SMSG, BCSTR, SMSGR. Also there are the network side network instructions: SNIP, JALNET, and NDJR. There exist two network driven instructions that were never implemented completely as well: NACK and RMSG. These were planned for originally but deemed redundant especially since their operation proved somewhat complex as well. The multiple and divide instructions were deprecated since they were implemented brute force with Altera megafunctions for a brief time. They were tested and working fine but were not too great for timing. They were taken out with the plans to implement a dedicated multiply and divide unit when time was available.

#### 2.2 Network Layer

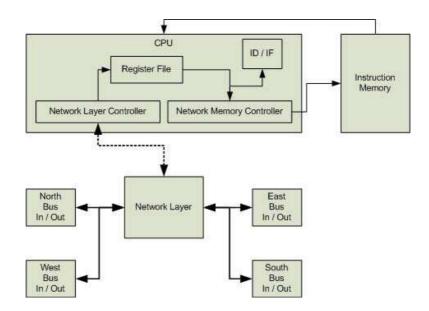

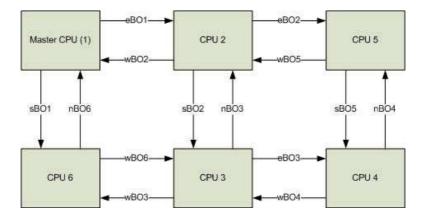

The Figure 2 below shows the basic overview of the Network Layer structure.

The idea behind the network layer is that it should function transparently to the CPU. This means that if the network layer is passing a message it will not affect the functionality of the CPU. The network layer is not clocked except for the send portion. It will correctly react to incoming messages regardless of the time at which those messages are received. The send portion, since it is triggered by a send message or broadcast message instruction from the CPU, must be clocked however. This is not clocked by an actual clock but rather self-timed due to the send flag, dxFlag, which is clocked by the

Figure 2: Network Layer Architecture Overview

network controller module.

The network layer is driven by a network controller which decodes the CPU side network instructions such as set ID, and send message. For the case of a send message instruction the network controller module will then decode the instruction on the negative edge of the clock and set the dxFlag to high. The dxFlag then is used by the network layer to set the output busses to the correct values. This is done on the positive edge of the clock to allow all of the send values to be correctly set before the message is set out on the network layer busses. The dxFlag is pipelined into a register to avoid from sending the same message twice or in the case that the same message is required to be sent twice and ensure that there will be a NULL message on the bus between messages.

#### 2.2.1 Message Passing

The messages are sent out on a 32 bit bus and each message contains the 7 bit destination CPU's ID, 8 bits of the message data, the 7 bit origination CPU's ID, a 4 bit message age, a 2 bit origination direction, and a 2 bit last taken direction. Each one of these values is used to help navigate the message to its correct destination. Figure 3 shows the composition of a message.

| 8 Bit       | 8 Bit   | 8 Bit       | 4 Bit   | 2 Bit       | 2 Bit Last |

|-------------|---------|-------------|---------|-------------|------------|

| Destination | Message | Origination | Message | Origination | Taken      |

| ID.         | Data    | ID          | Age     | Direction   | Direction  |

Figure 3: Message Composition

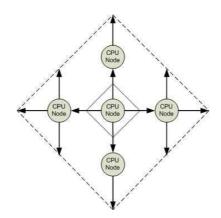

The way that the network layer propagates a messages gets its motivation from wave propagation. This was demonstrated with a C++ based simulation before implementation to prove that this algorithm will work correctly since it is much harder to debug and prove in Verilog. The overview of the algorithm is shown in Figure 4.

Figure 4: Message Passing Algorithm

The idea behind this algorithm is to always maintain a wave "crest" of the message and try to keep this crest as coherent as possible. A big problem is when multiple message crests collide and this must be dealt with by using a message buffer. This was not yet implemented in the hardware design but it was simulated in the simulation program.

The algorithm works by the original message source sending out the message in all directions setting the appropriate data values to the different fields of the message. In the case that the message is a broadcast message (which should be received by everyone) then the message's destination ID field is replaced with 0xFF which when read by the Network Layer will be seen as a broadcast message. Note that the IDs 0xFF and 0x00 are reserved for special cases such as broadcast and null IDs. This is important for the correct

operation of the network layer and also disallows an ID to be changed once it is set.

When a message is received by a node first the destination ID is compared to the ID of that node. This is why it is extremely important to provide a ROM image initially in a CPU node's memory that will set the ID to the correct ID. The conventions of how to use this system regarding writing actual programs is described in the Results and Analysis section. After checking the destination ID the network layer then decodes the origination direction and deals with the message in different ways based on the bus that the message was incoming on.

The general idea is that "horizontally" traveling messages will produce new messages on in the same direction as they were originally traveling as well as the directions perpendicular to their originating direction. However, messages traveling in "vertical" directions will simply continue to propagate in the vertical directions. This can be compared to dragging one's finger across the face of water.

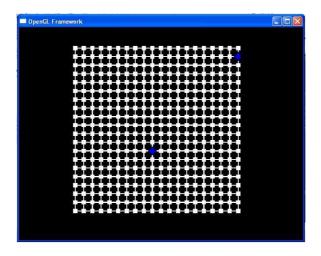

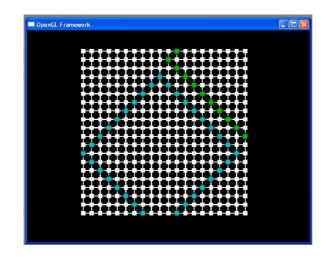

This was shown to correctly work in the Visual Nodes simulation program. This program is further discussed in Appendix A. Figure 5 shows two blue nodes sitting on an arbitrary network of other CPU nodes. These nodes' CPUs have received instructions to send messages to two other nodes on the network. Notice that these nodes have no idea where the destination node is in the network. This constitutes a packet switched network where the message propagated contains very simple routing information.

Figure 5: CPU Nodal Network at Initial State

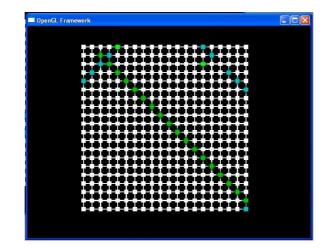

Next we see how the algorithm described before effectively creates two message crests. Each message is identified by it's own individual color as to differentiate between the two and show that no lossiness of message occurs since each node has a message queue in the network layer. Simulation shows this but this was not implemented in hardware. Figure 6 shows the simulation of this scenario. Notice that when the messages reach the boundary of the network they are lost. This is OK to do since we know that the message must have arrived if all the connections were made correctly and the messages passed according to the algorithm.

Figure 6: Message crests formed after two nodes send out a message to an unknown ID on the network

Eventually the messages are received by the destination CPUs as shown by the neon green node in Figure 7. Notice that we do not need to worry about the rest of the messages on the network since we know that only one CPU on the network has the unique ID being sent to. So once the message arrives we no longer need to worry about the coherency of the wave. Notice there is a hole "horizontally" behind the receiver node. This is because at this node the message is not propagated.

Figure 7: The messages are received by the correct CPU nodes on the network

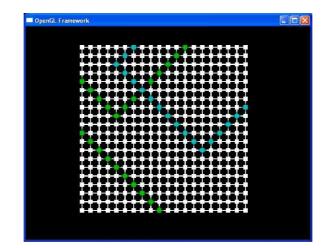

In the simulation the node will initially pend for a few cycles. Then to prove that the data was received correctly, as encoded by color, it will send back the same message to the original sender of the message. This is shown in Figure 8. In the real implementation of this the way that CPUs would communicate is much different as will be explained in further detail. Notice that the origination direction of the message is taken into account went the reply is sent. This was never done for the hardware as well but could be in the future with some expanded instructions.

The only current open issue is that in the real implementation the message queue has not been implemented so that collisions are a real threat to the system. Collisions can only truly occur when multiple nodes are communicating on the network at the same time. It was decided that to prove the validity of the system the message queue would be something extra to strive for. It would be relatively easy to implement especially considering that the functional model has already been outlined in the Visual Nodes simulation.

#### 2.2.2 Adaptive Network

The network layer explained up until now has been a packet switching network. However, it is obvious that this can be rather inefficient if two nodes on the network tend to communicate much more often than other nodes on the network. It would be much more efficient if the network could somehow evolve to treat commonly used paths as circuit switched networks rather than

Figure 8: Message replied to original sender with same data

packet switched networks so that routing occurs automatically after a certain fitness threshold.

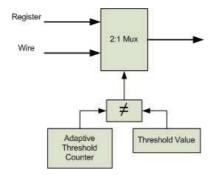

Exactly this was done in the network layer through the implementation of what I call a register-thru design. Essentially each directional bus also owns a certain threshold counter which is initialized to zero. Each time that a network message passes through the node this counter is incremented by one while each time a message is received this counter is decremented by one. If the counter reaches a certain threshold value it is no longer incremented but at this point the node begins to pass messages along this bus without holding on to them. However, the node does catch a glimpse of the values so it is possible for the CPU to still receive messages on this connection while the message will still pass through the node. This has no real consequences, however, since nodes need to have unique IDs. When a message is passed with matching destination ID the cut off node will "awaken" but needs to continue to get multiple messages as to not shut off once it receives a different message of mismatched ID. Also a broadcast message will reset this counter to zero.

The way that the register-thru design is implemented is by multiplexing a wire and register design. When the counter is below the threshold value the bus will first pass the message by setting the output register to the input value. This requires a certain delay and is less optimal than a pure wire. When the counter reaches a certain value the output is multiplexed to the

input and hardwired so that the input is seen on the output at the same time neglecting the actual delay of the wire. Using this register-thru design we can extremely optimize a network which may have an arbitrary node delay. The register-thru design is shown in Figure 9.

Figure 9: Register-Thru Design Implementation

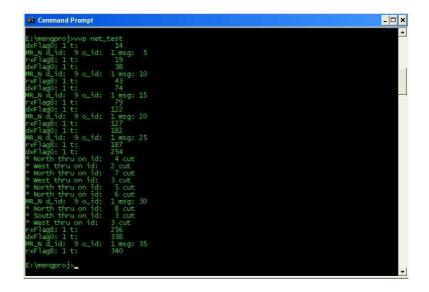

To demonstrate some of the functionality of this register thru design the following print out of a command line simulation is shown in Figure 10. A more conclusive result is shown in the Results section but this is a quick demonstration in simulation of the design in action. Notice that messages are being passed back and forth with a certain delay. Once the threshold count is arrived at for a few nodes the connection is cut and adaptively converted to circuit based connections. The delay is then reduced to a delay of two units where the original delay was 5 delay units. Note, however, that this is a nodal network of only 9 nodes. The potential improvement can be rather scalable.

#### 2.2.3 Network Driven Operation CPU Side

There are two sides to the network driven operation of the CPU. The CPU side which is dictated by instructions coming out of the instruction memory and Network side which is dictated by the network literally driving the CPU through instructions dispatched to it through the network. This section deals with the CPU side of sending and broadcasting messages.

You will notice that in the design there are remnants of other instructions and other such issues that need to be re factored. Due to time constraints these are being ignored since they are not affecting anything but they will be described and considered here since they may in the future be implemented.

Figure 10: Adaptive network command line simulation

The receive message instruction RMSG was originally going to be used to allow a CPU to pend on a receive. However, with the way that the project has shifted since the original introduction of this instruction this never had to be implemented. The only place this instruction is seen is in the ndmaref.h file which defines the OP-Codes for the CPU. Another instruction that falls into the same category is the NACK instructions (although Network Side). In the end a different approach was taken to the NACK functionality instead of a dedicated instruction which would have been somewhat inefficient.

The only CPU side instructions that occur consist of send message (SMSG), broadcast (BCST) and their register based counter parts. The usage of these instructions is as follows:

```

smsg $destination_ID, message

smsgr $destination, $message, byte_offset

bcst message

bcstr $message, byte_offset

```

The normal versions of SMSG uses the value inside of the register \$destination as the destination ID of the message being sent. The message is then sent as described at the beginning of this section. The normal version works the same way, however it requires no ID since the ID sent in the message is

0xFF which notifies the network layer that this is a broadcast message. A broadcast message will also "wake" up all nodes in it's path.

After the BCST and SMSG instructions were implemented and some of the system had been implemented it was obvious that it would be needed to have the same instructions except register based. This would allow the sending of the whole contents of a register. Since the message sent can only be 8 bits 4 messages must be used to send a full 32 bit package. Doing this by hand through the use of hexadecimal digits or decimal digits would be extremely cumbersome. Instead register versions of the instructions were designed which allow you to send an 8 bit piece of a 32 bit register through the use of the byte offset. The byte offset designates 3 as the most significant byte. In this was the following series of instructions can be used to broadcast an instruction to another CPU:

```

ori $a0, $0, 0

lui $a0, Instruction First Half

ori $a0, $a0, Instruction Second Half

bcstr $a0, 3

bcstr $a0, 2

bcstr $a0, 1

bcstr $a0, 0

```

Using this convention it was possible allow a CPU to initialize a register with an instruction that it would like to dispatch to another CPU and then utilize the bcstr / smsgr instructions to piece wise send the instruction. Note that the first three instructions above would be commonly repeated often and complex to program by hand. These were integrated into a pseudo instruction called SRI or set register instruction. This pseudo instruction is further explained in the assembler section.

#### 2.2.4 Network Driven Operation Network Side

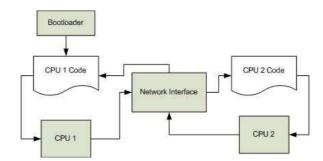

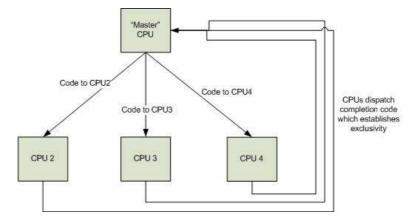

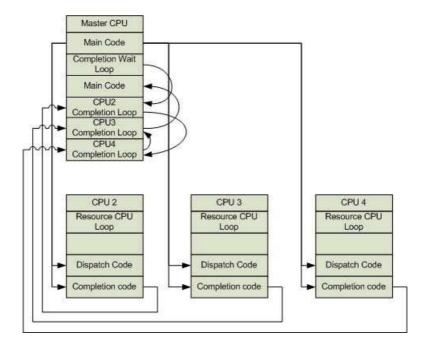

Once the instruction reaches the point of being in the pipes it is considered a network side instruction. The basic principles of the system network driven operation is shown in Figure 11. What is being shown in the diagram is that CPU 1's instruction memory is originally initialized through the use of the NDMA Bootloader. This memory will then drive CPU 1 and allow CPU 1 to dispatch instructions to other CPUs. Only a two CPU system is shown

here for simplicity. This is effectively enabling CPU 1 to boot load any of the other CPUs on the system. The way that this is done will be explained in this section. Once a different CPU on the network is boot loaded and running it can then return the favor and replace or re-boot load CPU 1 or any other CPU on the network. If wanted this can create an infinite chain of CPUs not only passing data messages but also passing the code required to parse those messages so that you can design programs with dynamic parallelism.

Figure 11: Network side system operation and communication

For this to be possible a few different specialized instructions need to exist which only manipulate the network layer. These instructions consist of the following:

# snip pointer\_value jalnet ndjr \$target\_register

The way that the network layer receives information has two parts. When a message is received by the network layer it is then saved to a specialized register in the register file indexed by a network message counter. This counter is incremented each time a message is received and saves that 8 bit message into the register indexed by the counter. Once 4 messages have been received then that constitutes a full 32 bits received.

When the instruction received from the network is valid the register file sends the instruction to the network memory controller which will then look at the instruction and either write it to a specific location in instruction memory or decode it if it is a special instruction. The way this works is that the network memory controller contains a pointer into memory which defines the network memory "space" in instruction memory. This pointer

can be changed with one of the above SNIP instruction which stands for Set Network Instruction Pointer. It should have been SNIMP since it's an Instruction Memory pointer but SNIP tends to have a ring about it's functionality. When a SNIP instruction is decoded the CPU is not driven with any specific functionality but rather the instruction memory pointer is set to the value passed by pointer\_value. Notice that when a special instruction is received by the network instruction memory controller that it is not written to memory.

There also needs to be a way to have the target CPU start executing the instructions in the network portion of the instruction memory as well as a way to force them into their previous operation. The instructions JALNET and NDJR do exactly that. JALNET is a network driven Jump and Link. This works the same way a normal JAL would work except the location to jump to is taken as the instruction memory pointer. When a JALNET is received it will be decoded by the network instruction memory but also passed to the Instruction Fetch and Instruction decode modules in the CPU data path. The CPU will then be driven by this instruction and jump to the correct location. A NDJR instruction works the same way where all of the registers initialized by the ID and IF stages in the CPU. The NDJR instruction stands for Network Driven Jump Register and works exactly the same as a normal Jump Register instruction except that it has precedence and is network driven.

One issue regarding network driven instructions was the question of what of the current instruction? The decision was made to give precedence to the network driven instructions, or specifically JALNET which should be the only one that has any problems, since with JALNET the current pointer is saved into a register and while a normal JAL will save PC + 1 to the register JALNET was changed to save the pure PC to the register because when a JALNET occurs we are consistently blocking an instruction that must be preserved.

#### 2.2.5 Network Programming Conventions

The meat of this topic will be discussed more in the assembler section since most of the conventions applied will be done on the software side. In fact the design architecture is good to go as is, however it is rather cumbersome to program. The way that this is done is through specialized assembler side instructions which will dispatch instructions through an API. The idea

behind this is that a node cannot actually dispatch data to another processor but rather must send an instruction with that data encoded within it.

Although this may convolute the process of sending data from one processor to the other it also ensures that the interfaces are standard and that data is passed in a very interface oriented way. This allows processors to literally tell each other what to do rather than simply pass data back and forth. If a node is smart about the code that it dispatches to another processor than it is quite easy to design a system with rather complex parallelism.

Since for every instruction sent at least 4 instructions must be executed the instructions sent must be parallelized functions as is. So instead we could design a system which dispatches out a few different pieces of code to different processors which loop. These loop until completion at which point they send back instructions to the dispatcher CPU with their results where the dispatcher CPU was the one to tell them to do that. Until this occurs the dispatcher CPU is sitting on a loop waiting for the results from the dispatched process. Once this occurs the dispatcher executes the network memory, returns to a point outside of the loop (or sets a branch condition false) and then retrieves the result out of the point in which it was stored.

This is a simple scenario but imagine multiple CPUs processing different programs at the same time all the while the dispatcher CPU is sitting on a useful loop of some sort. As long as the code dispatched will run for at least 4 iterations on average we can see that this parallelism will benefit us. Especially as you increase nodes in the system since as soon as you create code that can create more code each node can then dispatch to three other nodes (not including the node it received the code from in the first place). Although my project was more of an infrastructure project this architecture seems much more realistic for parallel programming than the current methods which currently use distributed memory sharing with the very serious memory bandwidth bottleneck.

Another very important possible use of this architecture is to enable resource sharing and system reconfiguration. It would be possible to have one processor connected to one resource and have all processors relay their information to a centralized processor which would then organize all of the resources. However, when the resources are not needed it would be possible to better utilize the CPUs for other uses such as computation. This dynamic parallelism could be very useful in consumer type computers where resource need is very diverse rather than in computationally intensive computers where data is the main thing that matters.

## 3 Software

Apart from the hardware design of this project a variety of software had to be written. This section describes these software systems.

### 3.1 LCC NDMACompiler Back end

The NDMA architecture needed to have a compiler so that decently complex programs could be written both to test the system as well as make the system usable. The compiler used was LCC which is a retargetable ANSI compatible C compiler. The back-end was written such that the assembly language the compiler generated was specific to the NDMA architecture and would interface cleanly with the assembler.

A big problem that I encountered while using LCC was build related due to my Windows XP operating system. I could not quite get LCC to build correctly and in turn compile my code into NDMA specific assembly. Instead I discovered RCC which is the program that actually generates the assembly. In the case of a standard C error RCC will output a message however it will not stop generating assembly. This, for my purposes, was enough and since LCC utilizes RCC I am sure that on a system which can build LCC correctly (e.g. Linux) that LCC would work fine for my compiler back end.

The way that LCC's back end works is through an interpreted definitions file which is interpreted by a program named lburg. The file is a long listing of function calls and instruction definitions. A rather large amount of the file is standard for all code targets so I started off using a specification for the MIPS R3000 that is provided along with the source code for LCC. After this I went through the file changing all of the different instructions so that they will be compliant with my NDMA assembler as well as compiler conventions. Since I did not write LCC it was occasionally easier to keep certain conventions and then deal with them in the assembler.

#### 3.1.1 Pseudo Instructions

There were a few pseudo instructions that were used in the compiler which I could not completely eliminate from the back-end and had to implement in the assembler. Most significantly was the pseudo instruction LA which stands for Load Address. In most cases this instruction would be used as

la \$destination, offset(\$source)

#### 3 SOFTWARE

The use of this instruction would be used to load in the effective address of the offset + \$source into the \$destination register. It would have then been very easy to simply replace every LA instruction with

#### addi \$destination, \$source, offset

This was not possible since LCC uses the LA instruction in a variety of ways all the while only having one specification for it. The LA specification in the lburg file is as such:

#### reg: addr "la \$%c, %0\n" 1

This indicates that the field filled by %0 can be anything as provided by LCC. This is in fact true and was found to be of any of the following:

## offset(\$source) offset

#### Label

The label in the above snippet means that not only is the LA instruction used to initialize registers with effective addresses as to be used for the purpose of initializing them with numerical constants but it was also used to load registers with values designating pointers to instruction memory. This became especially prevalent when dealing with resource strings in programs where LA was used as a pointer to instruction memory so that strings could be read out of the program's code.

NDMA has an independent instruction and data memory. So changing the lburg file for LA was an impossibility. Instead the assembler was designed in a much more clever way as to perceive which form of LA it was receiving and as such decode and assemble it so that it would work correctly. This became somewhat complex for string resources since it required a collaboration on both parts of the assembler and compiler as will be described below.

#### 3.1.2 String Resources

As mentioned before the NDMA has a separate instruction and data memory. This allows for network driven operations as well as maintain more of a RISC oriented operation. However it has rather big issues regarding how LCC would process string resources in a program. Traditionally when a programmer defines a string in a program the string is saved at the top of the assembly code using .byte directives:

```

.SetStack 255

.Boot main

.rdata

STR_LABEL1:

.byte 72

.byte 45

.byte 44

.text

.text

main:

... code ...

la $3, STR_LABEL1

lb $4, 0($3)

... code ...

```

Then when the string was encountered in the code it would use the STR\_LABEL1 to designate a point in memory and load the effective address into a register which would then be used to load the memory from. This would not work using the hardware architecture. Also a big point to note is that the memory used for the CPU had 32 bit wide blocks as mentioned above. It was then important to change the way data was loaded and stored into memory when it's size was less than 3 words.

To deal with these issues the code that would load and store data in LCC was altered to the following:

```

static void blkfetch(int size, int off, int reg, int tmp) {

int i;

assert(size == 1 || size == 2 || size == 4);

if (size == 1)

print("lbu $%d,%d($%d)\n", tmp, off, reg);

else if (salign >= size && size == 2)

print("lhu $%d,%d($%d)\n", tmp, off, reg);

else if (salign >= size)

print("lw $%d,%d($%d)\n", tmp, off, reg);

else if (size == 2)

{

// LH for .Byte here

print("ori $%d, $0, 0\n", tmp);

}

}

```

```

// Second byte

print("lw $1, %d($%d) \n", off + 1, reg);

print("sll $1, $1, 8\n");

print("or $%d, $1, $%d\n", tmp, tmp);

// First byte

print("lw $1, %d($%d) \n", off, reg);

print("or $%d, $1, $%d\n", tmp, tmp);

//print("lhu $%d, %d($%d)\n", tmp, off, reg);

}

else

{

// LW for .Byte here

print("ori $%d, $0, 0\n", tmp);

for (i = 0; i < 4; i += 1)

{

print("lw $1, %d($%d) \n", off + (3 - i), reg);

print("sll $1, $1, %d\n", (3 - i)*8);

print("or $%d, $1, $%d\n", tmp, tmp);

}

}

}

static void blkstore(int size, int off, int reg, int tmp) {

int i = 0;

if (size == 1)

print("sb $%d,%d($%d)\n", tmp, off, reg);

else if (dalign >= size && size == 2)

print("sh $%d,%d($%d)\n", tmp, off, reg);

else if (dalign >= size)

print("sw $%d,%d($%d)\n", tmp, off, reg);

else if (size == 2)

{

// First

print("sw $%d, %d($%d)\n", tmp, off, reg);

print("srl $%d, $%d, 8\n", tmp, tmp);

// Second

```

}

What this effectively does is when loading bytes the compiler will put out assembly instructions that treat each byte as being on an individual line of memory and then pack them into a register so that when the CPU deals with the data in the register it would do so as it would normally would. The same thing is done for stores which will unpack the data and store each byte on an individual line in memory.

So after this translation the compiler can deal with the bytes as it normally would since they are packed into the register. The only other issue is to ensure that when the resource is accessed the data is stored into data memory correctly. This is done mostly by the assembler as is described in the next section. However, it was also important to make sure that the correct data location was used by the .byte directives. This was done by appending the following after the string label:

#### print("la \$1, 0(\$0)\n");

This would load 0 into the \$1 register which is the temporary compiler register so that when the .byte directives are "run" and exited that the correct location in memory is accessed. Notice that this instruction has the possibility of being used with differential locations in memory. Currently the code will write only to a specific point in memory opposite to the Stack Pointer and will hopefully not have problems regarding collisions. I could not find a way to extract size information from the labels so for the time being the location must default to 0.

So with these precautions taken and with the assembler dealing correctly with the LA instruction and the .byte directives, string resources will be dealt with correctly although through a somewhat convoluted process. They are first unpacked into memory by running a snippet of code which is derived by the assembler from the .byte directives. Then the loads will pack the data memory into registers and when storage is required they are unpacked into memory. There are a few issues regarding the default locations in memory since string manipulation may not correctly work, this has not been fully tested although multiple strings have been tested and work correctly.

#### 3.1.3 Unsupported Instructions

The NDMA supports a variety of instructions but for simplicity of testing and ensuring that the system worked many of these instructions were disabled. This included more complex instructions like multiply and divide. However, there were a few instructions that simply required validation time that have yet to be integrated enabled on the CPU which were not deemed that important that the difference between them being one instruction or two mattered.

For one only BNE and BEQ branch instructions were fully tested and so any form of branch was some permutation of SLT, BNE, or BEQ. This is shown below:

```

stmt: EQI4(reg,reg)

"beq $%0,$%1,%a\n"

1

stmt: EQU4(reg,reg)

"beg $%0,$%1,%a\n"

1

stmt: GEI4(reg,reg)

"slt $1, $%0, $%1 \nbeq $1,$0,%a\n"

1

stmt: GEU4(reg,reg)

"sltu $1, $%0, $%1 \nbeq $1,$0,%a\n"

1

stmt: GTI4(reg,reg)

"beq $%0, $%1, 2 \nslt $1, $%0, $%1 \nbeq $1,$0, %a\n"

1

"beg $%0, $%1, 2 \nsltu $1, $%0, $%1 \nbeg $1,$0, %a\n"

stmt: GTU4(reg,reg)

"beq $%0, $%1, %a \nslt $1, $%0, $%1 \nbne $1, $0, %a\n" 1

stmt: LEI4(reg,reg)

stmt: LEU4(reg,reg)

"bleu $%0,$%1,%a\n"

1

stmt: LTI4(reg,reg)

"slt $1, $%0, $%1 \nbne $1, $0, %a\n"

1

stmt: LTU4(reg,reg)

"sltu $1, $%0, $%1 \nbeq $1, $0, %a\n"

1

stmt: NEI4(reg,reg)

"bne $%0,$%1,%a\n"

1

stmt: NEU4(reg,reg)

"bne $%0,$%1,%a\n"

1

```

Also NOT instructions were not implemented on the CPU so a NOT was interpreted as a combination of addi and XOR to first initialize a register to all ones and then xor that with the register in question.

reg: BCOMI4(reg) "addi \$1, \$0, -1\nxor \$%c, \$1, \$%0\n" 1

#### 3.1.4 Stack Pointer

As described above the memory is of width 32 bits and thusly when the stack needed to be manipulated it did not need to be incremented/decremented by counts of 4. Instead it manipulated by counts of 1 and as such through the LCC back end this had to be changed. Most of this was done by setting the argument offsets as 4 rather than 16 and adjusting values in the back end to ensure of this. Most of the changes were implemented by validation through the use of simple test programs.

#### 3.1.5 Usage

To use the compiler it must be built. To do so you must run the following in a Visual Studio 2005 build window or a build environment which has nmake from Visual Studio 6.0 or later:

```

...ProjectModules\LCC>set BUILDDIR=\lcc_build_directory

...ProjectModules\LCC>nmake -f makefile.nt all

```

This will build the compiler into your build directory you specified and then to compile a program you must run:

...build\_dir> rcc -target=ndma/ndmaOS filename.c

This will spit out the assembly code which can then be "cut and paste" into the assembler code which should include some of the APIs as explained below. If wanted it is possible to output the rcc output to a file by doing the following:

```

...build_dir> rcc -target=ndma/ndmaOS filename.c > outfile

```

This file can then be used by the NDMA Suite as explained below. If you add the RCC path to the system's PATH variable (accessed through control panel-¿System-¿Advanced-¿Environment Variables or the SET command in the command prompt) then you can utilize the NDMA Suite along with NDMA Merge to output files that can then directly be assembled and boot loaded.

#### 3.2 NDMA Assembler-Linker

The NDMA Assembler-Linker is a combination of a linker and assembler to simplify the integration chain design so that it could be feasibly designed in the time allotted. The Assembler began development along side the development of the NDMA CPU Architecture as to guarantee that the two will work together in unison from the get go. However, as time progressed and requirements of the assembler grew the design of the assembler had to be re factored so that new instructions and functionality could be incorporated into the program.

The NDMA Assembler-Linker consists of two parts as the name suggests. The first part is the linker which needs to run before the assembler considering the design of the program and it's structure. After the linker runs through the file one time the assembler is run assembling each instruction and using the data collected by the linker to set the correct targets for the assembled instructions.

#### 3.2.1 Linker

The linker needs to know almost as much about each line of the input assembly file as the assembler itself. If not the target locations of jumps will not correctly be calculated. This means that the linker portion of the assembler is pretty close to the assembler itself except it does not need to decode the instructions but only match them up to the data base of accepted instructions, directives that are translated to instructions, pseudo instructions and the correct behavior of these pseudo instructions based on differing circumstances, and different special instructions. All the while the parsing of the file will tabulate a data structure with all of the different labels and the correct PC location of those labels in program code.

The way that the linker does the above is by reading each line of code at a time. This is done in 100 character pieces since it is assumed that each line should not exceed this amount in characters. This input is then tokenized and the first token is compared against a number of conditional statements in an exclusive order. This is done in such a way that the special instructions take precedence over the normal ones since all instructions are registered in the s\_mapOP, which is a map data structure of all of the instructions the assembler supports.

First the token is compared to the LA instruction. As explained above

the LA instruction is a pseudo instruction that has different functionality in a number of different circumstances sometimes being translated to 2 instructions and other times to only one. The exact way this is done will be explained more fully in the assembler portion below. There are two different circumstances for the LA pseudo instruction. Either it is calculating an effective address and will be translated to one instruction which will be an addi. Or it will be translated into two instructions when the offset is found to be a label. Since at this stage we cannot guarantee that the label specified in the LA offset field will be in our database we must check to see if it is a label in a different way. This is done by noting that label based LA instruction will have at least one letter in the offset field. Otherwise this field must be an immediate type number. If a letter is found in this argument then the LA instruction increments the PC counter of the linker by two otherwise only by one.

The next special instruction that is looked at is called SRI or Set Register Instruction. This instruction is further explained in the later network driven assembler portion however the basic functionality of it is that it takes a register and a normal instruction as two inputs and then loads that instruction into the register. This requires a register clear with an ORI instruction and a combination of one LUI and one ORI instruction. This sums to a total of three instructions and when the linker comes across this instruction it increments the PC counter of the linker by three.

After these two special instructions the linker checks for an empty line. If it is not an empty line the linker checks against the directives .Boot, .Set-Stack, and .byte. The .Boot and .SetStack directives both get translated to one instruction. The .Byte directive, however, gets translated to two instructions so in the case of the .Byte directive the linker adds two to the linker's PC counter. In the other cases it simply adds one and in the case of an empty line the linker skips on to the next line. Also at this point the linker compares the first token to the list of supported assembler instructions. If it matches then one is added to the linker's PC counter.

If after all of the checks the first token of the line does not match any of the above conditions then the first token is checked for consistency with the format of a label. The way that this is checked is by checking to see if a colon is found in the token. If yes the token is tokenized and then inserted into the s\_mapLabel map data structure. When this is done it is checked to see that duplicate labels are not found in the file. If this is the case then an error is thrown and the program exited showing which label has been repeated. Once the linker is done the s\_mapLabel data structure should contain all of the information regarding the PC location and names of the labels that are encountered throughout the assembly file as well as ensure that no duplicate labels are found in the file.

#### 3.2.2 Assembler

Assembling an instruction requires a few different steps. Assembly is done slightly differently for different groups of instructions but apart from the special instructions, directives, and pseudo instructions all of the instructions are assembled in generally the same manner.

The first phase that the extracted line goes through is a quick and dirty token counting check. This is useful for a number of quick tricks to get the pipe going but mainly it provides a way to allocate memory for the correct number of tokens to be saved and used later. After the quick token check the input line is actually tokenized and each argument saved for use in the assembly process later.

After this the first token is run through a number of conditionals to check to see if the line is empty, a comment, directive, special instruction or normal instruction. If the line is empty or is a comment the pipe is skipped and the next line is looked at by the assembler. However in the case of a normal instruction (the other cases are dealt with below) there can be a few different cases. If the assembler receives more than 8 tokens it spits out an error message indicating that the instruction has too many arguments. If there are between 3 and 8 arguments then the instruction is dealt like a normal instruction other than J type instructions. If the instruction has 2 or less arguments then the instruction is dealt with as a J Type instruction.

Notice that if the first argument is found to be SRI this sets a "flag" for the rest of the program of fSRI to 2. This value is then used to offset all of the argument values if it is set so that after SRI has been found then the pipe will only look at the instruction passed to SRI. In this case the assembly works normally except only on the instruction passed to SRI. The SRI instruction is explained in more depth below.

#### 3.2.3 Directives

Checking the line to see if is a directive is done by checking the first character of the line. If this character is a '.' then that line refers to a directive. The

#### 3 SOFTWARE

LCC compiler spits out a good amount of directives that are not used by the Assembler but these were kept in since they provide good information about what the assembly code coming out of LCC means. The only directives that are directly implemented by the assembler are the .SetStack, .Boot and .Byte directives.

When a directive is encountered the period is stripped off and it is compared to the supported directives. Since this list is not long this is done manually but it would not be hard to implement a map of all supported directives with the current model since the period is tokenized away. If the directive is seen to match the .SetStack directive (which is a very important directive for the correct functionality of the data memory stack) then this directive is replaced by an ORI instruction which then sets the stack pointer to the value specified by the directive. By using this directive it is possible to designate to the program what the size of the CPU's data memory is. The correct setting of this is imperative for correct functionality. Otherwise, the stack will be placed at zero and the memory may behave unreliably. Note, however, that when the SetStack directive is used a variable in the assembler is set and will output statistics regarding the program's size versus the size of the data memory. Note that the data memory can be a different size than the instruction memory and the boot loader will load memory that does not exist. This debugging message can be double faced in that sense and realize that the SetStack directive only has to do with the data memory and not the instruction memory.

The next directive is the .Byte directive which will map to two instructions. The way that resources work on this architecture is that the .Byte directives become a small snippet of code which is called whenever the resource is needed. In this way each byte is loaded into it's own specific point in data memory and then the code snippet will return. The way that the code gets to this snippet is through the LA instruction which is explained below. However, each byte must be loaded into it's own location in memory and different strings of resource must be independent. This way the cData variable will be reset to zero when no byte directive is encountered to effectively reset it. Every time a succeeding byte directive is encountered, however, it is incremented. This way each string gets it's own space while each byte gets a succeeding location in memory. The cData variable is used to assemble the two instructions the .Byte directive gets translated to.

The last directive is less involved. The .Boot directive with be replaced with a jump instruction to the location of the label provided. The common

#### 3 SOFTWARE

use of the .Boot directive is .Boot main which will make sure that the first code run is the main code since between the .Boot directive and the main code there may lie a good amount of other code such as APIs or resources.

#### 3.2.4 Normal Type Instructions

For normal type instructions the first token of the instruction is checked up against the s\_mapOP map data structure. This data structure is initialized before the running of the assembler by the function:

#### (void) InitializeOPMap();

This function goes through the OPS enum and assigns an appropriate string to each correct enum element. These enums are then later used by the function OpFunctionSADecode() which will go through the map data structure and find if the token matches. If the token does not match an error message is output, however, if the token does match then this function will set the binary OP, and FUNCTION fields to the correct strings to be assembled together later. This function will also set the instruction type in the variable ins\_type which is then used to group instructions more effectively, although this generally is not precise enough and specific instructions must be checked individually as well as the instruction type.

After this stage the only thing left to assemble are the RD, RS, RT, IMMEDIATE, TARGET, and SHIFT AMOUNT fields. Before this is done the instruction passes through a number of conditional statements which ensure that the correct argument is used for the correct field since different instructions have different structures. This is done for convenience so that when the fields are assembled we can use a variable index rather than index constant values differently for different instructions.

After the field indexing stage the RD, RS, and RT are assembled through a function call RegDecode() which will take in one of the tokenized arguments and pass back a binary string that represents that argument. This function can support register arguments in their numerical form of "\$31" or their symbolic form "\$ra". This is nice since it provides us flexibility in how the assembly code is written and makes the code somewhat more readable. Although the output of the LCC code will still be numerical the APIs which are generally written in assembler will be somewhat more legible.

#### 3 SOFTWARE

At this point the only fields left are the IMMEDIATE, TARGET and SHIFT AMOUNT. The immediate and target fields are taken care of together. The normal type instructions only deal with the immediate field so the target field can be ignored. First the immediate argument is checked against the map of labels. If the instruction is a branch type instruction then this label is treated as relative rather than absolute. Whatever the value ends up it is saved to binary and then to the immediate field. If the immediate argument is not a label it is first checked to see if it is of hexadecimal format. Hexadecimal immediates were rather useful for debugging and general low level programming so that is why this feature was implemented.

If the argument was not of hexadecimal format it had to first be tokenized to see if there was an operand between two values. The LCC compiler on occasion would output expressions rather than constants. This was up to the LCC compiler and not the back end so I had to add this functionality to the assembler. The expression is tokenized and evaluated and if it is found that no operand exists or only one value is there then that value is simply converted to binary and saved into the immediate field. Once the expression is evaluated it's result is placed into the immediate field.

The only field left now is the SHIFT AMOUNT. The shift amount field is passed to the assembler in the immediate argument. This makes it easy for the assembler to find so it is taken, converted to binary and placed into the shift amount field. This is only done for SR\_TYPE instructions which stand for Shift Register instructions.

At this point all of the instruction fields have been correctly set and all that is left is to assemble them together. This is done differently for different sets of instructions and different instruction types by adding the different pieces one after the other into a buffer of length 32. Once this is done it is copied into the output stream as well as the output file. The output stream is nice to have since debug messages can be appended to it while the output file is the one that is sent to the boot loader. There are many different categories of instruction assembly but they are all done according to the rules of that specific instruction. This is important to note when adding new custom instructions to the assembler. Every portion of the process must see the effect of the new instruction. Occasionally the new instruction will not fit into a previously made grouping so a new one must be made. This must be done in an exclusive fashion.

#### 3.2.5 J Type Instructions

The J Type instructions always have two arguments or less and so have their own special way of being assembled. This way is instruction specific. Since there were few J Type instructions and all other instructions that fit into this mold were dealt with in such a diverse way this was the preferred way to do this. In this section I will only talk about the J Type instructions.

When an instruction is found to only have two arguments or less it is assembled on an individual basis. The only J Type instructions fitting this description are the J, JR, and JAL instructions. In each case the appropriate arguments are decoded and assembled as is done for the normal instructions but instead of using a pipe it is done on a per instruction basis.

The JAL instruction is followed by either an immediate type target or a label. When the instruction is assembled first the target is checked against the label map. Since the JAL address is absolute no relative calculations need to be made and the PC value of the label is converted to binary and then is assembled with the rest of the instruction fields. If the target is just an immediate then it is converted to binary and set into the target field and assembled with the rest of the instructions.

The JR instruction is done in a similar fashion except the register argument is decoded using the RegDecode() function and then set into the appropriate field and the instruction is then assembled. The J instruction is very much similar to the JAL except for slightly different OP codes. Since the instructions are done on an individual basis each instruction needs a different conditional block for the OP codes since the function call used in the regular case is not used.

### 3.2.6 Special J Type Instructions

There are a few special instructions that register as J Type instructions although they are not jump instructions. For example the BREAK instruction is a special instruction that tells the CPU to temporarily halt. This is useful for hardware debugging. Since the instruction is flat when this instruction is encountered the flat value is assembled. This is the same case for the NOP instruction. The only exception to this rule is the QUIT instruction which is not really an instruction but rather more of a debugging assembler directive. This is useful to halt the assembly of a file for different purposes. This was put there during debugging and development but never taken out due to its usefulness.

#### 3.2.7 Network Instructions

There are a few network type instructions that the assembler will parse directly. These include the SID, BCST, BCSTR, SMSG, and SMSGR. These are the CPU side network instructions and these are decoded in a particular way. SID stands for Set ID which allows the initialization of the ID of a CPU. This ID is extremely important if it is expected for the CPU to receive any messages or send any messages. SID is parsed as a J Type immediate instruction. First the number of arguments will identify that this is a J Type and then SID is processed and the instruction is assembled with the immediate converted to binary.