# TWO-DIMENSIONAL GRAPHICS CARD (GPU) ON AN ALTERA FPGA

A Design Project Report

Presented to the Engineering Division of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Master of Engineering (Electrical and Computer)

by

Peter Alexander Greczner

**Project Advisor: Dr. Bruce Land**

Degree Date: May, 2010

# Abstract

Master of Electrical and Computer Engineering Program

**Cornell University**

Design Project Report

Project Title: Two-Dimensional Graphics Card (GPU) on an Altera FPGA

Author: Peter Alexander Greczner

# Abstract:

This project realizes a simple graphics processing unit (GPU) on an FPGA which can be used as a GPU for Atmega microcontrollers to output graphics to a VGA display. An Altera Cyclone II FPGA will be used to implement the GPU. The FPGA and the host device will communicate via a RS-232 serial interface using a handshaking command structure to ensure accuracy of instruction delivery. Final output of the graphics will be displayed on a VGA compatible monitor. The result of the project is a GPU as well as VGA driver for the host device that allows a user to set up a graphical window to draw into and display on the VGA screen. The GPU supports multiple drawing functions such as text writing, line drawing, and rectangular fills. It also provides two different screen resolutions to draw into, 640x480 and 320x240, as well as capability for both single and double buffered graphics. The end product allows a simple method for one to use a microcontroller or other host device to create high quality graphical program without sacrificing memory, speed, or timing constraints of said microcontroller.

Report Approved by

Project Advisor: \_\_\_\_\_

# **1. Executive Summary**

A simple two-dimensional graphics processing unit (GPU) was implemented on an Altera Cyclone II FPGA. The GPU is capable of understanding 80bit instructions sequentially sent to it via RS-232 serial communication. The only requirement being from a user side is that they have installed the proper C files and have a means of sending a byte over serial. As instruction requests are handled, they are appropriately written into SRAM and later displayed on a VGA compatible monitor.

This GPU supports an extensible number of drawing modules since a common data-flow scheme is inherent to all modules. Current modules include the functionality for the drawing of lines, circles, rectangles, and polygons. As well as the filling of both circles and rectangles, and that of writing text to the monitor.

The GPU is also able to support four different drawing modes. The modes are first divided into what resolution the monitor displays. These are 640x480 pixels and 320x240 pixels. The second level of division is that of either single or double buffering. A frame buffer was implemented on the GPU to allow for a user to draw into a frame and not have the result displayed until they specify the update. This process eliminates flickering that one would see from constantly refreshing the same buffer. The single buffer mode was still included because it offers simplicity in some applications, specifically low-latency applications.

Color depth is supported up to 12bit RGB in the single buffered 320x240 drawing mode. Single buffer 640x480 and double buffer 320x240 support 8bit RGB. Double buffer 640x480 supports 4bit RGB.

A hardware serial receiver and transmitter module was implemented at a baud rate of 115200 to provide the communication between FPGA and host device. The serial communication supports 8bit data, 1 start bit, and 1 stop bit. There is no flow control, and parity check is done via a simple CRC of the packet, not byte by byte.

With a few minor modifications the GPU will provide the ability to draw into sprites and support multiple fonts. One goal of the project was to implement a method of downloading instructions into an instruction RAM (IRAM) and having a dedicated processor handle the graphics operations directly on the GPU. At the time of this report, that functionality is only partially implemented and still being tested and debugged.

The specific FPGA hardware used was the Altera Cyclone II DE2 EP2C35F672C6 development board.

# 2. Design Problem and Specifications

# 2.1 Design Problem Description

This project stemmed from addressing the problem of providing high resolution color graphics for constrained embedded applications, such as a microcontroller. In the situation such as a microcontroller you often need extra hardware to provide color graphics, but then you are still limited to memory constraints of the microcontroller. In situations without extra hardware you may be limited to black and white low resolution graphics over NTSC signal. Since many microcontrollers provide support for RS-232 serial communication, a question was posed of: can the graphics operations be offloaded via serial to a GPU, and how would that GPU hardware be realized?

The proposed solution to this problem was to have an FPGA act as the GPU co-processor to the embedded application and they would communicate via RS-232 serial.

# 2.2 Design Specifications

In development of the GPU the issues to address can be split into a few categories: performance parameters, functionality, communication, and end-user design.

# 2.2-1 *Performance Parameters*

Performance Parameters includes what the user can expect to achieve from the GPU. These are things such as frames per second and available resolutions.

| Performance Parameter | Design Specification |

|-----------------------|----------------------|

| Frames per second     | 10 fps               |

| Resolution 1          | 320x240              |

| Resolution 2          | 640x480              |

| Color Depth           | 16 predefined colors |

| Frame Buffers         | 2                    |

| Fonts                 | 1 downloadable (MIF) |

# 2.2-2 Drawing Functionality

- Shapes filled and unfilled (Circles, Rectangles, Polygons, and lines)

- Character display 8x8 pixel characters to be printable on the screen

- Sprites using MIF's allow for drawing into this frame

- Frames two full resolution frames

- Drawing queue queue of instructions that can be programmed to automatically get executed each frame instead of the microcontroller continuingly specifying

Originally the design specified that there would be hardware polygon manipulation, but as the development wore on it became apparent that hardware polygon manipulation is not something that should be a primary goal of a two-dimensional graphics card. Due to complicated issues in

implementation of other parts of the project, this idea was scrapped from the initial proposal, in favor of more completely developing the other aspects.

## 2.2-3 Communication

The communication between the FPGA and the microcontroller will take place over RS-232 serial protocol. The microcontroller will output a command to the FPGA who will receive and send either an ACK or NACK indicating successful or unsuccessful reception of the command.

## 2.2-4 End-user Design

The end-user will be able to write graphics by including a graphics module in their C program that contains all the code necessary to write to the FPGA. Graphics functions will have a simple English naming convention, such as fillRectangle(x1,y1,w,h,red,green,blue). An API will be available to explain in detail how to write to the FPGA and what methods are available.

# 3. Range of Solutions

# 3.1 Image Memory

With the goal of providing multiple resolution color graphics which could be displayed on a VGA compatible monitor, the choice of hardware solution was to be an FPGA. Other options such as color NTSC and an extra hardware chip were discounted as mentioned above. The next logical step was to decide on possible implementation approaches for aspects of the project.

One aspect of the project was where to store the image memory. The DE2 board allowed for four possible approaches to this image memory: SRAM, SDRAM, Flash, and M4K blocks. SRAM has 512Kbytes of memory, SDRAM has 8Mbytes, Flash has 4Mbytes, and there are 104 M4K (4Kbytes blocks) blocks. To support 16 colors (4 bits) in two frames at a resolution of 640x480 requires:

0.5bytes \* 640 pixels \* 480 pixels \* 2 frames = 307.2Kbytes

Ultimately SRAM was chosen, and below is a description of the other possible approaches strengths and weaknesses.

Each type of memory option has enough memory capable for storing both image frames. The next criteria is how easy it will be to access each type of memory, since the graphics card will constantly be reading and writing to the memory.

Flash memory isn't memory that is used in constant write operations since it has a limited number of write-erase cycles before it can no longer be used. Therefore, Flash memory was discounted.

The M4K blocks have an advantage that they could be individual accessible, in a grid like fashion, so parallel computation could be achieved on each region of the image. This would work well in the case of rectangle fills, which take the most processing times. However, functions such as line drawing would still be sequential in nature, and figuring out which M4K block to select would be difficult. One other disadvantage to M4K blocks is that 77 blocks would need to be used, and that would only leave 27 other blocks for extensible features of the GPU, such as Fonts or Sprites. The complexity of the M4K blocks along with the extra hardware resources they suffocated discounted them as the image memory choice.

SDRAM provides the most available memory for the images. It can also be dual ported for reads and writes. However, the disadvantage is that the reads and writes have to be done in large blocks. The hardware implementation for this type of memory is also very complex and based on the proposed design of the drawing modules, it did not appear to be an appropriate choice.

SRAM was chosen as the best option for this project because it provided a sufficient amount of memory without adding too much excess memory. It interfaced nicely with the VGA controller and was simple to write to in that it supported single cycle reads and writes. One disadvantage was that it was only single ported. However, this was deemed an acceptable sacrifice based on the other advantages SRAM posed in terms of designing the GPU drawing modules.

## 3.2 Communication

The first communication choice to make was RS-232 versus USB. USB was discounted because it would require extra hardware attachments to most, if not all, microcontrollers as well as complicated hardware on the FPGA. However, the transmission rate would be very high and much less than the transmission overhead that serial communication provides. But ultimately, RS-232 was chosen because of the probability that most microcontrollers support some form of serial communication and it would require the least amount of overhead. In my prior work on FPGA's I had developed a RS-232 hardware receiver and transmitter that needed some modifications and an overhaul to be more robust and accurate for this project, but ultimately the baseline hardware was in place which made that option advantageous also.

# 3.3 Video Display

To display the images on a screen there were two different options, to use NTSC television signals or to use VGA signals. NTSC was discounted in favor of VGA because the original intent of the project was to provide a user developing graphical applications on a microcontroller, such as in Cornell Engineering ECE 4760, the ability to have color graphics. The lab in which this class is held has an abundance of VGA compatible monitors as opposed to color NTSC compatible televisions. VGA provided the most practical approach and it was in line with the goal of the project.

# 3.4 Draw Mode Specific Modules versus Single Data Writing Module

There was the option of having a different drawing module for each of the drawing functions and for each of the drawing modes. For example in that case there would be a line drawer for 640x480 single buffer, double buffer, and 320x240 single buffer and double buffer. Then each of these modules would have their output muxed based on if they should have been in use based on the current instruction. The advantage to this is that writing to SRAM can be done directly within each module since each module knows exactly how it needs to read and write its data based on drawing mode. Therefore, for something like a 320x240 single buffer mode in which no reads are needed to be done in order to write data, cycles are saved.

The second option was having universal drawing modules that output coordinates and data to a data writing module. The data writing module knows what drawing mode it is in and writes accordingly. The disadvantage here is that each drawing module needs to issue a signal indicating that the data writer should write, and then it needs to listen for the data writer to signal that a write has finished. This adds up to five extra states to each write operation. The advantage though, is that it allows for easier extensibility of adding more drawing modules, and for easier debugging of current drawing modules, since you only need to work about one line drawer having an error, not four or more different line drawers having an error.

Ultimately the multiple drawing modules per drawing function method of data writing was discounted due to unnecessary increased hardware and lack of extensibility. The method of using a single data

writer, while adding more states, made it easiest to write data accurately based on the different modes, and provided a common interface for each drawing module to implement.

# 3.5 Purely Downloadable versus Serial Sequential

One option was to have the user download the entire graphics program into an instruction memory (IRAM) and have it run off of that. The benefit to this is that it would provide the fastest execution speed and possibly the best graphical results. However, the disadvantage is that of updating data on the fly while the microcontroller is running its applications. It was not clear how the GPU would handle interrupts and modify the program on the fly.

The alternative option was to have the graphics functions sent in line with the users host application. This is most similar to how graphics work on a PC application have the advantage of always having access to data used to create the graphics; i.e. no interrupts to change something in the DRAM of the processor, since the microcontroller/host sends the updated value within the instruction.

The end design of this project implemented the serial sequential approach and attempted to also implement the downloadable IRAM approach.

# 4. GPU Design

## 4.1 Overview

There are three levels of interaction in order to make the entire GPU application functional. There is the communication of instructions between host program and the GPU. There is the execution of the instruction within the GPU. Lastly, there is the displaying of the end result on the VGA monitor.

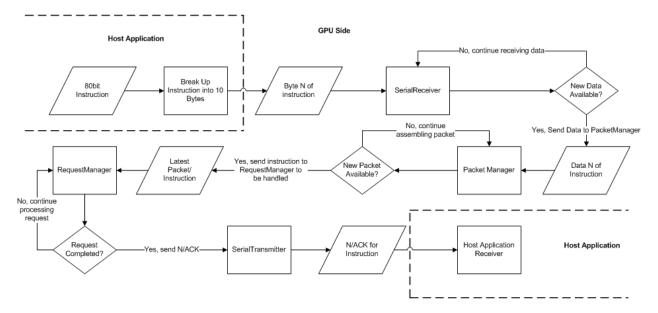

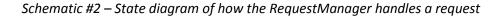

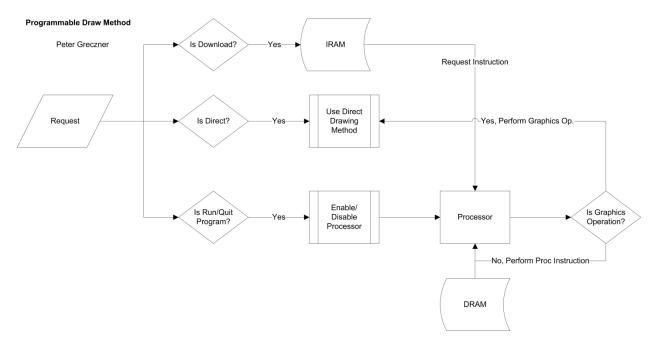

The general flow of information is that the host sends an instruction over serial to the GPU. The GPU processes the instruction, and sends a N/ACK back to the host. See Schematic #3 for an overview of the entire process.

# 4.2 Communication of Instructions

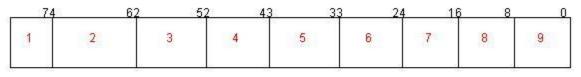

RS-232 was used as the method of communication of instructions between the host application and the GPU. The first issue that had to be resolved before any instructions could be sent was the issue of what comprises an instruction. The final instruction request is 80 bits long and a rationale for the length follows.

# Instruction Bit Description

- 1. Instruction, 6 bits, [79:74]

- 2. Color, 12 bits, [73:62]

- 3. X Position, 10 bits, [61:52]

- 4. Y Position, 9 bits, [51:43]

- 5. X end/width, 10 bits, [42:33]

- 6. Y end/height, 9 bits, [32:24]

- 7. Extra 1, 8 bits, [23:16]

- 8. Extra 2, 8 bits, [15:8]

- 9. Checksum, 8 bits, [7:0]

The GPU set out to support the following drawing functions: fills for both circles and rectangles, draws for circles, rectangles, and lines, text writing, frame updating, and setting the draw mode. These comprise a total of eight instructions. However, when designing the instruction parameters I felt that possibly I would need more than just three bits to represent the eight instructions should I find a need to extend the functionalities. Therefore I chose to use six bits to represent the type of instruction to be executed. Color is transmitted as 12 bits with four bits for each of the red, green, and blue components.

The x position and x end/width are 10 bits in length which is the minimum number of bits to represent a range of 0-640. The y position and y end/height are 9 bits in length which is the minimum number of bits to represent a range of 0-480. The checksum is a simple XOR of all packets sent to quickly check if anything wrong in transmission has occurred. The reason it is so simple is because at these transmissions speeds and at such a short transmission length, error probability is very minimal. Lastly the two interesting components are the Extra 1 and Extra 2 bytes. I included those in the original design should I need to extend functionality of something that I had not originally planned. In fact I ended up using these to represent signals when attempting to implement the downloading of instructions to the IRAM, as well as some bits to represent what current drawing mode we were in. The main purpose of these extra bytes was to keep the design flexible to extra additions.

For the RS-232 serial communication I decided to use a baud rate of 115200. The data sent was 1 byte at a time (8 bits) with one start bit and one stop bit. This meant that each byte required 10 total bits to transmit. The rationale for this choice is that it is the highest supported baud rate on the PC that I was testing the GPU on. At a baud rate of 115200 with each instruction comprising 80 bits, this means each instruction takes (8+1+1)\*10 = 100 bits to transmit. Minimum transmission of one instruction is 100/115200 seconds. To receive an acknowledgement of one byte takes (8+1+1)\*1 = 10 bits / 115200 seconds. Maximum total instructions that can be sent per second equals 1047.3. Note that this means that no actual execution on the GPU took place, just instruction to be sent and immediately have an N/ACK follow. This value of 1047.3 instructions per second (IPS) will scale with the baud rate, and since higher IPS means better framerate and that one can do more with graphics, the highest possible baud rate was chosen.

The process for sending an instruction from host to the GPU is as follows. The host breaks up the instruction into 10 bytes to be sent over serial to the GPU. The GPU SerialReceiver module is constantly listening for new data on the serial port. Once a new byte comes in, it sets a flag to indicate that a new byte of data is available. Listening to this flag is a PacketManager. The PacketManager is responsible for taking each new byte of data and placing it into the appropriate spot in the packet; essentially, reorganizing the instruction as the bytes come in. After the PacketManager has recreated the entire instruction into a single 80-bit packet, it raises a flag to indicate that a new packet is available to process. Listening to this flag is the RequestManager. The RequestManager is responsible for taking in each new request that a user has sent and processing it according to the requests specifications. Once the request has been processed the RequestManager signals the SerialTransmitter to transmit back a N/ACK to the host to indicate either successful or unsuccessful processing. Refer to Schematic #1 in the appendix for a visual flow explanation of the process.

To synchronize the baud rates between the GPU and the host application a module was created to generate the baudrate that the SerialReceiver uses to listen to instructions. Using the 50MHz clock it is not possible to directly derive a baudrate of 115200 through the use of a counter. Therefore one can only approximate the baudrate to around 115200. Over time a skew will cause the receiver to miss a bit of data that is transmitted. To correct for this most receivers listen at a factor of eight or more times the baudrate for a start bit and then resynchronize to the standard baudrate. This ensures that no start bits are missed and the amount of skew that will be evident over the 10 bits required to receive one byte of

data is negligible to caused missed data. Another baudrate generator is used to set the baudrate for the serial transmitter. This does not require a higher baudrate for listening, since the transmitter is only sending and it is the hosts duty to meet baudrate requirements.

## 4.3 Processing Instructions

## 4.3-1 Overview of Request Handling

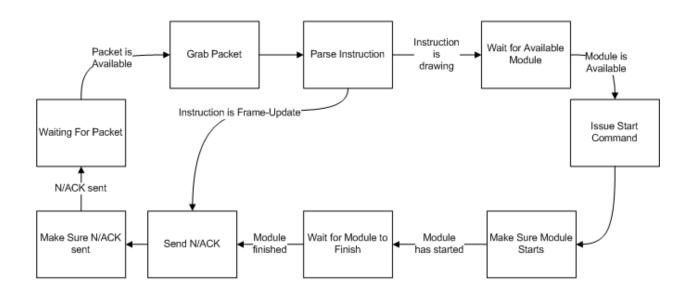

Once an instruction is received it is given to the RequestManager which is responsible for managing the instruction request until completion. The RequestManager has nine states which it uses to process an instruction. Its primary state is listening for a new request. Once a new request is noticed it "grabs" the packet from the PacketManager and the PacketManager then lowers its new packet flag because that packet is now in use. After the packet is grabbed, the RequestManager parses the 80-bit instruction into its different component registers. The values of these 9 registers are outputted from the RequestManager into the top level module to be read by the drawing functions. At this point the RequestManager decides if the current instruction is a drawing instruction or a frame-update instruction. If it is a frame-update instruction it proceeds to the completion stage and tells the serial transmitter to send an ACK back to the host. Otherwise, it decides which type of drawing instruction is going to be executed and waits for that module to acknowledge that it is free for use. Once the wanted module has acknowledge that it is ready for an instruction, the RequestManager sends a start command to that module to begin its processing. All other drawing modules remain idle at this time. The RequestManager then listens for the selected drawing module's availability flag, and once the module indicates it is available again, the RequestManager understands that the drawing instruction has completed. At this point the RequestManager then signals the serial transmitter to send an ACK of completion to the host. Refer to Schematic #2 in the appendix for a visual representation of this process.

# 4.3-2 Processing a Drawing Instruction

Each drawing module has an inherent identification number that specifies which type of drawing module it is. This is the same number that when an instruction comes in the six bits that specify the instruction correspond to. The RequestManager starts the drawing by outputting which ID of the drawing module it wants to use along with a start command. Then, only the drawing module who's ID matches that from the RequestManager will process the start command. All modules have the requisite drawing information available to them, but only the module that is wanted will begin the drawing function and set its current availability to unavailable.

Each module has a different function, but all have the same inherent structure to drawing. There are three basic stages to performing a drawing function. The first is to listen for the start command. Once this is received it begins its drawing loop and continues within this loop until completion in which it exits back to the listening for a start command state. Also within the drawing loop is a stage that performs a write to memory. Each time the module wants to write to memory it enters a specific state in which is sets the data to be written to memory and choose the x and y addresses. It then remains in this state

until a write is complete and then exits back to the loop. During the looping state the module sets itself as unavailable and in the listening for a start command state the module sets itself as available.

## 4.3-3 Handling a Data Write

To facilitate easier writing of data to memory based on what type of drawing mode is in use a DataWriter module was created. The purpose of this module is to properly pack the data into SRAM. Its other purpose is to separate memory functions from the drawing modules. This way drawing modules only need to worry about coordinates, in case memory specifications were to change, and thus they would not be affected in terms of functionality and performance.

Three muxes are implemented to feed the proper data into the DataWriter. These three muxes are for the X and Y Coordinates, and the color values. Each module sends a current value for each of these and the muxes select which one to output to the data writer based on which module the RequestManager has selected.

The DataWriter has four stages which include: waitForRequest, loadData, writeData, sendACK. In the waitForRequest state the DataWriter is listening for the drawing module to signal that it has data it wants to write. Once it receives this signal the DataWriter packages the color value appropriately so it can be written later into SRAM. In the loadData state, the DataWriter reads in from SRAM the current value of data at the address we want to write and modify data at. This is necessary since in some drawing modes data is packed more than one pixel per SRAM address. In the writeData state the DataWriter takes in the previously read data and modifies it with the data that the drawing module requested to be written and it writes this new data back into SRAM. Lastly, in the sendACK state, the DataWriter sends a signal back to the drawing module that the write has completed so the drawing module can continue on its operations.

The DataWriter is also responsible for refreshing the screen by listening for the coordinate request from the VGA controller.

### 4.4 Displaying to the VGA Monitor

To display to the VGA monitor a VGA controller written by Bruce Land is used to select which current pixel we want to read from SRAM and display on the screen. Based on the drawing mode in use and the pixel requested the data line is unpacked to get the correct pixel and then this fraction of data is repackaged and fed to the VGA red, green, and blue lines. The following code shows how each of the four drawing modes has their red, green, and blue color values unpacked from SRAM and repackaged based on the current Coord\_X and Coord\_Y (the outputs of the VGA controller) and then fed into the VGA color lines.

```

// Show SRAM on the VGA

//320x240 single frame

assign mVGA_R1 = {SRAM_DQ[15:12], 6'b0} ;

assign mVGA_G1 = {SRAM_DQ[11:8], 6'b0} ;

assign mVGA_B1 = {SRAM_DQ[7:4], 6'b0} ;

//640x480 - single frame

assign mVGA_R2 = (Coord_X[0]) ? {SRAM_DQ[15:13], SRAM_DQ[15:13], SRAM_DQ[15:13], 1'b1} :

{SRAM_DQ[7:5], SRAM_DQ[7:5], SRAM_DQ[7:5], 1'b1} ;

```

```

assign mVGA G2 = (Coord X[0]) ? {SRAM DQ[12:10], SRAM DQ[12:10],SRAM DQ[12:10],1'b1} :

{SRAM DQ[4:2], SRAM DQ[4:2],SRAM DQ[4:2],1'b1};

assign mVGA B2 = (Coord X[0]) ? {SRAM DQ[9:8],

SRAM DQ[9:8], SRAM DQ[9:8], SRAM DQ[9:8], SRAM DQ[9:8]} : {SRAM DQ[1:0],

SRAM DQ[1:0],SRAM DQ[1:0],SRAM DQ[1:0],SRAM DQ[1:0]};

//320x240 - double frame

assign mVGA R3 = ~readFrame ? {SRAM DQ[15:13], SRAM DQ[15:13],SRAM DQ[15:13],1'b1} :

{SRAM DQ[7:5], SRAM DQ[7:5], SRAM DQ[7:5], 1'b1};

assign mVGA_G3 = ~readFrame ? {SRAM_DQ[12:10], SRAM_DQ[12:10],SRAM_DQ[12:10],1'b1} :

{SRAM DQ[4:2], SRAM DQ[4:2], SRAM DQ[4:2], 1'b1};

assign mVGA B3 = ~readFrame ? {SRAM DQ[9:8],

SRAM_DQ[9:8], SRAM_DQ[9:8], SRAM_DQ[9:8], SRAM_DQ[9:8]} : {SRAM_DQ[1:0],

SRAM DQ[1:0], SRAM DQ[1:0], SRAM DQ[1:0], SRAM DQ[1:0]};

//640x480 - double frame

assign mVGA R4 = ~Coord X[0] ? (readFrame ? ({10{SRAM DQ[7]}}) : ({10{SRAM DQ[3]}})) : (readFrame

? ({10{SRAM DQ[11]}}) : ({10{SRAM DQ[15]}}));

assign mVGA G4 = ~Coord X[0] ? (readFrame ? ({5{SRAM DQ[6:5]}}) : ({5{SRAM DQ[2:1]}})) :

(readFrame ? ({5{SRAM_DQ[10:9]}}) : ({5{SRAM_DQ[14:13]}}));

assign mVGA B4 = ~Coord X[0] ? (readFrame ? ({10{SRAM DQ[4]}}) : ({10{SRAM DQ[0]}})) : (readFrame

? ({10{SRAM DQ[8]}}) : ({10{SRAM DQ[12]}}));

assign mVGA R = (drawMode == sixteenBit single 320x240) ? mVGA R1:

(drawMode == eightBit_single_640x480)

? mVGA R2:

(drawMode == eightBit_double_320x240)

? mVGA R3:

(drawMode == fourBit double 640x480) ? mVGA R4: 10'd0;

assign mVGA G = (drawMode == sixteenBit single 320x240) ? mVGA G1:

(drawMode == eightBit single 640x480)

? mVGA G2:

(drawMode == eightBit_double_320x240)

? mVGA G3:

(drawMode == fourBit double 640x480) ? mVGA G4: 10'd0;

assign mVGA B = (drawMode == sixteenBit single 320x240) ? mVGA B1:

(drawMode == eightBit single 640x480)

? mVGA B2:

? mVGA_B3:

(drawMode == eightBit_double_320x240)

(drawMode == fourBit double 640x480) ? mVGA B4: 10'd0;

```

### 4.5 Drawing Modules

All drawing modules follow the same basic "protocol" in terms of what data they receive, how they process and what they output.

Common to all modules are that they receive an initial (X,Y) coordinate starting point and they receive some sort of clarifier point or points. The clarifier could be a width and height for rectangles, a radius for the circles, and end (X,Y) point for a line, etc. They also take in color data for what color they need to draw presently. Each drawing module, as mentioned earlier, also has its own ID to identify itself. Also common to all modules are that they output an (X,Y) address for drawing as well as a data value to write to that (X,Y) address. The drawing modules output a signal to notify if they are currently available or not. Lastly, the drawing modules output a write clock for use of the DataWriter and take in a flag from the DataWriter indicating if a write has finished. See the appendix for further description on all inputs and outputs of each drawing module.

Below is a presentation of the different drawing algorithms.

### 4.5-1 Rectangle Fills and Draws

The rectangle fill works by starting at the starting coordinate (X,Y) and iterating across X and down Y until the coordinate (X+width,Y+height) is reached. Each pixel is written sequentially. In hindsight I

realized I could have designed the 640x480 version to fill two pixels at once since it is double packed and that would cut fill completion time in half for that scenario of single buffered 640x480.

The rectangle draw works by iterating over each wall of the rectangle, north, south, east, and west.

These fills only support a single color fill, however an extension to the modules is possible if one were to use one of the extra fields of the instruction to specify an end color and a gradient effect could be achieved with minor modifications to the color data output of the modules.

# 4.5-2 Circle Fills and Draws

Circles are drawn using the Bresenham circle drawing algorithm which breaks up the circle into eight quadrants in which the edges of the circle can be formed. Then using symmetry it loops through the algorithm to form the exterior of the circle.

To fill a circle, the 8 different quadrants are paired to their symmetric partner across the vertical axis. The partner on the left specifies a start point, and since Bresenham is symmetric, the other partner specifies an end coordinate that is on the same Y line. Then the algorithm iterates from  $(X_{p1}, Y)$  to  $(X_{p2}, Y)$ , where p1 and p2 are the partner pairing of the quadrants.

Originally I attempted to have the circle fill module output an  $(X_1, Y_1)$  and  $(X_2, Y_2)$  points to the line drawing module, but this made things unnecessarily complicated and introduced numerous communication and timing constraints and problems. Eventually I realized that because the quadrants were paired on the same horizontal, a simple loop would be sufficient for the fills.

# 4.5-3 Line Drawing

Lines are drawn using the integer Breshenham line drawing algorithm. This module was modified for this project and adapted from a laboratory exercise in ECE 5760. Refer to the appendix for pseudo-code of the line drawing algorithm.

# 4.5-4 Text Writing

The TextWriter module is responsible for writing characters to the string. A .MIF file containing 256 ASCII 8x8 characters is downloaded into ROM. The TextWriter addresses into this ROM based on which character the instruction specifies. It then loops across the 8x8 character which consists of 1's and 0's. A 1 indicates to draw a pixel, and a 0 indicates to ignore.

Future modification to this file could have the instruction specify the type of font being used and instead of looping across 8x8, it loops across WxH where W is the width and H is the height of the font in use.

# 4.5-5 Sprite Drawing (in progress)

Drawing into a sprite was attempted in this project. At the current time of this report that work is still in progress. The way it works is that a sprite is represented by a 32x32 pixel, 8 bit color RAM module. A drawing instruction that comes in specifies that you want to draw into a certain sprite and instead of

feeding the X,Y coordinate and data into the DataWriter module, it muxes the information into the Sprite RAM. To draw the sprite on the screen the sprite must be enabled and have a valid (X,Y) screen coordinate. Then when the VGA controller is looping through the coordinates to display on the monitor, the sprite module checks to see if its boundaries corresponds to that pixel and if it does, it immediately draws on the screen instead of grabbing from SRAM.

# 4.6 Instruction Download and GPU Processor Mode

An original attempt of the project was to provide a processor to program and download the instructions directly into an instruction queue of the GPU. The idea was to eliminate the serial overhead, except for the one time downloading of instructions, and have the entire program run locally on the GPU, similar to the nVidia CUDA architecture. However, issues with the normal drawing methods delayed the start of this part of the project, and at the time of the report it is only partially implemented and not fully tested. However, an explanation of what was done follows.

The processor that was created was a simple single cycle microprocessor that supported functions such as branches, ALU ops, jumps, loads, stores. It had an IRAM and DRAM as well. A full list of all instructions is included in the appendix.

When the RequestManager received a request it is decided whether this is a real-time request (should be directly drawn on the screen) or if this is a processor specific request, such as an instruction download. If it is a download, the RequestManager loads the current request into IRAM at a PC specified by the instruction. The value of this PC was supposed to come from a "compiler" that I would have written. The RequestManager also listens for a start processor command and when it receives that it enables to GPU Processor mode and goes to the PC = 0 to start the downloaded program. Execution then continues within the processor until the user specified an exit point, if there was one.

The processor itself is a standard single cycle microprocessor with some modifications to adapt to the GPU's drawing functions. The processor maintains its own PC and outputs that to IRAM which returns the instruction back into the processor. The processor then decodes the instruction. If it decides that the instruction is a non-drawing function, it continues to the ALU operation stage and then into the memory and writeback stage. However, if it is a drawing operation a flag is thrown to indicate that we need to stall the processor and execute a drawing instruction. The information for this instruction is then created and sent to the direct drawing method in which it is executed. At the end of execution a flag is returned to the processor indicated that all drawing has completed. The GPU processor is then enabled and continues on its operations.

A visual representation of this process is included in the appendix by the name of Schematic #4.

# 4.7 Graphics Library in C

A graphics library has been written in the C programming language to facilitate communication with the GPU over serial. It provides instructions for drawing each of the type of graphics functions and it packages up the instructions into the appropriate bytes and is able to send them out over serial. The

only modification one needs to make to any of these files would be if the serial communication is different for your specific process. Mine uses methods like writeByte, where one may want to use something like fprintf instead. These are trivial changes and only need to be changed in one line of code in the send instruction method. A list of instructions is included in the appendix along with an explanation of how they work. A simple example of how to draw something to the GPU is as follows:

This piece of code first sets the type of drawing mode that we want the GPU to run, and that is a single buffer 640x480 image. It then does a sequence of rectangular fills, line draws, and text writing. What is nice about the code is that as long as the communication is set up in the underlying graphics library, the user only has to worry about simple functions such as fillRectangle in their main application code.

### 4.8 Timing Issues

One of the major challenges of this project was numerous timing issues that I had to deal with. Almost every single module was clocked and not every module used the same clock to process its data. The serial modules ran on a clock equal to the baudrate. The drawing functions ran on the VGA control clock that is used to drive the VGA controller. Other clock signals were generated artificially from within some modules, such as the signal to grab a packet, or send a N/ACK to the transmitter. One more factor to complicate things is that the VGA controller needs to read from SRAM to refresh the screen, and when this is happening, no processing can be done in the form of writing to SRAM from one of the drawing modules. This loss of synch causes some modules to pause, while others need not pause because they don't depend on VGA synch complications. This skew in some modules needing to pause while others were free to run caused some initial problems in having every module communicate smoothly. This is because sometimes an artificial clock signal would be lost during a loss of synch. These issues were resolved through careful debugging and testing of the code to find complications of this type. One thing that this project certainly helped me understand is how important meeting timing requirements and understanding the timing of a system is to system performance.

# 5. Results and Conclusions

# 5.1 Original Goal Completion

Of the original goals of the project this GPU was successful in implementation of the following:

- Multiple resolution support, 320x240 and 640x480

- Color depth support, at least 16 colors in worst case palette

- Two frame buffers

- Multiple drawing functions, lines, circles, rectangles, text, and polygons

- Font support, 1 8x8 downloadable font

- 10 FPS, successful in some applications; is application dependent

Of the original goals of the project this GPU was partially successful in implementation of the following:

- Sprite support, functionality was created but not finished

- Programmable Interface, the processor was created but not fully tested and implemented

# 5.2 Testing the GPU

The GPU performed a multitude of tests to check for accuracy of drawing algorithms, communication of instructions, and to measure overall performance (such as IPS and FPS).

# 5.2-1 Accuracy of Drawing Algorithms

Tests were done in each of the four drawing modes on each of the different drawing modules. The criterion in testing was to see if the modules drew their function correctly. For fills this meant that every interior point was filled, and for the text writer, this meant that the proper character was written to the string. These tests also checked that the objects were drawn at the correct location on the screen.

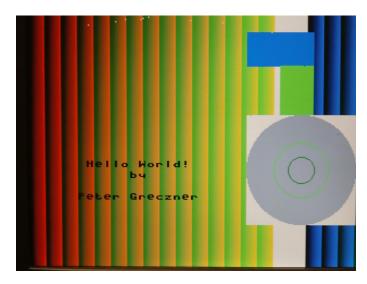

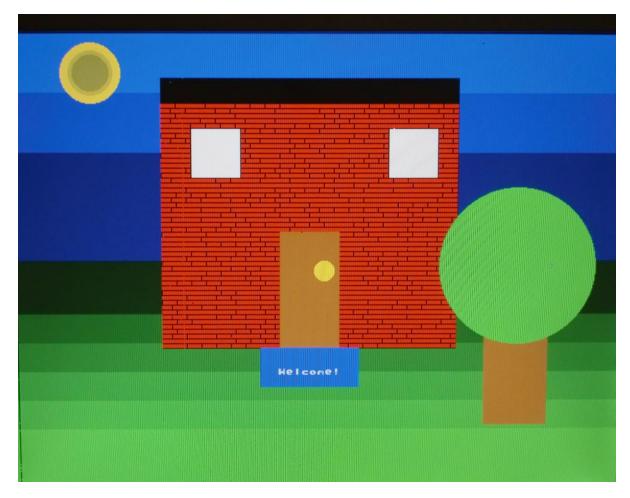

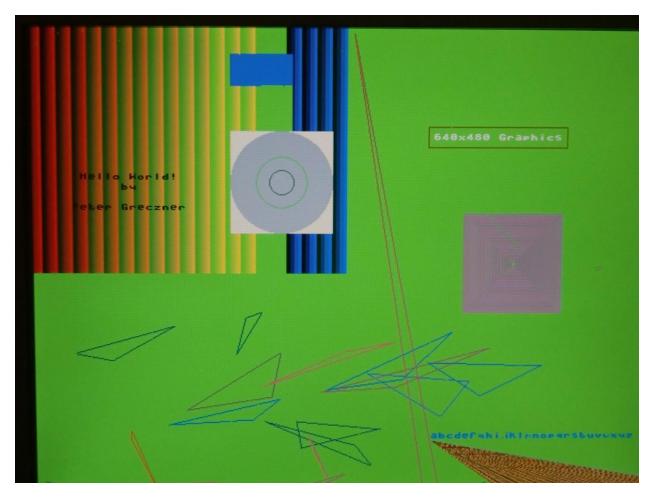

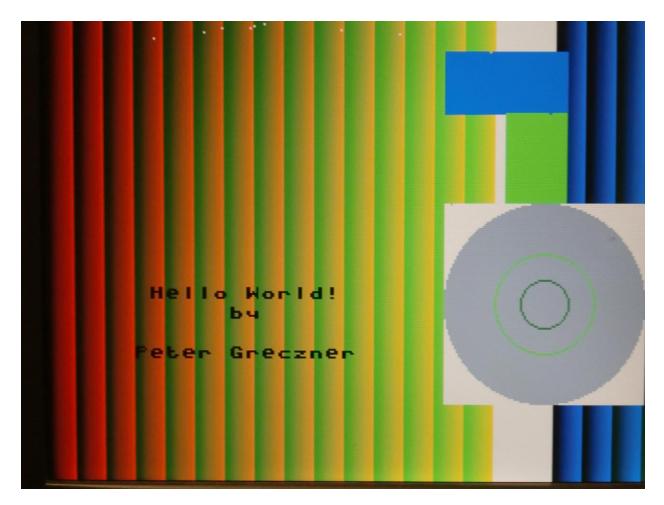

Figure – 320x240 Accuracy of Drawing Algorithm Test

There were two functions that did not work perfectly and a solution could not be found for these functions. The first is that the circle and rectangle fills would occasionally miss one pixel to draw. The likely explanation for this problem is a time/synchronization problem that results in one pixel not being written to SRAM. The other problem was with the text writing module which would occasionally write errant pixels to the screen. This problem was caused by the text writing module reading lines with a one cycle lag from the request. This would cause the last line of the previous character to be the first line of the next character. No problems occur when the last line is blank, but for a hanging letter such as 'g' or 'j', a bar would be drawn on top of the following character. This problem was resolved by introducing an extra line request when the command is sent from the RequestManager.

Figure – Scene created in 640x480 resolution to show off all drawing functions

# 5.2-2 Performance Tests

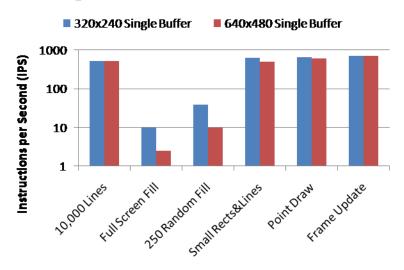

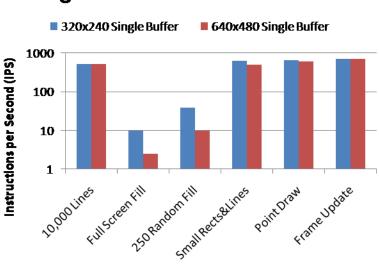

A few performance tests were run to see the speed at which the GPU could execute instructions. The theoretical max for best performance was 1047.3 instructions per second (IPS). To see what the real IPS is for the GPU the following tests were run and execution time was measured in all cases:

- 10,000 Lines 10,000 random lines were drawn, used to represent where one might be drawing a lot of polygons

- Full Screen Fill 100 full screen rectangle fills were performed, used to represent most extreme of drawing cases

- Random Fill 250 rectangles of random size were filled on the screen, use to represent a high stress drawing application that constantly erasing parts of the screen

- Small Rectangles and Lines 1000 rectangles and lines were drawn on the screen, use to represent an average type of drawing someone might do

- Point Draw 5000 single point instructions, used to represent the least intensive of actual drawing instructions

• Frame Update – 5000 frame updates were performed, used to represent the equivalent of a NOP to find the real peak IPS for this GPU

# **Single Buffer Performance Tests**

Figure – Shows the performance in terms of IPS for Single Buffer tests

The result of the test show that in most cases the IPS for the GPU peaks around the 800 IPS range. The outliers are the computationally heavy in terms of memory write tests of full screen rectangle fills and many random rectangle fills. However in the tests used to represent what an aggregate application might use, such as the Small Rects and lines, a high IPS was achieved.

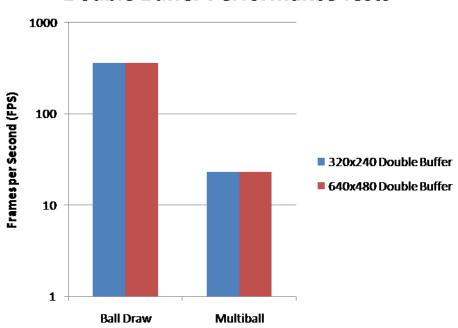

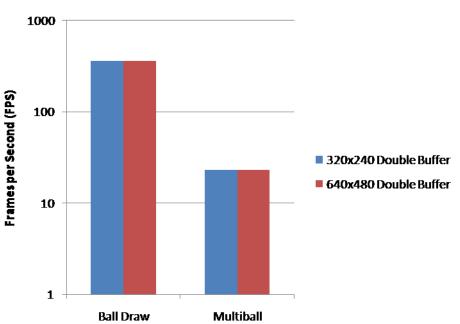

To test the double buffered performance two simple tests were run, one in which a single bouncing ball was updated, and the second in which ten bouncing balls were updated and refreshed on the screen.

# **Double Buffer Performance Tests**

Figure – Double buffer FPS test

The result was that in the case of 10 balls bouncing on the screen an FPS of around 10 could be achieved. This was within the original goal of the project.

### 5.3 Conclusions

The GPU was extremely successful in completing many of the goals of the original proposal and made good progress towards completion of the last few goals. I believe that the current state of the GPU would work best for low-latency applications or those in which full screen fills do not occur often. Since IPS peaks around 800, this means that your FPS could significantly vary depending on the type of application you want to write. If your application requires 1000 instructions per frame to be executed, then it simply will not be possible to achieve an FPS better than 1, and hopefully the application is low-latency refresh, such as just printing data to the monitor. However, if your application is very simple, or you implement your graphics algorithm in an intelligent way (i.e. only refreshing areas that have been written too, instead of the whole screen) a high FPS is possible. Basically, the GPU cannot guarantee a certain minimum FPS as I had originally intended it too due to serial overhead limitations.

However, I am not sure that that is a bad thing at all. Leaving the design up to the user to decide how to best implement the graphics is not a bad component of the project. Also, although the GPU cannot guarantee an FPS of 10, that does not mean that an FPS of 10 is not possible; it certainly is.

What I also believe works well in this project is the room for extension. The modules of the project were created in a way that could allow for easy future expansion of new drawing functions. From the

beginning in which I added the two Extra 1 and Extra 2 fields should new functions arise, and the general extensible nature of the drawing modules in which they all follow a specific protocol, can make it easy for someone to take this project and make even more functionality.

Ultimately, this project did not implement the instruction queue and processor functionality to completion. Had that processor gotten to the working stage I truly believe the results would have been some high quality and high speed graphics. That isn't to take away from the serial sequential method which performs well, but future work in implementing the programmable processor could make this GPU an even more attractive option.

This project set out to realize a two-dimensional graphics card on an FPGA that could be used as a GPU for host devices such as microcontrollers in order to provide those applications with color graphics on a VGA compatible monitor. This goal was met.

# 6. Appendix

#### 6.1 Schematics

**Communication Flow Schematic**

Schematic #1 – Overview of the communication between host and GPU

## RequestManager State Machine

Schematic #4 – The programmable flow method data flow schematic

#### 6.2 Images and Results

Double Buffer Performance Tests

Double Buffer Performance Tests

# **Single Buffer Performance Tests**

Single Buffer Performance Tests

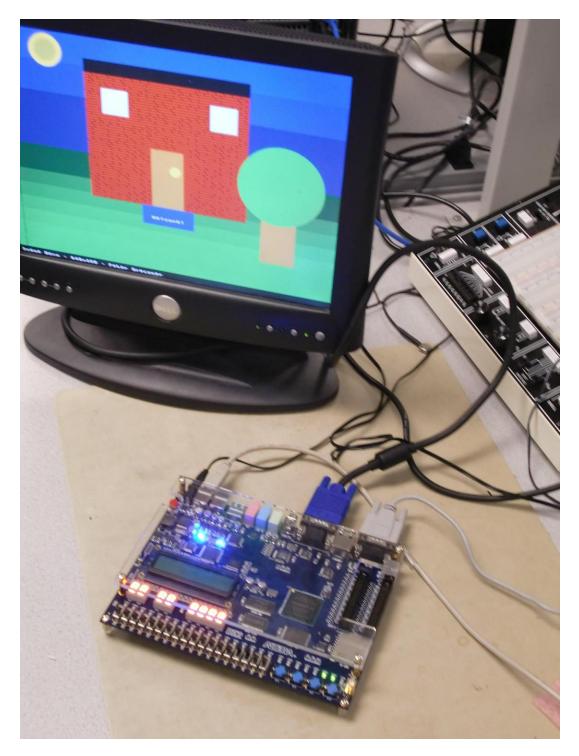

GPU running on FPGA and outputting to VGA monitor

640x480 Scene Test

640x480 Drawing function Test

320x240 Drawing Function Test

# 6.3 Module Descriptions

- *availableMux.v*: muxes the availability bits of all the drawing modules based on a select bit from the RequestManager

- *BaudGenerator.v:* generates the baud clock for the serial communication

- BaudGenerator\_8Times.v: generates a baud clock at 8 times the required speed

- *circle\_draw.v:* draws a circle on the screen

- *circle\_fill\_better.v*: fills a circle on the screen

- *Color\_MUX*.v: muxes all of the color data from the drawing modules based on a select bit from the RequestManager

- *CRC.v:* computes the XOR of the packet to create a CRC

- DataWriter.v: writes the current data to SRAM

- *font1\_rom*.v: the 8x8 font ROM

- *line\_drawer*.v: draws a line on the screen

- *PacketManager\_updated.v*: the packet manager that collects the instruction as it receives the individual parts from the SerialReceiver

- *RequestManager\_updated.*v: manages all the requests that come in from the host device and processes them accordingly

- *SerialReceiver\_improved\_fastClock.v*: the serial receiver module

- SerialTransmitter\_updated.v: the serial transmitter module

- square\_draw.v: draws a square on the screen

- *square\_fill.v:* fills a square on the screen

- *TextWriter.v:* writes text to the screen

- TransmitClock.v: artificial clock used to grab a packet

- *Xaddr\_MUX.v:* mux for the x address data that muxes based on a select bit from the RequestManager

- *Yaddr\_MUX.v:* mux for the yaddress data that muxes based on a select bit from the RequestManager

## 6.4 Software User Guide

# 6.4-1 Function Library and Description

The following functions have been created in the C graphics library:

void fillRectangle(int x, int y, int w, int h, int r, int g, int b);

Use: fills a rectangle on the screen with the specified color, width, and height at (x,y)

Parameters:

x = starting x coordinate y = starting y coordinate w = width of rectangle h = height of rectangle r = red color (0-15) g = green color (0-15) b = blue color (0-15)

void fillCircle(int x, int y, int r, int red, int green, int blue);

Use: fills a circle on the screen with the specified color, and radius at (x,y)

Parameters:

x = starting x coordinate y = starting y coordinate r = radius red = red color (0-15) green = green color (0-15) blue = blue color (0-15)

void drawRectangle(int x, int y, int w, int h, int r, int g, int b);

Use: draws a rectangle on the screen with the specified color, width, and height at (x,y) Parameters: x = starting x coordinate y = starting y coordinate w = width of rectangle h = height of rectangle r = red color (0-15) g = green color (0-15) b = blue color (0-15)

void drawCircle(int x, int y, int r, int red, int green, int blue);

Use: draws a circle on the screen with the specified color, and radius at (x,y)

Parameters:

x = starting x coordinate y = starting y coordinate r = radius red = red color (0-15) green = green color (0-15) blue = blue color (0-15)

void drawLine(int x1, int x2, int y1, int y2, int r, int g, int b);

Use: draws a line from (x1,y1) to (x2,y2) with the specified color

Parameters:

x1 = point 1 of line x coordinate x2 = point 2 of line x coordinate y1 = point 1 of line y coordinate y2 = point 2 of line y coordinate r = red color (0-15) g = green color (0-15) b = blue color (0-15)

void drawChar(int x1, int y1, int charVal, int r, int g, int b);

Use: draws a character on the screen at (x1,y1) with the specified color

Parameters:

x1 = starting x coordinate of character y1 = starting y coordinate of character charVal = the ascii character value (0-255) r = red color (0-15) g = green color (0-15)

b = blue color (0-15)

y1 = starting y coordinate of string \*string = pointer to character array r = red color (0-15) g = green color (0-15) b = blue color (0-15)

\*y = integer array of the y points of the polygon

\*y = integer array of the y points of the polygon

elems = number of elements in \*x and \*y arrays

r = red color (0-15)

g = green color (0-15)

b = blue color (0-15)

*void writeInstruction(int PC, char a, char b, char c, char d, char e, char f);* Use: to write an instruction into IRAM

void startProgram(void); Use: to start execution of the IRAM program

void startDownload(void); Use: to start downloading into IRAM

void finishDownload(void); Use: to signal finish downloading into IRAM

void frameUpdate(void);

Use: to update to the current frame and switch to drawing into alternate frame

void setDrawMode(int dm);

Use: sets the drawing mode

Parameters:

dm = the drawing mode...

\*M16bit\_SINGLE\_320x240: single buffer 320x240 image

\*M8bit\_SINGLE\_640x480: single buffer 640x480 image

- \*M8bit\_DOUBLE\_320x240: double buffer 320x240 image

- \*M4bit\_DOUBLE\_640x480: double buffer 640x480 image

void sendInstruction(int \*instr);

Use: sends an instruction over serial to the GPU

Parameters:

\*instr = integer array of the instruction to be sent

int computeChecksum(int \*packet);

Use: computes a checksum of the current instruction to be sent

Parameters:

\*packet = current packet of instruction to be sent

#### 6.4-2 Example Program

```

#include <stdio.h>

#include "rs232.h"

#include "globals.h"

#include "Graphics Functions.h"

#include <time.h>

//This program draws a simple scene of a house in a field

int main(int argc, char **argv)

{

int error;

int test_num = -3;

printf("args %i\n",argc);

if(argc > 1)

test num = atoi(argv[1]);

printf("Serial Communication in C\n");

printf("Opening Comport: COM1\n");

error = OpenComport(0, 115200);

if(error) {

printf("Failed!!! Exiting\n");

return 0;

}

unsigned char result;

result = 0;

int gray = 1;

while (gray == 1 && test num != 24)

gray = PollComport(0,&result,1); //to flush out initial data

setDrawMode(M8bit_SINGLE_640x480);

fillRectangle(0,0,640,480,0,0,0);

int sky = 0;

int skyc = 15;

double dskyc = 1.0/230.0;

for(sky = 1; sky < 230; sky ++)

{

if((sky % 15) == 0) skyc --;

drawLine(0,640,sky,sky,0,0,max(skyc,4));

printf("(int)skyc: %i\n",skyc);

}

int grass = 0;

int grassc = 0;

double dgrassc = 1.0/250.0;

for(grass = 230; grass <= 479; grass ++) {</pre>

if((grass % 15) == 0) grassc ++;

drawLine(0,640,grass,grass,0,max(grassc,2),0);

}

fillRectangle(320-150,320-250,300,250,12,0,0);

int brick = 0;

for(brick = 320; brick >= (320-250); brick -=5)

{

drawLine(170,470,brick,brick,0,0,0);

int x;

for (x = 170 + (brick 2) * 10); x < 470; x += 15)

```

```

if((rand()/(float)RAND MAX) <= .5)</pre>

{

if(brick <= 315)

{

drawLine(x,x,brick,brick+5,0,0,0);

}

}

}

fillRectangle(320-150,320-250-25,300,25,0,0,0);

fillRectangle(320-30,320-120,60,120,9,5,0);

fillCircle(320+15,320-80,10,15,15,0);

fillRectangle(320-120,320-225,50,50,15,15,15);

drawRectangle(320-120,320-225,50,50,0,0,0);

fillRectangle(320+80,320-225,50,50,15,15,15);

drawRectangle(320+80,320-225,50,50,0,0,0);

fillRectangle(500,400-165,65,165,9,5,0);

fillCircle(533,400-165,80,0,12,0);

fillRectangle(320-50,320,100,40,0,0,15);

drawString(320-8*4,340,"Welcome!",15,15,8);

int sun = 0;

for(sun = 15; sun >= 8; sun --)

fillCircle(100,40,sun*2,sun,sun,0);

drawString(10,470,"Scene Demo - 640x480 - Peter Greczner",15,15,15);

```

#### 6.5 Drawing Algorithm Reference

```

6.5-1 Bresenham Line Drawing Algorithm (pseudo-code)

```

```

function line(x0, x1, y0, y1)

boolean steep := abs(y1 - y0) > abs(x1 - x0)

if steep then

swap(x0, y0)

swap(x1, y1)

if x0 > x1 then

swap(x0, x1)

swap(y0, y1)

int deltax := x1 - x0

int deltay := abs(y1 - y0)

int error := deltax / 2

int ystep

int y := y0

if y0 < y1 then ystep := 1 else ystep := -1

for x from x0 to x1

if steep then plot(y,x) else plot(x,y)

error := error - deltay

if error < 0 then</pre>

y := y + ystep

error := error + deltax

[1] http://en.wikipedia.org/wiki/Bresenham%27s_line_algorithm#Optimization

```

#### 6.5-2 Bresenham Circle Drawing Algorithm (pseudo-code)

```

void circle(int xc, int yc, int r)

{

int x = 0;

int y = r;

int p = 3 - 2 * r;

while (x <= y)</pre>

```

```

{

putpixel(xc + x, yc + y, getcolor());

putpixel(xc - x, yc + y, getcolor());

putpixel(xc + x, yc - y, getcolor());

putpixel(xc - x, yc - y, getcolor());

putpixel(xc + y, yc + x, getcolor());

putpixel(xc - y, yc + x, getcolor());

putpixel(xc - y, yc - x, getcolor());

if (p < 0)

p += 4 * x++ + 6;

else

p += 4 * (x++ - y--) + 10;

}

</pre>

```

[2] http://gamebub.com/cpp\_algorithms.php#circle

#### 6.6 Processor ISA Opcodes

| Instruction Name | Op Code |

|------------------|---------|

| Add              | 100000  |

| Subtract         | 100001  |

| Shift Left       | 100010  |

| Shift Right      | 100011  |

| OR               | 100100  |

| NOR              | 100101  |

| AND              | 100110  |

| NAND             | 100111  |

| XOR              | 101000  |

| BGT              | 101001  |

| BLT              | 101010  |

| BGE              | 101011  |

| BLE              | 101100  |

| BEQ              | 101101  |

| BNE              | 101110  |

| BEZ              | 101111  |

| BNEZ             | 110000  |

| J                | 110001  |

| JR               | 110010  |

| LD               | 110011  |

| ST               | 110100  |

| Circle Fill      | 000000  |

| Circle Draw      | 000001  |

| Square Fill      | 000010  |

| Square Draw      | 000011  |

| Line Draw        | 000100  |

| Text Write       | 000101  |

| Frame Update     | 000110  |

| ADDI | 110101 |

|------|--------|

| SUBI | 110110 |

| SLI  | 110111 |

| SRI  | 111000 |

| NOT  | 111001 |

| JAL  | 111010 |

# 6.7 Code Reference

//globals.h

#define CIRCLE\_FILL 0

#define CIRCLE\_DRAW 1

#define SQUARE\_FILL 2

#define SQUARE\_DRAW 3

#define LINE\_DRAW 4

#define TEXT\_WRITE 5

#define FRAME\_UPDATE 6

#define FRAME\_SWITCH 6

#define DRAW\_MODE 7

#define START\_DOWNLOAD 8

#define FINISH\_DOWNLOAD 15

#### //Drawing Modes

#define M16bit\_SINGLE\_320x240 0

#define M8bit\_SINGLE\_640x480 1

#define M8bit\_DOUBLE\_320x240 2

#define M4bit\_DOUBLE\_640x480 3

#define PACKET\_LENGTH 10

#define DIRECT 0

#define LOAD 1

```

//Graphics_Functions.c

#include "Graphics_Functions.h"

#include "globals.h"

#include "rs232.h"

#include <string.h>

int packet[] = {0,0,0,0,0,0,0,0,0,0,0;};

int instruction[] = {0,0,0,0,0,0,0,0,0};

int frame sel = 0;

int draw_mode = M16bit_SINGLE_320x240;

void fillRectangle(int x, int y, int w, int h, int r, int g, int b)

{

instruction[0] = SQUARE_FILL;

instruction[1] = r*256 + g*16 + b;

instruction[2] = x;

instruction[3] = y;

instruction[4] = w;

instruction[5] = h;

instruction[6] = (draw_mode << 5) + (frame_sel << 3);</pre>

instruction[7] = 0;

sendInstruction(instruction);

}

void fillCircle(int x, int y, int r, int red, int green, int blue)

{

instruction[0] = CIRCLE_FILL;

instruction[1] = red*256 + green*16 + blue;

instruction[2] = x;

instruction[3] = y;

instruction[4] = r;

instruction[5] = 0;

instruction[6] = (draw_mode << 5) + (frame_sel << 3);</pre>

instruction[7] = 0;

sendInstruction(instruction);

}

void drawRectangle(int x, int y, int w, int h, int r, int g, int b)

{

instruction[0] = SQUARE_DRAW;

instruction[1] = r*256 + g*16 + b;

instruction[2] = x;

instruction[3] = y;

instruction[4] = w;

instruction[5] = h;

instruction[6] = (draw_mode << 5) + (frame_sel << 3);</pre>

instruction[7] = 0;

```

```

sendInstruction(instruction);

```

```

void drawCircle(int x, int y, int r, int red, int green, int blue)

{

instruction[0] = CIRCLE_DRAW;

instruction[1] = red*256 + green*16 + blue;

instruction[2] = x;

instruction[3] = y;

instruction[4] = r;

instruction[5] = 0;

instruction[6] = (draw_mode << 5) + (frame_sel << 3);</pre>

instruction[7] = 0;

sendInstruction(instruction);

}

void drawLine(int x1, int x2, int y1, int y2, int r, int g, int b)

{

instruction[0] = LINE_DRAW;

instruction[1] = r*256 + g*16 + b;

instruction[2] = x1;

instruction[3] = y1;

instruction[4] = x2;

instruction[5] = y2;

instruction[6] = (draw_mode << 5) + (frame_sel << 3);</pre>

instruction[7] = 0;

sendInstruction(instruction);

}

void drawPolygon(int *x, int *y, int elems, int r, int g, int b)

{

int i;

for(i = 1; i < elems; i ++)</pre>

{

drawLine(x[i],x[i-1],y[i],y[i-1], r, g, b);

printf("drawing line from (%d,%d) to (%d,%d)\n",x[i],y[i],x[i-1],y[i-1]);

}

if(elems >= 2)

drawLine(x[elems-1],x[0],y[elems-1],y[0], r, g, b);

printf("drawing line from (%i,%i) to (%i,%i)\n",x[elems-1],y[elems-1],x[0],y[0]);

}

void drawChar(int x1, int y1, int charVal, int r, int g, int b)

{

instruction[0] = TEXT_WRITE;

instruction[1] = r*256 + g*16 + b;

instruction[2] = x1;

instruction[3] = y1;

instruction[4] = charVal >> 2;

instruction[5] = (charVal & 0x3) << 2;</pre>

instruction[6] = (draw_mode << 5) + (frame_sel << 3);</pre>

instruction[7] = 0;

```

}

```

sendInstruction(instruction);

}

void writeInstruction(int PC, char a, char b, char c, char d, char e, char f)

{

instruction[0] = a;

instruction[1] = b;

instruction[2] = c;

instruction[3] = d;

instruction[4] = e;

instruction[5] = f;

instruction[6] = PC >> 4;

instruction[7] = (((PC\&0xF) << 4) | 0x0F);

sendInstruction(instruction);

}

void startProgram(void)

{

int i;

for(i = 0; i < 8; i ++) instruction[i] = 0xFF;</pre>

sendInstruction(instruction);

}

void startDownload(void)

{

instruction[0] = START_DOWNLOAD;

sendInstruction(instruction);

}

void finishDownload(void)

{

instruction[0] = FINISH_DOWNLOAD;

sendInstruction(instruction);

}

void frameUpdate(void)

{

instruction[0] = FRAME SWITCH;

sendInstruction(instruction);

switch(draw_mode)

{

case M16bit_SINGLE_320x240:

frame_sel = 0;

break;

case M8bit_SINGLE_640x480:

frame_sel = 0;

break;

case M8bit DOUBLE 320x240:

frame_sel = (frame_sel == 0) ? 1 : 0;

break;

case M4bit_DOUBLE_640x480:

frame_sel = (frame_sel == 0) ? 1 : 0;

break;

}

}

void setDrawMode(int dm)

```

{

```

draw_mode = dm;

instruction[0] = DRAW_MODE;

instruction[6] = (draw_mode << 5) + (frame_sel << 3);</pre>

//sendInstruction(instruction);

}

void drawString(int x1, int y1, char *s, int r, int g, int b)

{

int i = 0;

for(i = 0; i < strlen(s); i ++)</pre>

{

int charVal = s[i]*8 - 8*16;

drawChar(x1+i*8,y1,charVal,r,g,b);

}

void sendInstruction(int *instr)

{

unsigned char result;

int tries = 0;

//int gray = 1;

//while(gray == 1)

// gray = PollComport(0,&result,1); //to flush out initial data

//do

//printf("*******: %i ::******\n",instr[4]);

int i;

{

result = 0;

packet[0] = ((instr[0] & 0x3F) << 2) | ((instr[1] & 0xC00) >> 10);

packet[1] = ( instr[1] & 0x3FC) >> 2;

packet[2] = ((instr[1] & 0x3) << 6) | ((instr[2] & 0x3F0) >> 4);

packet[3] = ((instr[2] & 0xF) << 4) | ((instr[3] & 0x1E0) >> 5);

packet[4] = ((instr[3] & 0x1F) << 3) | ((instr[4] & 0x380) >> 7);

packet[5] = ((instr[4] & 0x7F) << 1) | ((instr[5] & 0x100) >> 8);

packet[6] = ((instr[5] & 0xFF));

packet[7] = instr[6] & 0xFF;

packet[8] = instr[7] & 0xFF;

packet[9] = 0;

for(i = 0; i < (PACKET LENGTH-1); i ++)</pre>

{

packet[PACKET_LENGTH-1] ^= packet[i];

SendByte(0,(unsigned char)packet[i]);

//printf("%i: %i\n",i,packet[i]);

}

SendByte(0,(unsigned char)packet[PACKET_LENGTH-1]);

tries ++;

```

int pollResult = 0;

}

```

while(pollResult == 0){

pollResult =PollComport(0,&result,1);

//printf(".");

}

//printf("Got Ack: %d\n",result);

//printf("tries: %d result = %d, poll_res = %i\n",tries, result,pollResult);

}

/*int wait = 0;

for(i = 0; i < 10000000; i ++)

wait ++;

i = wait;*/

//while(result < 128);</pre>

```

}

```

void fillRectangle(int x, int y, int w, int h, int r, int g, int b);

void fillCircle(int x, int y, int r, int red, int green, int blue);

void drawRectangle(int x, int y, int w, int h, int r, int g, int b);

void drawCircle(int x, int y, int r, int red, int green, int blue);

void drawLine(int x1, int x2, int y1, int y2, int r, int g, int b);

void drawChar(int x1, int y1, int charVal, int r, int g, int b);

void drawString(int x1, int y1, char *string, int r, int g, int b);

void drawPolygon(int *x, int *y, int elems, int r, int g, int b);

void writeInstruction(int PC, char a, char b, char c, char d, char e, char f);

void startProgram(void);

void startDownload(void);

void finishDownload(void);

void frameUpdate(void);

void setDrawMode(int dm);

void sendInstruction(int *instr);

int computeChecksum(int *packet);

```

module Decoder(instruction, ctrl\_ALU, ctrl\_BS, isBranch, isLoad, isStore, isJump, isDraw, isIMMOpp, SA, SB, SD, IMM, WE);

input wire [79:0] instruction;

```

output reg [3:0] ctrl_ALU;

output reg [3:0] ctrl_BS;

output reg isBranch;

output reg isLoad;

output reg isStore;

output reg isJump;

output reg isDraw;

output reg isIMMOpp;

output reg [4:0] SA, SB, SD;

output reg [31:0] IMM;

output reg WE;

parameter

ADD = 6'b100000,

SUB = 6'b100001,

SL = 6'b100010,

SR = 6'b100011,

OR = 6'b100100,

NOR = 6'b100101,

AND = 6'b100110,

NAND= 6'b100111,

XOR = 6'b101000,

ADDI= 6'b110101,

SUBI= 6'b110110,

SLI = 6'b110111,

SRI = 6'b111000,

LD = 6'b110011,

ST = 6'b110100,

NOT = 6'b111001,

BGT = 6'b101001,

BLT = 6'b101010,

BGE = 6'b101011,

BLE = 6'b101100,

BEQ = 6'b101101,

BNE = 6'b101110,

BEZ = 6'b101111,

BNEZ= 6'b110000,

J = 6'b110001,

JR = 6'b110010,

JAL = 6'b111010,

CIRCLE FILL = 6'b000000,

CIRCLE_DRAW = 6'b000001,

SQUARE_FILL = 6'b000010,

SQUARE_DRAW = 6'b000011,

LINE_DRAW = 6'b000100,

TEXT_WRITE = 6'b000101,

FRAME_UPDATE = 6'b000110;

```

```

BS_blt = 4'd1,

BS_bge = 4'd2,

BS_ble = 4'd3,

//BS_ble = 4'd4,

BS_beq = 4'd5,

BS_bne = 4'd6,

BS_bez = 4'd7,

BS_bnez = 4'd8,

BS_j = 4'd9,

BS_jr = 4'd10,

BS jal = 4'd11,

BS nop = 4'd12;

parameter

ALU_add = 4'd0,

ALU_sub = 4'd1,

ALU_sl = 4'd2,

ALU_sr = 4'd3,

ALU_and = 4'd4,

ALU_or = 4'd5,

ALU_xor = 4'd6,

ALU_nand= 4'd7,

ALU_not = 4'd8,

ALU_nor = 4'd9,

ALU_nop = 4'd10;

always @(instruction)

begin

case(instruction[79:74])

ADD: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_add;

IMM = 0;

ctrl_BS = BS_nop;

end

SUB: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_sub;

IMM = 0;

```

```

ctrl_BS = BS_nop;

end

SL: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_sl;

IMM = 0;

ctrl_BS = BS_nop;

end

SR: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_sr;

IMM = 0;

ctrl_BS = BS_nop;

end

OR: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_or;

IMM = 0;

ctrl_BS = BS_nop;

end

NOR: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

```

```

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_nor;

IMM = 0;

ctrl_BS = BS_nop;

end

AND: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_and;

IMM = 0;

ctrl_BS = BS_nop;

end

NAND: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_nand;

IMM = 0;

ctrl_BS = BS_nop;

end

XOR: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_xor;

IMM = 0;

ctrl_BS = BS_nop;

end

ADDI: begin

SA = instruction[73:69];

SD = instruction[68:64];

SB = instruction[68:64];

isBranch = 0;

```

```

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

WE = 1;

ctrl_ALU = ALU_add;

IMM = instruction[63:32];

ctrl_BS = BS_nop;

end

SUBI: begin

SA = instruction[73:69];

SD = instruction[68:64];

SB = instruction[68:64];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

WE = 1;

ctrl_ALU = ALU_sub;

IMM = instruction[63:32];

ctrl_BS = BS_nop;

end

SLI: begin

SA = instruction[73:69];

SD = instruction[68:64];

SB = instruction[68:64];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

WE = 1;

ctrl_ALU = ALU_sl;

IMM = instruction[63:32];

ctrl_BS = BS_nop;

end

SRI: begin

SA = instruction[73:69];

SD = instruction[68:64];

SB = instruction[68:64];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

WE = 1;

ctrl_ALU = ALU_sr;

IMM = instruction[63:32];

ctrl_BS = BS_nop;

end

ST: begin

```

```

SA = instruction[73:69];

SD = instruction[68:64];

SB = instruction[68:64];

isBranch = 0;

isLoad = 0;

isStore = 1;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

WE = 0;

ctrl ALU = ALU add;

IMM = instruction[63:32];

ctrl_BS = BS_nop;

end

LD: begin

SA = instruction[73:69];

SD = instruction[68:64];

SB = instruction[68:64];

isBranch = 0;

isLoad = 1;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

WE = 1;

ctrl_ALU = ALU_add;

IMM = instruction[63:32];

ctrl_BS = BS_nop;

end

NOT: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 1;

ctrl_ALU = ALU_not;

IMM = 0;

ctrl_BS = BS_nop;

end

BGT: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 1;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

IMM = instruction[63:32];

WE = 0;

```

```

ctrl_ALU = ALU_add;

ctrl_BS = BS_bgt;

end

BLT: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 1;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

IMM = instruction[63:32];

WE = 0;

ctrl_ALU = ALU_add;

ctrl_BS = BS_blt;

end

BGE: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 1;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

IMM = instruction[63:32];

WE = 0;

ctrl_ALU = ALU_add;

ctrl_BS = BS_bge;

end

BLE: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 1;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

IMM = instruction[63:32];

WE = 0;

ctrl ALU = ALU add;

ctrl_BS = BS_ble;

end

BEQ: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 1;

isLoad = 0;

isStore = 0;

isJump = 0;

```

```

isDraw = 0;

isIMMOpp = 1;

IMM = instruction[63:32];

WE = 0;

ctrl_ALU = ALU_add;

ctrl_BS = BS_beq;

end

BNE: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 1;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

IMM = instruction[63:32];

WE = 0;

ctrl_ALU = ALU_add;

ctrl_BS = BS_bne;

end

BEZ: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 1;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

IMM = instruction[63:32];

WE = 0;

ctrl ALU = ALU add;

ctrl BS = BS bez;

end

BNEZ: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 1;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 1;

IMM = instruction[63:32];

WE = 0;

ctrl_ALU = ALU_add;

ctrl_BS = BS_bnez;

end

J: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

```

```

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 1;

isDraw = 0;

isIMMOpp = 1;

IMM = instruction[63:32];

WE = 0;

ctrl_ALU = ALU_add;

ctrl_BS = BS_j;

end

JR: begin

SA = instruction[73:69];

SB = 0;

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 1;

isDraw = 0;

isIMMOpp = 0;

WE = 0;

ctrl ALU = ALU add;

ctrl_BS = BS_jr;

IMM = 0;

end

JAL: begin

SA = instruction[73:69];

SB = 0;

SD = 5'd31;

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 1;

isDraw = 0;

isIMMOpp = 0;

IMM = instruction[63:32];

WE = 1;

ctrl_ALU = ALU_add;

ctrl_BS = BS_jr;

end

CIRCLE_FILL: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 1;

isIMMOpp = 0;

WE = 0;

ctrl_ALU = ALU_nop;

IMM = 0;

ctrl_BS = BS_nop;

```

```

CIRCLE_DRAW: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 1;

isIMMOpp = 0;

WE = 0;

ctrl_ALU = ALU_nop;

IMM = 0;

ctrl_BS = BS_nop;

end

SQUARE_FILL: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 1;

isIMMOpp = 0;

WE = 0;

ctrl_ALU = ALU_nop;

IMM = 0;

ctrl_BS = BS_nop;

end

SQUARE_DRAW: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 1;

isIMMOpp = 0;

WE = 0;

ctrl_ALU = ALU_nop;

IMM = 0;

ctrl_BS = BS_nop;

end

LINE DRAW: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 1;

isIMMOpp = 0;

WE = 0;

```

```

ctrl_ALU = ALU_nop;

IMM = 0;

ctrl_BS = BS_nop;

end

TEXT_WRITE: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 1;

isIMMOpp = 0;

WE = 0;

ctrl_ALU = ALU_nop;

IMM = 0;

ctrl_BS = BS_nop;

end

FRAME_UPDATE: begin

SA = instruction[73:69];

SB = instruction[68:64];

SD = instruction[63:59];

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 1;

isIMMOpp = 0;

WE = 0;

ctrl_ALU = ALU_nop;

IMM = 0;

ctrl_BS = BS_nop;

end

default: begin

SA = 0;

SB = 0;

SD = 0;

isBranch = 0;

isLoad = 0;

isStore = 0;

isJump = 0;

isDraw = 0;

isIMMOpp = 0;

WE = 0;

ctrl_ALU = ALU_and;

IMM = 0;

ctrl_BS = BS_nop;

end

endcase

```

### endmodule