# **Section 31. DMA Controller**

## **HIGHLIGHTS**

This section of the manual contains the following major topics:

| 31.1 | Introduction                              | 31-2  |

|------|-------------------------------------------|-------|

| 31.2 | Status and Control Registers              |       |

| 31.3 | Modes of Operation                        | 31-29 |

| 31.4 | Channel Control                           | 31-40 |

| 31.5 | Interrupts                                | 31-44 |

| 31.6 | Operation in Power-Saving and Debug Modes | 31-46 |

| 31.7 | Effects of Various Resets                 | 31-46 |

| 31.8 | Related Application Notes                 | 31-47 |

| 31.9 | Revision History                          |       |

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device, this manual section may not apply to all PIC32 devices.

Please consult the note at the beginning of the "Direct Memory Access (DMA) Controller" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

## 31.1 INTRODUCTION

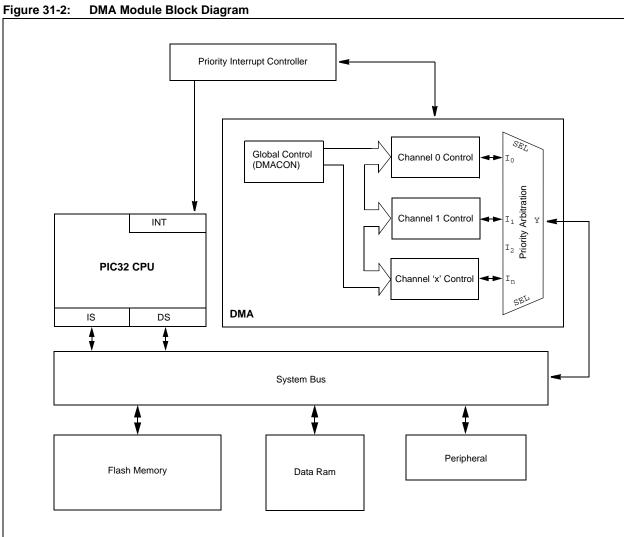

The Direct Memory Access (DMA) controller is a bus master module that is useful for data transfers between different peripherals without intervention from the CPU. The source and destination of a DMA transfer can be any of the memory-mapped modules included in the PIC32 family of devices. For example, memory, or one of the Peripheral Bus (PB) devices such as the SPI or UART, among others.

Key features of the DMA module include:

- Depending on the device, up to eight identical channels are available, including:

- Auto-Increment Source and Destination Address registers

- Source and Destination Pointers

- · Depending on the device, uninterrupted data transfers of up to 64 Kbytes are supported

- · Flexible data transfer, featuring the following:

- Transfer granularity down to byte level

- Bytes need not be word-aligned at source and destination

- · Fixed priority channel arbitration

- · Flexible DMA channel operating modes, including:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests, featuring:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Automatic transfer termination upon a data pattern match

- · Multiple DMA channel status interrupts, supplying:

- DMA channel block transfer complete

- Source empty or half-empty

- Destination full or half-full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- · DMA debug support features, including:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module, featuring:

- CRC module can be assigned to any of the available channels

- Data read from the source can be reordered on some devices

- CRC module is highly configurable

- CRC calculation

These features are also available in the DMA controller:

- · Different source and destination sizes

- Memory-to-memory transfers

- · Memory-to-peripheral transfers

- Channel auto-enable

- Events start/stop

- Pattern match detection

- Channel chaining

## 31.1.1 DMA Operation

A DMA channel transfers data from a source to a destination without CPU intervention. The source and destination start addresses define the start address of the source and destination, respectively.

Both the source and destination have independently configurable sizes and the number of the transferred bytes is independent of the source and destination sizes.

A transfer is initiated either by software or by an interrupt request. The user can select any interrupt on the device to start a DMA transfer.

Upon transfer initiation, the DMA controller will perform a cell transfer (defined by the cell size register) and the channel remains enabled until all bytes of a block (the larger of source size or destination size) transfer is complete. When a channel is disabled, further transfers will be prohibited until the channel is re-enabled.

The DMA channel uses separate pointers to keep track of the current word locations at the source and destination.

Interrupts can be generated when the source/destination pointer is half of the source/destination size, or when the source/destination counter reaches the end of the source/destination.

A DMA transfer can be aborted by the software, by a pattern match or by an interrupt event. The transfer will also stop when an address error is detected.

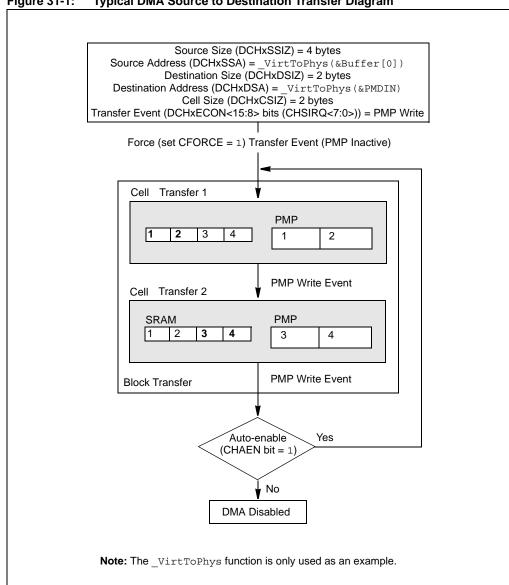

Figure 31-1 shows a typical DMA transfer. The block transfer size is set by setting the Source size (DCHxSSIZ) and Destination size (DCHxDSIZ) to 4 and 2 bytes (block size is 4). The source (DCHxSSA) and destination (DCHxDSA) registers are then given starting address locations. The source address is the physical SRAM location of an array named buffer. The destination address is the physical PMDIN (PMP output buffer) memory location. The cell size (DCHxCSIZ) is also set to 2. This means the 4 byte block transfer will take two 2 byte cell transfers to be completed. The transfer event for the DMA is set to be a PMP write, which means when a PMP write occurs, a cell transfer will be initiated. Notice the DMA channel can be auto-enabled by setting the CHAEN bit to '1' in the DCHxCON register. A DMA transfer can also be forced by writing a '1' to the CFORCE bit in the DCHXECON register. If the channel is auto-enabled, at the end of a block transfer all channel registers reset to their initial set state before the initial cell transfer. If not, the DMA channel becomes disabled.

Figure 31-1: Typical DMA Source to Destination Transfer Diagram

### 31.2 STATUS AND CONTROL REGISTERS

**Note:** A PIC32 device may have one or more DMA channels. An 'x' used in the names of Control/Status bits and registers denotes the particular channel. Refer to the "**Direct Memory Access Controller**" chapter of the specific device data sheet for more details.

The DMA module consists of the following Special Function Registers (SFRs):

DMACON: DMA Controller Control Register

This register configures the corresponding DMA channel.

• DMASTAT: DMA Status Register

This register contains the status of the last read or write transfer that occurred.

DMAADDR: DMA Address Register

This register contains the address of the most recent DMA transfer.

DCRCCON: DMA CRC Control Register

This register controls the CRC of the DMA and how it will function.

DCRCDATA: DMA CRC Data Register

This register sets the initial value of the CRC generator. Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC.

• DCRCXOR: DMA CRCXOR Enable Register

This register provides a description of the generator polynomial for CRC calculation.

DCHxCON: DMA Channel 'x' Control Register

This register controls the configuration of a specific DMA channel.

DCHxECON: DMA Channel 'x' Event Control Register

This register controls the event for a specific DMA channel.

• DCHxINT: DMA Channel 'x' Interrupt Control Register

This register controls the DMA interrupt for a specific DMA channel.

DCHxSSA: DMA Channel 'x' Source Start Address Register

This register configures the source start address for a specific DMA channel.

DCHxDSA: DMA Channel 'x' Destination Start Address Register

This register configures the destination start address for a specific DMA channel.

DCHxSSIZ: DMA Channel 'x' Source Size Register

This register configures the source size for a specific DMA channel.

DCHxDSIZ: DMA Channel 'x' Destination Size Register

This register configures the destination size for a specific DMA channel.

• DCHxSPTR: DMA Channel 'x' Source Pointer Register

This register contains the address of the current location of the source for a specific DMA channel.

• DCHxDPTR: DMA Channel 'x' Destination Pointer Register

This register contains the address of the current location of the destination for a specific DMA channel.

DCHxCSIZ: DMA Channel 'x' Cell Size Register

This register configures how many transfers can occur per event for a specific DMA channel.

• DCHxCPTR: DMA Channel 'x' Cell Pointer Register

This register counts how many transfers have occurred since the last event for a specific DMA channel.

• DCHxDAT: DMA Channel 'x' Pattern Data Register

This register contains data to be matched to allow a terminate on match for a specific DMA channel.

each bit.

Table 31-1:

Table 31-1 provides a brief summary of the related DMA module registers. Corresponding register tables appear after the summary, that include a detailed description of each bit.

Table 31-1: DMA Register Summary

| Name                    | Bit<br>Range | Bit 31/15                       | Bit 30/14                     | Bit 29/13               | Bit 28/12 | Bit 27/11               | Bit 26/10  | Bit 25/9 | Bit 24/8            | Bit 23/7              | Bit 22/6 | Bit 21/5              | Bit 20/4 | Bit 19/3               | Bit 118/2 | Bit 17/1 | Bit 16/0 |

|-------------------------|--------------|---------------------------------|-------------------------------|-------------------------|-----------|-------------------------|------------|----------|---------------------|-----------------------|----------|-----------------------|----------|------------------------|-----------|----------|----------|

| DMACON <sup>(1)</sup>   | 31:15        | _                               | _                             | _                       | _         | _                       | _          | _        | _                   | _                     | _        | _                     | _        | _                      | _         | _        | _        |

|                         | 15:0         | _                               | _                             | _                       | _         | _                       | _          | _        | _                   | ON                    | _        | _                     | SUSPEND  | DMABUSY <sup>(2)</sup> | _         | _        | _        |

| DMASTAT                 | 31:16        | RDWR <sup>(2)</sup>             | _                             | _                       | _         | _                       | _          | _        | _                   | _                     | _        | _                     | _        | _                      | _         | _        | _        |

|                         | 15:0         | _                               | _                             | _                       | _         | _                       | _          | _        | _                   | _                     | _        | _                     | _        | RDWR <sup>(2)</sup>    | DM        | ACH<2:0: | >(2)     |

| DMAADDR                 | 31:16        |                                 |                               |                         |           |                         |            | D        | MAADDR<             | 31:16>                |          |                       |          |                        |           |          |          |

|                         | 15:0         |                                 |                               |                         |           |                         |            | [        | MAADDR<             | <15:0>                |          |                       |          |                        |           |          |          |

| DCRCCON <sup>(1)</sup>  | 31:16        | _                               | _                             | BYTO<1:                 | 0>(2)     | WBO <sup>(2)</sup>      | _          | _        | BITO <sup>(2)</sup> | _                     | _        | _                     | _        | _                      | _         | _        | _        |

|                         | 15:0         | _                               | _                             | _                       |           | PLE                     | EN<4:0>(2) |          |                     | CRCEN                 | CRCAPP   | CRCTYP <sup>(2)</sup> | _        | _                      | CR        | CCH<2:0: | >(2)     |

| DCRCDATA <sup>(1)</sup> | 31:16        |                                 |                               | •                       |           |                         |            | DC       | RCDATA<             | 31:16> <sup>(2)</sup> |          |                       |          |                        |           |          |          |

|                         | 15:0         |                                 |                               |                         |           |                         |            | DO       | CRCDATA<            | 15:0> <sup>(2)</sup>  |          |                       |          |                        |           |          |          |

| DCRCXOR <sup>(1)</sup>  | 31:16        |                                 | DCRCXOR<31:16> <sup>(2)</sup> |                         |           |                         |            |          |                     |                       |          |                       |          |                        |           |          |          |

|                         | 15:0         |                                 | DCRCXOR<15:0> <sup>(2)</sup>  |                         |           |                         |            |          |                     |                       |          |                       |          |                        |           |          |          |

| _                       | 31:16        | CHPIGN<7:0>                     |                               |                         |           |                         |            |          |                     | _                     | _        | _                     | _        | _                      |           |          |          |

|                         | 15:0         | CHBUSY <sup>(2)</sup>           | _                             | CHPIGNEN <sup>(2)</sup> | _         | CHPATLEN <sup>(2)</sup> | _          | _        | CHCHNS              | CHEN                  | CHAED    | CHCHN                 | CHAEN    | _                      | CHEDET    | CHPR     | RI<1:0>  |

| DCHxECON <sup>(1)</sup> | 31:16        | _                               | _                             | _                       | _         | _                       | _          | _        | 1                   |                       |          |                       | CHAIRC   | 0<7:0>                 |           |          |          |

|                         | 15:0         |                                 |                               | •                       | CHSIRC    | 0<7:0>                  |            |          |                     | CFORCE                | CABORT   | PATEN                 | SIRQEN   | AIRQEN                 | _         | _        | _        |

| DCHxINT <sup>(1)</sup>  | 31:16        | _                               | _                             | _                       | _         | _                       | _          | _        | _                   | CHSDIE                | CHSHIE   | CHDDIE                | CHDHIE   | CHBCIE                 | CHCCIE    | CHTAIE   | CHERIE   |

|                         | 15:0         | _                               | _                             | _                       | _         | _                       | _          | _        | 1                   | CHSDIF                | CHSHIF   | CHDDIF                | CHDHIF   | CHBCIF                 | CHCCIF    | CHTAIF   | CHERIF   |

| DCHxSSA <sup>(1)</sup>  | 31:16        |                                 | •                             | •                       |           |                         | •          |          | CHSSA<3             | 1:16>                 |          |                       |          |                        |           |          |          |

|                         | 15:0         |                                 |                               |                         |           |                         |            |          | CHSSA<1             | 5:0>                  |          |                       |          |                        |           |          |          |

| DCHxDSA                 | 31:16        |                                 |                               |                         |           |                         |            |          | CHDSA<3             | 1:16>                 |          |                       |          |                        |           |          |          |

|                         | 15:0         |                                 |                               |                         |           |                         |            |          | CHDSA<1             | 5:0>                  |          |                       |          |                        |           |          |          |

| DCHxSSIZ <sup>(1)</sup> | 31:16        | _                               | _                             | _                       | _         | _                       | _          | _        | _                   | _                     | _        | _                     | _        | _                      | _         | _        | _        |

|                         | 15:0         |                                 |                               |                         |           |                         |            |          | CHSSIZ<15           | 5:0>(2)               |          |                       |          |                        |           |          |          |

| DCHxDSIZ <sup>(1)</sup> | 31:16        | _                               | _                             | _                       | _         | -                       | _          | _        | _                   | _                     | _        | _                     | _        | _                      | _         | _        | _        |

|                         | 15:0         | 5:0 CHDSIZ<15:0> <sup>(2)</sup> |                               |                         |           |                         |            |          |                     |                       |          |                       |          |                        |           |          |          |

| DCHxSPTR                | 31:16        | _                               | _                             | _                       | _         | _                       | _          | _        | _                   | _                     | _        | _                     | _        | _                      | _         | _        | _        |

|                         | 15:0         |                                 |                               |                         |           |                         |            |          | CHSPTR<             | 15:0>                 |          |                       |          |                        |           |          |          |

Legend

DS60001117H-page 31-7

— = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

Note 1: This register has an associated Clear, Set, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively. These registers have the same name with CLR, SET, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively. These registers have the same name with CLR, SET, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively. These registers have the same name with CLR, SET, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively. These registers have the same name with CLR, SET, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively. These registers have the same name with CLR, SET, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively. These registers have the same name with CLR, SET, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively. These registers have the same name with CLR, SET, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively. These registers have the same name with CLR, SET, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively.

2: This bit is not available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

Table 31-1: DMA Register Summary (Continued)

| Name                    | Bit<br>Range | Bit 31/15 | Bit 30/14 | Bit 29/13 | Bit 28/12 | Bit 27/11             | Bit 26/10 | Bit 25/9 | Bit 24/8  | Bit 23/7            | Bit 22/6 | Bit 21/5 | Bit 20/4 | Bit 19/3 | Bit 118/2 | Bit 17/1 | Bit 16/0 |

|-------------------------|--------------|-----------|-----------|-----------|-----------|-----------------------|-----------|----------|-----------|---------------------|----------|----------|----------|----------|-----------|----------|----------|

| DCHxDPTR                | 31:16        | _         | _         | _         | _         | -                     | _         | _        | _         | _                   | _        | _        | _        | _        | _         | _        | _        |

|                         | 15:0         |           |           |           |           |                       |           | C        | HDPTR<1   | 5:0> <b>(2)</b>     |          |          |          |          |           |          |          |

| DCHxCSIZ <sup>(1)</sup> | 31:16        | _         | _         | _         | _         | _                     | _         | _        | _         | _                   | _        | _        | _        | _        | _         | _        | _        |

|                         | 15:0         |           |           |           |           |                       |           | (        | CHCSIZ<15 | 5:0> <sup>(2)</sup> |          |          |          |          |           |          |          |

| DCHxCPTR                | 31:16        | _         | _         | _         | _         | _                     | _         | _        | _         | _                   | _        | _        | _        | _        | _         | _        | _        |

|                         | 15:0         |           |           |           |           |                       |           | C        | CHCPTR<1  | 5:0> <sup>(2)</sup> |          |          |          |          |           |          |          |

| DCHxDAT <sup>(1)</sup>  | 31:16        | _         | _         | _         | _         | _                     | _         | _        | _         | _                   | _        | _        | _        | _        | _         | _        | _        |

|                         | 15:0         |           |           |           | CHPDAT<   | :15:8> <sup>(2)</sup> |           |          |           |                     |          |          | CHPDA    | Γ<7:0>   |           |          |          |

**Legend:** — = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

This register has an associated Clear, Set, and Invert register at an offset of 0x4, 0x8, and 0xC bytes, respectively. These registers have the same name with CLR, SET, and INV appended to the end of the register name (e.g., DMACONCLR). Writing a '1' to any bit position in the Clear, Set, or Invert register will clear valid bits in the associated register. Reads from these registers should be ignored.

PIC32 Family Reference Manual

2: This bit is not available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

Register 31-1: DMACON: DMA Controller Control Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | _                 | -                 | _                 | _                 |                        |                   | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | _                 | SUSPEND           | DMABUSY <sup>(1)</sup> | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 |                        | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: DMA On bit

1 = DMA module is enabled

0 = DMA module is disabled

When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

bit 14-13 **Unimplemented:** Read as '0' bit 12 **SUSPEND:** DMA Suspend bit

1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

0 = DMA operates normally

bit 11 **DMABUSY:** DMA Module Busy bit<sup>(1)</sup>

1 = DMA module is active

0 = DMA module is disabled and not actively transferring data

bit 10-0 Unimplemented: Read as '0'

Note 1: This bit is not available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

Register 31-2: DMASTAT: DMA Status Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04:04        | R-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | RDWR              | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | RDWR              | DMACH<2:0>        |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 RDWR: Read/Write Status bit

1 = Last DMA bus access when an error that was detected was a read

0 = Last DMA bus access when an error that was detected was a write

bit 30-4 **Unimplemented:** Read as '0' bit 3 **RDWR:** Read/Write Status bit

1 = Last DMA bus access when an error that was detected was a read

0 = Last DMA bus access when an error that was detected was a write

bit 2-0 DMACH<2:0>: DMA Channel bits

These bits contain the value of the most recent active DMA channel when an error was detected.

Note: Not all bits in register are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

Register 31-3: DMAADDR: DMA Address Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        |                   |                   |                   | DMAADDF           | ?<31:24>          |                   |                  |                  |  |  |  |  |

| 22,46        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   | DMAADDR<7:0>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 DMAADDR<31:0>: DMA Module Address bits

Note: This register contains the address of the most recent DMA access.

Register 31-4: DCRCCON: DMA CRC Control Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2        | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |

|--------------|-------------------|-----------------------|-----------------------|----------------------|----------------------|--------------------------|------------------|---------------------|

| 04.04        | U-0               | U-0                   | R/W-0                 | R/W-0                | R/W-0                | U-0                      | U-0              | R/W-0               |

| 31:24        | _                 | _                     | BYTO<                 | :1:0> <sup>(1)</sup> | WBO <sup>(1,2)</sup> | _                        | _                | BITO <sup>(1)</sup> |

| 00.40        | U-0               | U-0                   | U-0                   | U-0                  | U-0                  | U-0                      | U-0              | U-0                 |

| 23:16        | _                 | _                     | -                     | _                    | _                    | _                        | _                | _                   |

| 45.0         | U-0               | U-0                   | U-0                   | R/W-0                | R/W-0                | R/W-0                    | R/W-0            | R/W-0               |

| 15:8         | _                 | _                     | -                     |                      |                      | PLEN<4:0> <sup>(2)</sup> |                  |                     |

| 7.0          | R/W-0             | R/W-0                 | R/W-0                 | U-0                  | U-0                  | R/W-0                    | R/W-0            | R/W-0               |

| 7:0          | CRCEN             | CRCAPP <sup>(2)</sup> | CRCTYP <sup>(1)</sup> | _                    | _                    | С                        | RCCH<2:0>        | 1)                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

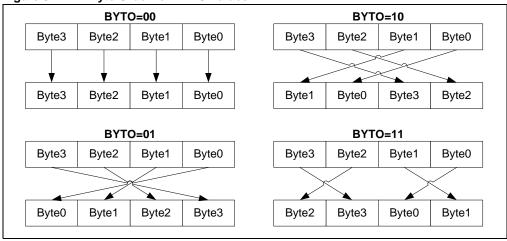

bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits(1)

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 WBO: CRC Write Byte Order Selection bit (1,2)

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit<sup>(2)</sup>

- 1 = The checksum/CRC is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The checksum/CRC is calculated Most Significant bit (MSb) first (i.e., not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(2)</sup>

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

These bits are unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- bit 6 CRCAPP: CRC Append Mode bit<sup>(2)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- Note 1: Not all bits are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

- 2: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

## Register 31-4: DCRCCON: DMA CRC Control Register (Continued)

- bit 5 CRCTYP: CRC Type Selection bit<sup>(1)</sup>

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits<sup>(1)</sup>

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- Note 1: Not all bits are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

- 2: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

Register 31-5: DCRCDATA: DMA CRC Data Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   |                   |                   | DCRCDATA          | A<31:24>          |                   |                  |                  |  |  |  |  |

| 22,46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   | A<15:8>           |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | ΓA<7:0>           |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than the PLEN<4:0> bits (DCRCCON<12:8>) will return '0' on any read.

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

Bits greater than the PLEN<4:0> bits (DCRCCON<12:8>) will return '0' on any read.

Note: Not all bits in this register are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

### Register 31-6: DCRCXOR: DMA CRCXOR Enable Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | DCRCXOR           | ?<31:24>          |                   |                  |                  |  |  |  |

| 22,46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

This register is unused.

### When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

Note: Not all bits in this register are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

Register 31-7: DCHxCON: DMA Channel 'x' Control Register

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-----------------------|-------------------|-------------------------|-------------------|-------------------------|-------------------|------------------|-----------------------|

| 04:04        | R/W-x                 | R/W-x             | R/W-x                   | R/W-x             | R/W-x                   | R/W-x             | R/W-x            | R/W-x                 |

| 31:24        |                       |                   |                         | CHPIGN            | <7:0> <sup>(1)</sup>    |                   |                  |                       |

| 00.40        | U-0                   | U-0               | U-0                     | U-0               | U-0                     | U-0               | U-0              | U-0                   |

| 23:16        | _                     | _                 | _                       | _                 | _                       | _                 | _                | _                     |

| 45.0         | R/W-0                 | U-0               | R/W-0                   | U-0               | R/W-0                   | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY <sup>(1)</sup> | _                 | CHPIGNEN <sup>(1)</sup> | _                 | CHPATLEN <sup>(1)</sup> | _                 | _                | CHCHNS <sup>(2)</sup> |

| 7.0          | R/W-0                 | R/W-0             | R/W-0                   | R/W-0             | U-0                     | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(3)</sup>   | CHAED             | CHCHN                   | CHAEN             | _                       | CHEDET            | CHPF             | RI<1:0>               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-24 CHPIGN<7:0>: Channel Register Data bits(1)

#### Pattern Terminate mode:

Any byte matching these bits during a pattern match may be ignored during the pattern match determination when the CHPIGNEN bit is set. If a byte is read that is identical to this data byte, the pattern match logic will treat it as a "don't care" when the pattern matching logic is enabled and the CHPIGEN bit is set.

- bit 23-16 Unimplemented: Read as '0'

- bit 15 **CHBUSY:** Channel Busy bit<sup>(1)</sup>

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **CHPIGNEN:** Enable Pattern Ignore Byte bit<sup>(1)</sup>

- 1 = Treat any byte that matches the CHPIGN<7:0> bits as a "don't care" when pattern matching is enabled

- 0 = Disable this feature

- bit 12 Unimplemented: Read as '0'

- bit 11 **CHPATLEN:** Pattern Length bit<sup>(1)</sup>

- 1 = 2 byte length

- 0 = 1 byte length

- bit 8 **CHCHNS:** Chain Channel Selection bit<sup>(2)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- bit 7 CHEN: Channel Enable bit (3)

- 1 = Channel is enabled

- 0 = Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

- bit 5 CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- Note 1: This bit is not available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

- 2: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 3: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

## Register 31-7: DCHxCON: DMA Channel 'x' Control Register (Continued)

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

- 0 = Channel is disabled on block transfer complete

- bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

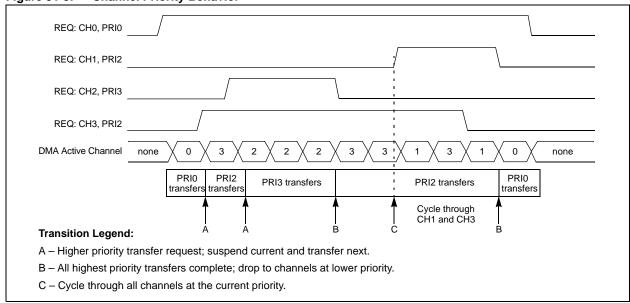

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: This bit is not available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

- 2: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 3: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

| Register 31-8: DCHxECON: DMA Channel 'x' Event Control | l Register |

|--------------------------------------------------------|------------|

|--------------------------------------------------------|------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 22.46        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 23:16        | CHAIRQ<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 15:8         |                   |                   |                   | CHSIRC            | (<7:0>            |                   |                  |                  |  |  |  |  |

| 7.0          | S-0               | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          | CFORCE            | CABORT            | PATEN             | SIRQEN            | AIRQEN            | _                 | _                | _                |  |  |  |  |

Legend:S = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-16 CHAIRQ<7:0>: Channel Transfer Abort IRQ bits

11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag

•

•

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits

11111111 = Interrupt 255 will initiate a DMA transfer

•

•

00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

bit 6 CABORT: DMA Abort Transfer bit

1 = A DMA transfer is aborted when this bit is written to a '1'

0 = This bit always reads '0'

bit 5 PATEN: Channel Pattern Match Abort Enable bit

1 = Abort transfer and clear CHEN on pattern match

0 = Pattern match is disabled

bit 4 SIRQEN: Channel Start IRQ Enable bit

1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

0 = Interrupt number CHSIRQ is ignored and does not start a transfer

bit 3 AIRQEN: Channel Abort IRQ Enable bit

1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

bit 2-0 Unimplemented: Read as '0'

Register 31-9: DCHxINT: DMA Channel 'x' Interrupt Control Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 22.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23 CHSDIE: Channel Source Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 22 CHSHIE: Channel Source Half Empty Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 21 CHDDIE: Channel Destination Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 20 CHDHIE: Channel Destination Half Full Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 19 CHBCIE: Channel Block Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 18 CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 17 CHTAIE: Channel Transfer Abort Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 16 CHERIE: Channel Address Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 15-8 **Unimplemented:** Read as '0'

bit 7 CHSDIF: Channel Source Done Interrupt Flag bit

1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)

0 = No interrupt is pending

bit 6 CHSHIF: Channel Source Half Empty Interrupt Flag bit

1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)

0 = No interrupt is pending

bit 5 CHDDIF: Channel Destination Done Interrupt Flag bit

1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)

0 = No interrupt is pending

### Register 31-9: DCHxINT: DMA Channel 'x' Interrupt Control Register (Continued)

- bit 4 CHDHIF: Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

- 0 = No interrupt is pending

- bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

- bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

- bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected Either the source or the destination address is invalid.

- 0 = No interrupt is pending

Register 31-10: DCHxSSA: DMA Channel 'x' Source Start Address Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | CHSSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 CHSSA<31:0> Channel Source Start Address bits

These bits define the channel source start address.

**Note:** The value of this register must be the physical address of the source.

Register 31-11: DCHxDSA: DMA Channel 'x' Destination Start Address Register

| rtegistei    | tegister 31-11. Donkboa. Diila onaimer x Destination otalit Address (register |                   |                   |                   |                      |                   |                  |                  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                                             | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 04.04        | R/W-0                                                                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | CHDSA<31:24> <sup>(1)</sup>                                                   |                   |                   |                   |                      |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0                                                                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | CHDSA<23:16> <sup>(1)</sup>                                                   |                   |                   |                   |                      |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0                                                                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHDSA<15:8> <sup>(1)</sup>                                                    |                   |                   |                   |                      |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0                                                                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

|              |                                                                               |                   |                   | CHDSA<            | :7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits

These bits define the channel destination start address.

**Note:** The value of this register must be the physical address of the destination.

Register 31-12: DCHxSSIZ: DMA Channel 'x' Source Size Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | CHSSIZ            | .<7:0>            |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

111111111111111 = 65,535 byte source size

•

•

•

0000000000000010 = 2 byte source size 0000000000000001 = 1 byte source size 00000000000000000 = 65,536 byte source size

Note: Not all bits in this register are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

Register 31-13: DCHxDSIZ: DMA Channel 'x' Destination Size Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   | _                 | _                 | -                 |                   |                   | _                | _                |  |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | ·                 |                   |                   | CHDSIZ            | ′<7:0>            |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDSIZ<15:0>: Channel Destination Size bits

111111111111111 = 65,535 byte destination size

•

•

.

Note: Not all bits in this register are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

Register 31-14: DCHxSPTR: DMA Channel 'x' Source Pointer Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | -                 | _                 | -                 |                   | _                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

|              |                   |                   |                   | CHSPTF            | R<7:0>            |                   | ·                | ·                |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits(1)

111111111111111 = Points to byte 65,535 of the source

•

•

•

0000000000000000 = Points to byte 1 of the source 000000000000000 = Points to byte 0 of the source

Note 1: When in Pattern Detect mode, this register is Reset on a pattern detect.

Register 31-15: DCHxDPTR: DMA Channel 'x' Destination Pointer Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

|              |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

111111111111111 = Points to byte 65,535 of the destination

•

•

•

Note: Not all bits in this register are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

Register 31-16: DCHxCSIZ: DMA Channel 'x' Cell Size Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | -                 | _                 | _                 | _                 | _                |                  |  |  |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | CHCSIZ            | <b>'</b> <7:0>    |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

111111111111111 = 65,535 bytes transferred on an event

•

•

•

Note: Not all bits in this register are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

Register 31-17: DCHxCPTR: DMA Channel 'x' Cell Pointer Register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCPTR<15:0>: Channel Cell Progress Pointer bits

11111111111111 = 65,535 bytes have been transferred since the last event

•

- Note 1: Not all bits in this register are available on all devices. Refer to the "Direct Memory Access (DMA) Controller" chapter in the specific device data sheet for availability.

- 2: When in Pattern Detect mode, this register is Reset on a pattern detect.

Register 31-18: DCHxDAT: DMA Channel 'x' Pattern Data Register

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|