Electrical & Computer Engineering

Dr. D. J. Jackson Lecture 15-5

|                  | 1                                 |

|------------------|-----------------------------------|

| Interface Prefix | Interface Type                    |

| asi              | Avalon-ST sink (input)            |

| aso              | Avalon-ST source (output)         |

| avm              | Avalon-MM master                  |

| avs              | Avalon-MM slave                   |

| axm              | AXI master                        |

| axs              | AXI slave                         |

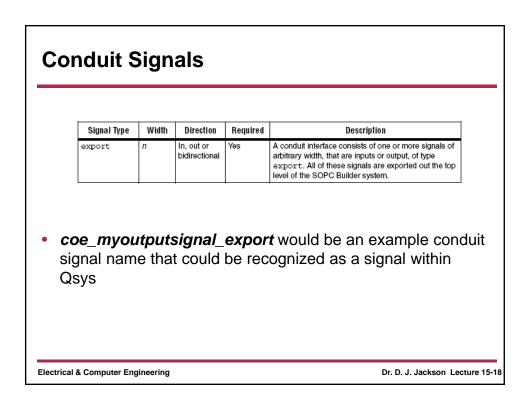

| coe              | Conduit                           |

| csi              | Clock Sink (input)                |

| CSO              | Clock Source (output)             |

| inr              | Interrupt receiver                |

| ins              | Interrupt sender                  |

| ncm              | Nios II custom instruction master |

| ncs              | Nios II custom instruction slave  |

| rsi              | Reset sink (input)                |

| rso              | Reset source (output)             |

| tcm              | Avalon-TC master                  |

| tcs              | Avalon-TC slave                   |

## **Clock Interfaces** • A clock input interface is used to provide synchronization and reset control for a component • A typical component has a clock input to provide a timing reference for other interfaces and internal logic • Valid signal types for a clock interface are: Signal Type Width Direction Required Description clk Input No A clock signal. Provides synchronization for internal 1 logic and for other interfaces. reset 1 Input No Reset input. Resets the internal logic of an interface or reset\_n component to a determined state. reset is synchronized to the clock input in the same interface. **Electrical & Computer Engineering** Dr. D. J. Jackson Lecture 15-12

| Signal Type         | Width                                       | Dir | Req'd | Description                                                                                                                                                                                                                                                                                           |  |

|---------------------|---------------------------------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fundamental Signals |                                             |     |       |                                                                                                                                                                                                                                                                                                       |  |

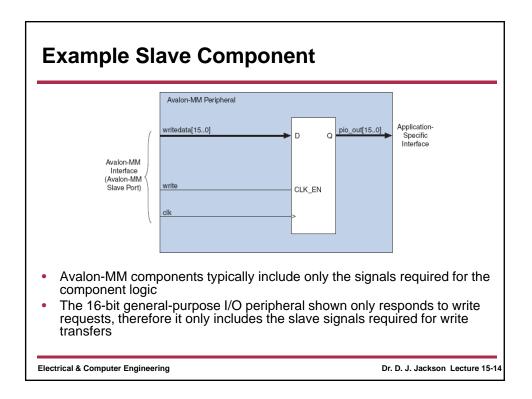

| read<br>read_n      | 1                                           | In  | No    | Asserted to indicate a read transfer. If present, readdata is required.                                                                                                                                                                                                                               |  |

| write<br>write_n    | 1                                           | In  | No    | Asserted to indicate a write transfer. If present,<br>writedata is required.                                                                                                                                                                                                                          |  |

| address             | 1-32                                        | In  | No    | Specifies an offset into the slave address space. Each<br>slave address value selects a word of slave data. For<br>example, address=0 selects the first <slave data="" width=""><br/>bits of slave data; address=1 selects the second <slave<br>data width&gt; bits of slave data.</slave<br></slave> |  |

| readdata            | 8,16,32,<br>64,<br>128,256,<br>512<br>1024  | Out | No    | The readdata provided by the slave in response to a read transfer.                                                                                                                                                                                                                                    |  |

| writedata           | 8,16,32,<br>64,<br>128,256,<br>512,102<br>4 | In  | No    | Data from the system interconnect fabric for write transfers.<br>The width must be the same as the width of readdata if<br>both are present.                                                                                                                                                          |  |