# SignalTap II with Verilog Designs

This tutorial explains how to use the SignalTap II feature within Altera's Quartus  $\mathbb{R}$  II software. The Signal-Tap II Embedded Logic Analyzer is a system-level debugging tool that captures and displays signals in circuits designed for implementation in Altera's FPGAs.

#### **Contents:**

Example Circuit Using the SignalTap II Logic Analyzer Probing the Design Using SignalTap Advanced Trigger Options Sample Depth and Buffer Acquisition Modes Quartus<sup>( $\mathbb{R}$ )</sup> II software includes a system level debugging tool called SignalTap II that can be used to capture and display signals in real time in any FPGA design.

Doing this tutorial, the reader will learn about:

- Probing signals using the SignalTap software

- Setting up triggers to determine when data is to be captured

This tutorial is aimed at the reader who wishes to probe signals in circuits defined using the Verilog hardware description language. An equivalent tutorial is available for the user who prefers the VHDL language.

#### PREREQUISITES

The reader is expected to have access to a computer that has Quartus II software installed. The detailed examples in the tutorial were obtained using the Quartus II version 7.1, but other versions of the software can also be used.

### 1 Example Circuit

As an example, we will use the switch circuit implemented in Verilog in Figure 1. This circuit simply connects the first 8 switches on the DE2 board to the first 8 red LEDs on the board. It does so at the positive edge of the clock (CLOCK\_50) by loading the values of the switches into a register whose output is connected directly to the red LEDs.

// Top-level module

module switches (SW, CLOCK\_50, LEDR);

input [7:0] SW;

input CLOCK\_50;

output reg [7:0] LEDR;

always @(posedge CLOCK\_50)

LEDR [7:0] = SW [7:0];

endmodule

Figure 1. The switch circuit implemented in Verilog code

Implement this circuit as follows:

- Create a project *switches*.

- Include a file *switches.v*, which corresponds to Figure 1, in the project. For convenience, this file is provided in the directory *DE2\_tutorials\design\_files*, which can be found on Altera's DE2 web pages.

- Choose the Cyclone II EP2C35F672C6 device, which is the FPGA chip on Altera's DE2 board.

- Import the csv file called *DE2\_pin\_assignments.csv* by clicking Assignments->Import Assignments. The node names used in the sample circuit correspond to the names used in this file.

- Compile the design.

# 2 Using the SignalTap II software

In the first part of the tutorial, we are going to set up the SignalTap Logic Analyzer to probe the values of the 8 LED switches. We will also set up the circuit to trigger when the first switch (LED[0]) is high.

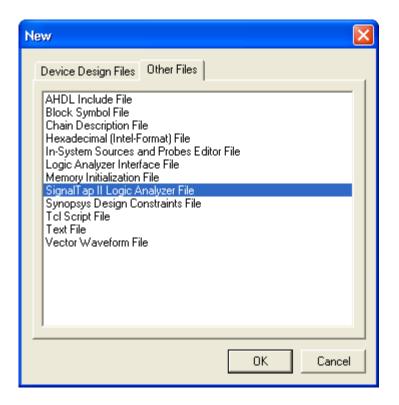

1. Open the SignalTap II window by selecting File > New, which gives the window shown in Figure 2. Click on the Other Files tab to reach the window displayed in Figure 3. Choose SignalTap II Logic Analyzer File and click OK.

| ٨ | lew 🔀                                                                                                                                                                            |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Device Design Files Other Files          AHDL File         Block Diagram/Schematic File         EDIF File         SOPC Builder System         Verilog HDL File         VHDL File |

|   | OK Cancel                                                                                                                                                                        |

Figure 2. Need to prepare a new file.

Figure 3. Choose to prepare a SignalTap II File.

2. The SignalTap II window with the Setup tab selected is depicted in Figure 4. Save the file under the name *switches.stp*. If the dialog box in Figure 5 appears, click OK. In the dialog box that follows (Figure 6), also click OK. For the dialog "Do you want to enable SignalTap II file switches.stp for the current project," click Yes (Figure 7). The file *switches.stp* is now the SignalTap file associated with the project.

Note: If you want to disable this file from the project, or to disable SignalTap from the project, go to Assignments > Settings. In the category list, select SignalTap II Logic Analyzer, bringing up the window in Figure 8. To turn off the analyzer, uncheck Enable. Also, it is possible to have multiple SignalTap files for a given project, but only one of them can be enabled at a time. Having multiple SignalTap files might be useful if the project is very large and different sections of the project need to be probed. To create a new SignalTap file for a project, simply follow Steps 1 and 2 again and give the new file a different name. To change the SignalTap file associated with the project, in the SignalTap File Name box browse for the file wanted and click Open, then click OK. For this tutorial we want to leave SignalTap enabled and we want the SignalTap II File name to be *switches.stp*. Make sure this is the case and click OK to leave the settings window.

| 🐇 Quartus II - D:/Mywork/Sign        | alTap/TutorialTrial3/switches - swit                             | ches - [stp1.stp*]                      |                              |                                                       |

|--------------------------------------|------------------------------------------------------------------|-----------------------------------------|------------------------------|-------------------------------------------------------|

| File Edit View Project Assign        | ments Processing Tools Window Help                               | <u>.</u><br>                            | ⊨ <u>m</u> n ⊨ @ @ •         | _ 8 >                                                 |

| Project Navigator + ×                |                                                                  |                                         |                              |                                                       |

| Entity                               | Switches.v                                                       | stp1.stp*                               |                              |                                                       |

| A Cyclone II: EP2C35F67              | 🛛 🛱 🍬 Խ 🔳 🖹 Invalid JTAG co                                      |                                         | 2                            |                                                       |

| > switches                           | Instance Manager: 🍬 🕪 🔳 🔝 Inval                                  |                                         |                              | × JTAG Chain Configuration: No device is selected ? × |

|                                      | Instance Status                                                  |                                         | x 0   Memory: 0   M512/LUTR/ | AM: Hardware: Please Select + Setup                   |

|                                      | auto_signaltap_0 Not running                                     | 00                                      | cels O bits                  |                                                       |

|                                      |                                                                  |                                         |                              | Device: None Detected 👻 Scan Chain                    |

|                                      | <                                                                |                                         |                              | >>> SOF Manager: 📩 🕕 🛄                                |

|                                      |                                                                  |                                         |                              | <b>N N</b>                                            |

|                                      | auto_signaltap_0                                                 | Allow all changes                       |                              | Signal Configuration: ×                               |

|                                      | Node                                                             | Data Enable Trigger Enable Trigger Leve | els                          | Clock                                                 |

|                                      | Type Alias Name                                                  | 0 0 117 Basic                           | -                            | · · · · · · · · · · · · · · · · · · ·                 |

|                                      | Double-click to add nodes                                        |                                         |                              | Data                                                  |

|                                      |                                                                  |                                         |                              | Sample depth: 128 💌 RAM type: Auto 🛫                  |

|                                      |                                                                  |                                         |                              | Buffer acquisition mode:                              |

|                                      |                                                                  |                                         |                              | Circular:     State Pre-trigger position              |

|                                      |                                                                  |                                         |                              |                                                       |

|                                      |                                                                  |                                         |                              | C Segmented: 128 1 sample segments                    |

|                                      |                                                                  |                                         |                              | Trigger.                                              |

| <br>▲ B ₽                            |                                                                  |                                         |                              | Trigger levels: 1                                     |

|                                      |                                                                  |                                         |                              |                                                       |

| Status • ×<br>Module Progress % Time |                                                                  |                                         |                              | Trigger in:                                           |

| ridges re rine                       | 🔉 Data 🔜 Setup                                                   |                                         |                              |                                                       |

|                                      | Hierarchy Display:                                               |                                         | × 🗆 Data Log: 👰              | ×                                                     |

|                                      | Theraicity Display.                                              |                                         | - Rate Log Est               |                                                       |

|                                      |                                                                  |                                         | M and_shrand_c               |                                                       |

|                                      |                                                                  |                                         |                              |                                                       |

|                                      |                                                                  |                                         |                              |                                                       |

|                                      |                                                                  |                                         |                              |                                                       |

|                                      | auto_signaltap_0                                                 |                                         |                              |                                                       |

| × Type Message                       |                                                                  |                                         |                              |                                                       |

|                                      |                                                                  |                                         |                              |                                                       |

|                                      |                                                                  |                                         |                              |                                                       |

|                                      | Info $\lambda$ Info $\lambda$ Warning $\lambda$ Critical Warning | λ Error λ Suppressed λ Flag /           |                              |                                                       |

| Message:                             | Location:                                                        |                                         |                              | - Locate                                              |

| For Help, press F1                   |                                                                  |                                         |                              | S+B+B Idle NUM                                        |

Figure 4. The SignalTap II window.

| Quartus | s II. 🛛 🔀                                                                                                                                                                                                                                                                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ⚠       | The SignalTap II Logic Analyzer is in the incremental compilation mode, however the design partitions in the current project are not all set to the<br>post-fit netlist type. Fitter generated nodes will not be accessable, and the SignalTap II Logic Analyzer instances will not be added incrementally to the<br>post-fitting netlist. |

|         | OK                                                                                                                                                                                                                                                                                                                                         |

Figure 5. Click OK to this dialog.

Figure 6. Click OK to this dialog.

| Settings - switches                     |                               |                                     |       |      |

|-----------------------------------------|-------------------------------|-------------------------------------|-------|------|

| Category:                               |                               |                                     |       |      |

| General                                 | SignalTap II Logic Analyz     |                                     |       |      |

| Files                                   |                               |                                     |       |      |

| Libraries<br>Device                     | Specify compilation options h | or the SignalTap II Logic Analyzer. |       |      |

| Operating Settings and Conditions       |                               |                                     |       |      |

| - Voltage                               | 🔽 Enable SignalTap II Logi    | -                                   |       |      |

| Temperature                             | SignalTap II File name:       | switches.stp                        |       |      |

| Compilation Process Settings            |                               |                                     |       |      |

| Early Timing Estimate                   |                               |                                     |       |      |

| Incremental Compilation                 |                               |                                     |       |      |

| EDA Tool Settings                       |                               |                                     |       |      |

| Design Entry/Synthesis<br>Simulation    |                               |                                     |       |      |

| - Timing Analysis                       |                               |                                     |       |      |

| - Formal Verification                   |                               |                                     |       |      |

| Physical Synthesis                      |                               |                                     |       |      |

| Board-Level                             |                               |                                     |       |      |

| ⊕ Analysis & Synthesis Settings         |                               |                                     |       |      |

| Fitter Settings                         |                               |                                     |       |      |

| Timing Analysis Settings                |                               |                                     |       |      |

| TimeQuest Timing Analyzer               |                               |                                     |       |      |

| Classic Timing Analyzer Settings        |                               |                                     |       |      |

| Classic Timing Analyzer Report          |                               |                                     |       |      |

| - Design Assistant                      |                               |                                     |       |      |

| SignalTap II Logic Analyzer             |                               |                                     |       |      |

| Logic Analyzer Interface                |                               |                                     |       |      |

| . Simulator Settings                    |                               |                                     |       |      |

| PowerPlay Power Analyzer Settings       |                               |                                     |       |      |

|                                         |                               |                                     |       |      |

|                                         |                               |                                     |       |      |

|                                         |                               |                                     |       |      |

| < · · · · · · · · · · · · · · · · · · · |                               |                                     | OK Ca | ncel |

|                                         |                               |                                     |       |      |

Figure 8. The SignalTap II Settings window.

3. For this project, we wish to turn off the incremental compilation feature of the Quartus II software. To do this, in the SignalTap II window uncheck the Incremental Compilation box. Then, select the Setup tab to reach the window shown in Figure 9.

| nstance Manager: 🏲          | og 🍫 🔳 🔛 🗛dd          | nodes to the current instance | 2                 | × JTA    | G Chain Configuration: JTAG ready                         | 2 ×                 |

|-----------------------------|-----------------------|-------------------------------|-------------------|----------|-----------------------------------------------------------|---------------------|

| nstance<br>auto_signaltap_0 | Status<br>Not running | Incremental Compilation       | LEs: 0<br>O cells |          | dware: USB-Blaster [USB-0]  vice: @1: EP2C35 (0x020B40DD) | Setup<br>Scan Chain |

| ]                           | Ш                     |                               |                   | >>       | SOF Manager: 👗 🕕                                          |                     |

| trigger: 2007/05/1          | 5 10:41:50 #0         | Allow a                       | l changes         | -        | Signal Configuration:                                     | ×                   |

| N<br>Type Alias             | lode<br>Name          | Data Enable Trigger En        | Trigger           |          | Clock: CLOCK_50                                           | <b>_</b>            |

| 🏹 Data 🕵 Se                 | tup                   |                               |                   |          | Sample depth: 128 V RAM type: Auto                        | ▼ <b>▼</b>          |

| Hierarchy Display:          |                       |                               | ×                 | Data Log | : 🗛                                                       | ×                   |

|                             |                       |                               |                   | 💦 auto_: | signaltap_0                                               |                     |

| 💦 auto_signaltap_(          | D                     |                               |                   |          |                                                           |                     |

Figure 9. The Setup tab of the SignalTap II window with Incremental Compilation turned off.

4. We now need to add the nodes in the project that we wish to probe. In the Setup tab of the SignalTap II window, double-click in the window that says Double-click to add nodes, bringing up the Node Finder window in Figure 10. Click List. This will now display all the nodes that can be probed in the project. Highlight SW[0] to SW[7], and then click the > button to add the switches to be probed. Then click OK.

| Named: ×                       | ▼ Filter: SignalTap II: | pre-synthesis 💌 Customize | . List 👩      | OK     |

|--------------------------------|-------------------------|---------------------------|---------------|--------|

| ook in: <mark>Iswitches</mark> |                         | 💌 🔽 Include suber         | ntities Stop  | Cancel |

| lodes Found:                   |                         | Selected Nodes:           |               |        |

| Name                           | Assignments 🔼           | Name                      | Assignments T |        |

| LEDR[3]~reg0                   | Unassigned              | Iswitches SW[0]           | PIN_N25 Ir    |        |

| 🗈 LEDR[4]                      | PIN_AD22                | Iswitches SW[1]           | PIN_N26 Ir    |        |

| LEDR[4]~reg0                   | Unassigned              | Iswitches SW[2]           | PIN_P25 Ir    |        |

| 🞯 LEDR[5]                      | PIN_AD23                | Iswitches SW[3]           | PIN_AE14 Ir   |        |

| LEDR(5)~reg0                   | Unassigned              | Iswitches SW[4]           | PIN_AF14 Ir   |        |

| 💷 LEDR[6]                      | PIN_AD21                | Iswitches SW[5]           | PIN_AD13 Ir   |        |

| @LEDR[6]~reg0                  | Unassigned              | > Iswitches SW[6]         | PIN_AC13 Ir   |        |

| DEDR[7]                        | PIN_AC21                | Iswitches SW[7]           | PIN_C13 Ir    |        |

| LEDR[7]~reg0                   |                         | >>                        |               |        |

| ₽SW                            | Unassigned              | <                         |               |        |

| ➡ SW[0]                        | PIN_N25                 |                           |               |        |

| ▶SW[1]                         | PIN_N26                 | <<                        |               |        |

| ▶ SW[2]                        | PIN_P25                 |                           |               |        |

| ■ SW[3]                        | PIN_AE14                |                           |               |        |

| ■ SW[4]                        | PIN_AF14                |                           |               |        |

| SW[5]                          | PIN_AD13                |                           |               |        |

| ■> SW[6]                       | PIN_AC13                |                           |               |        |

| 🕪 SW[7]                        | PIN_C13                 |                           |               |        |

| <                              |                         | <                         | >             |        |

Figure 10. Add nodes in the Node Finder window.

5. Before the SignalTap analyzer can work, we need to set up what clock is going to run the SignalTap module that will be instantiated within our design. To do this, in the Clock box of the Signal Configuration pane

of the SignalTap window, click ..., which will again bring up the Node Finder window. Select List to add all the nodes that can be added as the clock, and then double-click CLOCK\_50, which results in the image shown in Figure 11. Click OK.

| lamed: ×          | ▼ Filter: SignalTap II: pr | e-synthesis 💌 Customize |               | OK     |

|-------------------|----------------------------|-------------------------|---------------|--------|

| ook in: Iswitches |                            | 💌 🔽 Include subentities | Stop          | Cancel |

| Nodes Found:      |                            | Selected Nodes:         |               |        |

| Name              | Assignments 🔼              | Name                    | Assignments T |        |

| CLOCK_50          | PIN_N2                     | Iswitches CLOCK_50      | PIN_N2 Ir     |        |

| 🐼 LEDR            | Unassigned                 |                         |               |        |

| @ LEDR[0]         | PIN_AE23                   |                         |               |        |

| LEDR(0)~reg0      | Unassigned                 |                         |               |        |

| LEDR[1]           | PIN_AF23                   |                         |               |        |

| LEDR[1]~reg0      | Unassigned 😑               |                         |               |        |

| 🐵 LEDR[2]         | PIN_AB21                   | 1                       |               |        |

| LEDR(2)~reg0      | Unassigned                 |                         |               |        |

| 🐵 LEDR[3]         | PIN_AC22                   |                         |               |        |

| LEDR(3)~reg0      | Unassigned                 | 1                       |               |        |

| 🐵 LEDR[4]         | PIN_AD22                   |                         |               |        |

| LEDR[4]~reg0      | Unassigned 📃 📿             | 1                       |               |        |

| 🐵 LEDR(5)         | PIN_AD23                   | 1                       |               |        |

| LEDR[5]~reg0      | Unassigned                 |                         |               |        |

| @LEDR[6]          | PIN_AD21                   |                         |               |        |

| LEDR[6]~reg0      | Unassigned                 |                         |               |        |

| @ LEDR[7]         | PIN_AC21                   |                         |               |        |

| LEDR[7]~reg0      | Unassigned                 |                         |               |        |

| າຊີເພ<br><        | Unassigned 🐸               | <                       | >             |        |

Figure 11. Set CLOCK\_50 as the clock for this SignalTap instance.

6. With the Setup tab of the SignalTap window selected, select the checkbox in the Trigger Levels column. In the dropdown menu at the top of this column, select Basic. Right-click on the Trigger Level cell corresponding to the node SW[0] and select High. Now, the trigger for running the Logic Analyzer will be when the first switch on the DE2 board is set to high, as shown in Figure 12. Note that you can right click on the Trigger Levels cell of any of the nodes being probed and set the trigger condition to a number of choices. The actual trigger condition will be true when the logical AND of all these conditions is satisfied. For now, just keep the trigger condition as SW[0] set to high and the others set to their default value, Don't Care.

| auto_ | signalt | ap_0   |             | 🔓 Allow all chan | ges            | • |

|-------|---------|--------|-------------|------------------|----------------|---|

|       |         | Node   | Data Enable | Trigger Enable   | Trigger Levels |   |

| Туре  | Alias   | Name   | 8           | 8                | 1 🔽 Basic 💽    |   |

|       |         | SVV[0] |             |                  | 1              |   |

|       |         | SVV[1] | <b>N</b>    | N                |                |   |

|       |         | SW[2]  | <b>N</b>    | N                |                |   |

|       |         | SVV[3] | <b>N</b>    | N                |                |   |

|       |         | SVV[4] | <b>N</b>    | N                |                |   |

|       |         | SVV[5] | <b>N</b>    | N                |                |   |

|       |         | SVV[6] | <b>N</b>    | N                |                |   |

|       |         | SW[7]  | V           | N                |                |   |

Figure 12. Setting the trigger conditions.

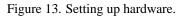

7. For SignalTap II to work, we need to properly set up the hardware. First, make sure the DE2 board is plugged in and turned on. In the Hardware section of the SignalTap II window, click Setup, bringing up the window in Figure 13. Double click USB-Blaster in the Available Hardware Items menu, then click Close.

| Hardware Setup                                                                                                                            |                     |               |                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------|---------------------------------|

| Hardware Settings JTAG Settings<br>Select a programming hardware se<br>hardware setup applies only to the<br>Currently selected hardware: | ·<br>etup to use wh | ammer window. | ces. This programming           |

| Hardware<br>USB-Blaster                                                                                                                   | Server<br>Local     | Port<br>USB-0 | Add Hardware<br>Remove Hardware |

|                                                                                                                                           |                     |               | Close                           |

The last step in instantiating SignalTap in your design is to compile the design. Select Processing > Start Compilation and indicate that you want to save the changes to the file by clicking OK. After compilation, go to Tools > Programmer and load the project onto the DE2 board.

### **3** Probing the Design Using SignalTap II

Now that the project with SignalTap II instantiated has been loaded onto the DE2 board, we can now probe the nodes as we would with an external logic analyzer.

- 1. On the DE2 board, first set all of the switches (0-7) to low. We will try to probe the values of these switches once switch 0 becomes high.

- 2. Select Processing > Run Analysis or click the icon in the SignalTap window. Then, click on the Data tab of the SignalTap II Window. You should get a screen similar to Figure 14. Note that the status column of the SignalTap II Instance window says "Waiting for trigger." This is because the trigger condition (Switch 0 being high) has not yet been met. (This is of course if Switch 0 is actually low as instructed in the previous step. If it is not, set it to low and then click Run Analysis again).

| stance   |          | jer: 🍬 Ņ 🔳 🔛<br>Status |        | Incremental Co  | mpilation |           | Configuration:   | ,            | 2        |                     |

|----------|----------|------------------------|--------|-----------------|-----------|-----------|------------------|--------------|----------|---------------------|

| auto_    | signalti | ap_0 Waiting for t     | rigger |                 | >         | Device:   |                  | (0x020B40DD) | <b>Y</b> | Setup<br>Scan Chain |

| log: 20  | 007/05   | /28 13:40:43 #0        |        |                 |           | click t   | o insert time ba | ,            |          |                     |

| Туре     | Alias    | Name                   | 0      | 16              | 32        | 48        | 64               | 80 96        | 5 11     | 2 128               |

|          |          | SV/[0]                 |        | ion in progress |           |           |                  |              |          |                     |

|          |          | SVV[1]                 |        |                 |           |           |                  |              |          |                     |

|          |          | SW[2]                  |        |                 |           |           |                  |              |          |                     |

|          |          | SW[3]                  |        |                 |           |           |                  |              |          |                     |

|          |          | SW[4]                  |        |                 |           |           |                  |              |          |                     |

|          |          | SVV[5]                 |        |                 |           |           |                  |              |          |                     |

|          |          | SVV[6]                 |        |                 |           |           |                  |              |          |                     |

|          |          | SW[7]                  |        |                 |           |           |                  |              |          |                     |

| Da       | ata 🛃    | J Setup                |        |                 |           |           |                  |              |          |                     |

| Hierarch | ny Disp  | lay:                   |        |                 | ×         | Data Log: | <b>F</b> AL      |              |          | 3                   |

| 1        |          |                        |        |                 |           | auto_sig  |                  |              |          |                     |

Figure 14. SignalTap II window after Run Analysis has been clicked.

3. Now, to observe the trigger feature of the Logic Analyzer, set Switch 0 on the DE2 board to high. The data window of the SignalTap II window should display the image in Figure 15. Note that this window shows the data levels of the 8 nodes being tapped before the trigger condition was met and also after. To see this, flip on any of the switches from 0-7 and then click Run Analysis again. When switch 0 is set to high again, you will see the values of the switches displayed on the SignalTap II Logic Analyzer.

| Instance Manager: 🍖 ⊳ 🔳 🔛 🛛 Read | y to acquire 🛛 🍳 🗙      | JTAG Chain Configuration: JTAG ready 🛛 🕄 🗙 |

|----------------------------------|-------------------------|--------------------------------------------|

| Instance Status                  | Incremental Compilation |                                            |

| auto_signaltap_0 Not running     |                         | Hardware: USB-Blaster [USB-0]              |

|                                  |                         |                                            |

|                                  |                         | Device: @1: EP2C35 (0x020B40DD) Scan Chain |

|                                  |                         | >> SOF Manager: 🚋 🕧 📖                      |

|                                  |                         |                                            |

|                                  |                         |                                            |

| <                                | >                       |                                            |

|                                  |                         |                                            |

| log: 2007/05/28 13:40:43 #0      |                         | click to insert time bar                   |

| Type Alias Name                  | -16 0 16                | 32 48 64 80 96 112                         |

| SVV[0]                           |                         |                                            |

| SW[1]                            |                         |                                            |

| 5W[2]                            |                         |                                            |

| SW[3]                            |                         |                                            |

| SV/[4]                           |                         |                                            |

| SVV[5]                           |                         |                                            |

| SVV[6]                           |                         |                                            |

| SW[7]                            | 1                       |                                            |

|                                  |                         |                                            |

| 🔊 Data 💭 Setup                   |                         |                                            |

| Hierarchy Display:               | ×                       | Data Log: 🔩 🗙                              |

| 🗹 🕩 switches                     |                         | 📲 🚼 auto_signaltap_0                       |

| _                                |                         | —                                          |

|                                  |                         |                                            |

|                                  |                         |                                            |

|                                  |                         |                                            |

|                                  |                         |                                            |

| auto_signaltap_0                 |                         |                                            |

Figure 15. Graphical display of values after trigger condition is met.

## 4 Advanced Trigger Options

Sometimes in a design you may want to have a more complicated triggering condition than SignalTap's basic triggering controls allow. The following section describes how to have multiple trigger levels as well as how to create advanced triggering options.

#### 4.1 Multiple Trigger Levels

In this section, we will set up the analyzer to trigger when there is a positive edge from switch 0, switch 1, switch 2, and then switch 3, in that order.

- 1. Click the Setup tab of the SignalTap II window.

- 2. In the Signal Configuration window, select 4 from Trigger Levels menu as in Figure 16. This modifies the node list window by creating three new Trigger Levels columns.

| Trigger levels: 4              |

|--------------------------------|

|                                |

| Trigger in:                    |

| Source: SW[0]                  |

| Pattern: Don't Care            |

| Trigger out:                   |

| Target: auto_stp_trigger_out_0 |

| Level: Active High             |

| Latency delay: 4 cycles        |

Figure 16. Set trigger levels to 4.

3. Right click the Trigger Level 1 cell for SW[0], and select Rising Edge. Do the same for the Trigger Level 2 cell for SW[1], and then for Trigger Level 3 for SW[2] and Trigger Level 4 for SW[3]. You should end up with a window that looks like Figure 17.

| trigger: 2007/05/15 15:33:01 #0 |       |        |             | 🖆 Allow all chan | Allow all changes        |             |             |             |  |  |  |  |  |  |  |

|---------------------------------|-------|--------|-------------|------------------|--------------------------|-------------|-------------|-------------|--|--|--|--|--|--|--|

|                                 |       | Node   | Data Enable | Trigger Enable   | er Enable Trigger Levels |             |             |             |  |  |  |  |  |  |  |

| Туре                            | Alias | Name   | 8           | 8                | 1 🔽 Basic 💽              | 2 🔽 Basic 💽 | 3 🔽 Basic 💽 | 4 🔽 Basic 💽 |  |  |  |  |  |  |  |

|                                 |       | SVV[0] | <b>N</b>    | N                | 5                        |             |             |             |  |  |  |  |  |  |  |

|                                 |       | SW[1]  | <b>N</b>    | <b>N</b>         |                          | 5           |             |             |  |  |  |  |  |  |  |

|                                 |       | SW[2]  | <b>N</b>    | N                |                          |             | 5           |             |  |  |  |  |  |  |  |

|                                 |       | SVV[3] |             | R                | <b>2</b>                 |             |             | 5           |  |  |  |  |  |  |  |

|                                 |       | SVV[4] | N           | N                | <b>3</b>                 |             | <b>3</b>    |             |  |  |  |  |  |  |  |

|                                 |       | SW[5]  | <b>N</b>    | N                |                          |             |             |             |  |  |  |  |  |  |  |

|                                 |       | SVV[6] | N           | <b>N</b>         |                          |             |             |             |  |  |  |  |  |  |  |

|                                 |       | SW[7]  | <b>N</b>    | N                |                          |             |             |             |  |  |  |  |  |  |  |

Figure 17. Multiple trigger levels set.

- 4. Now, recompile the design and load it onto the DE2 board again.

- 5. Go back to the SignalTap II window, click on the Data tab, and then click Run Analysis. Note that the window will say "Waiting for trigger" until the appropriate trigger condition is met. Then, in sequence, flip to 1 switches 0, 1, 2, and then 3. Each time you flip each switch, the status column of the Instance Manager of the SignalTap window will say a trigger condition has been met. Figure 18 shows what this window looks like after the first two switches have been flipped to 1.

After this has been done, you will see the values of all the switches displayed as in Figure 19. Experiment by following the procedure outlined in this section to set up other trigger conditions and use the DE2 board to test these trigger conditions.

If you want to continuously probe the analyzer, instead of clicking "Run Analysis," click "Autorun Analysis" which is the icon right next to the "Run Analysis" icon. If you do this, every time the trigger condition is met the value in the display will be updated. You do not have to re-select "Run Analysis." To stop the

"Autorun Analysis" function, click the 📕 icon.

| Instance Manager: 🍡 | 🔊 🔳 🔝 🗛 Acquisition in pro | gress     |           | 2          |                |          | ×              |

|---------------------|----------------------------|-----------|-----------|------------|----------------|----------|----------------|

| Instance            | Status                     | Increment | LEs: 481  | Memory: 10 | M512/LUTRAM: 0 | M4K/M9K  | M-RAM/M144K: 0 |

| 🚼 auto_signaltap_0  | Trigger level 2 met        | V         | 481 cells | 1024 bits  | 0 blocks       | 1 blocks | 0 blocks       |

Figure 18. Instance manager window after first two switches have been switched to 1.

| log: 2 | 2007/05 | /16 13:52:39 #0 |     |    |    |   |    |    |    | click to | o insert tim | e bar |    |      |    |    |    |     |     |

|--------|---------|-----------------|-----|----|----|---|----|----|----|----------|--------------|-------|----|------|----|----|----|-----|-----|

| Туре   | Alias   | Name            | -16 | -8 | 9  | 8 | 16 | 24 | 32 | 40       | 48           | 56    | 64 | . 72 | 80 | 88 | 96 | 104 | 112 |

|        |         | SV/[0]          |     |    |    |   |    |    |    |          |              |       |    |      |    |    |    |     |     |

|        |         | SV/[1]          |     |    | ;  |   |    |    |    |          |              |       |    |      |    |    |    |     |     |

|        |         | SV/[2]          |     |    | 1  |   |    |    |    |          |              |       |    |      |    |    |    |     |     |

|        |         | SW[3]           |     |    |    |   |    |    |    |          |              |       |    |      |    |    |    |     |     |

|        |         | SV/[4]          |     |    | 1  |   |    |    |    |          |              |       |    |      |    |    |    |     |     |

|        |         | SV/[5]          |     |    | 1  |   |    |    |    |          |              |       |    |      |    |    |    |     |     |

|        |         | SVV[6]          |     |    | i. |   |    |    |    |          |              |       |    |      |    |    |    |     |     |

|        |         | SVN[7]          |     |    |    |   |    |    |    |          |              |       |    |      |    |    |    |     |     |

Figure 19. Logic Analyzer display when all four trigger conditions have been met.

#### 4.2 Advanced Trigger Levels

In this section we will learn how to create advanced trigger conditions. Our trigger condition will be whenever any one of the first 3 LED displays have a positive or negative edge. This means that the Logic Analyzer will update its display everytime one of these inputs change. Note that we could have any logical function of the nodes being probed to trigger the analyzer. This is just an example. After you implement this in the next few steps, experiment with your own advanced triggers.

- 1. Have the *switches* project opened and compiled from the previous examples in this tutorial.

- 2. Open the SignalTap window select the Setup tab. In the Signal Configuration window make sure that the number of Trigger Levels is set to 1.

- 3. In the Trigger Levels column of the node list, make sure the box is checked and select Advanced from the dropdown menu as in Figure 20. This will immediately bring up the window in Figure 21. This window allows you to create a logic circuit using the various nodes that you are probing with SignalTap.

| trigge | er: 2007 | 7/05/22 14:11:40 #0 | 🚅 Allow all changes |                |                |  |  |  |  |  |

|--------|----------|---------------------|---------------------|----------------|----------------|--|--|--|--|--|

|        |          | Node                | Data Enable         | Trigger Enable | Trigger Levels |  |  |  |  |  |

| Туре   | Alias    | Name                | 8                   | 8              | 1 🔽 Advanced 🗸 |  |  |  |  |  |

|        |          | SVV[0]              | <b>N</b>            | N              |                |  |  |  |  |  |

|        |          | SVV[1]              | <b>N</b>            | N              |                |  |  |  |  |  |

|        |          | SW[2]               | <b>N</b>            | N              |                |  |  |  |  |  |

|        |          | SW[3]               | <b>N</b>            | N.             |                |  |  |  |  |  |

|        |          | SW[4]               | <b>N</b>            | <b>N</b>       |                |  |  |  |  |  |

|        |          | SW[5]               | V                   | <u> </u>       |                |  |  |  |  |  |

|        |          | SW[6]               | <b>N</b>            | ম              |                |  |  |  |  |  |

|        |          | SW[7]               | V                   | ম              |                |  |  |  |  |  |

Figure 20. Select Advanced from the Trigger Level dropdown menu.

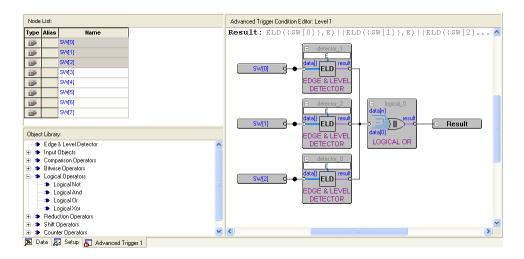

| Node   | List:     |                                 | ^ | Advanced Trigger Condition Editor: Level 1 |   |

|--------|-----------|---------------------------------|---|--------------------------------------------|---|

| Туре   | Alias     | Name                            |   | Result:                                    | ^ |

|        |           | SW[0]                           | _ |                                            |   |

|        |           | SW[1]                           |   |                                            |   |

|        |           | SW[2]                           |   |                                            |   |

|        |           | SW[3]                           |   |                                            |   |

|        |           | SVV[4]                          | _ |                                            |   |

| n S    |           | SVM51                           | × | –∋ Result                                  |   |

| Object | t Library | y:                              |   |                                            |   |

|        | Edge      | & Level Detector                |   |                                            |   |

|        |           | Objects                         |   |                                            |   |

| ±      |           | arison Operators<br>e Operators |   |                                            | _ |

| ±      |           | al Operators                    |   |                                            |   |

| ÷      |           | ction Operators                 |   |                                            |   |

| +      |           | Operators                       |   | Object has an incorrect number of inputs.  | ~ |

| ÷      | Count     | er Operators                    |   |                                            | > |

Figure 21. The Advanced Trigger editing window.

4. In the node list section of this window, highlight the 3 nodes SW[0] to SW[2], and click and drag them into the white space of the Advanced trigger window, resulting in Figure 22. Note that you can also drag and drop each node individually.

| Node   | List:     |                                 | ^           | Advanced Trigger Condition Editor: Level 1 |

|--------|-----------|---------------------------------|-------------|--------------------------------------------|

| Туре   | Alias     | Name                            |             | Result:                                    |

|        |           | SW[0]                           |             | SW[2]                                      |

|        |           | SW[1]                           |             | SW[1]                                      |

|        |           | SW[2]                           |             | SW[0]                                      |

|        |           | SW[3]                           |             |                                            |

|        |           | SW[4]                           |             | SW[0] d-                                   |

|        |           | SW[5]                           | <b>&gt;</b> |                                            |

| Object | t Library | y:                              |             | SW[1] d= tesuit                            |

| •      | Edge      | & Level Detector                |             | SW[2] d-                                   |

| ÷      |           | Objects                         |             |                                            |

| + - +  |           | arison Operators                |             |                                            |

| ÷      |           | e Operators                     |             |                                            |

| + +    |           | al Operators<br>ction Operators |             |                                            |

|        |           | Operators                       |             | Object has an incorrect number of inputs.  |

| ÷      |           | er Operators                    |             |                                            |

| 🔊 Da   | ata 🔀     | 🛛 Setup 🚮 Advanced Tri          | gger 1      |                                            |

Figure 22. The three input nodes of interest dragged into the Advanced Trigger Editing Window.

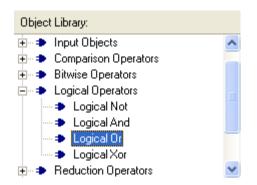

5. We now need to add the necessary logical operators to our circuit. We will need an OR gate as well as three edge level detectors. To access the OR gate, click on the plus sign next to Logical Operators and select Logical Or, as in Figure 23. Then drag and drop the operator into the editing window.

Figure 23. Select the Logical Or operator from the Object Library window and drag this into the editing window.

6. In the object library click Edge and Level Detector and drag this into the editing window. Do this three times and then arrange the circuit as in Figure 24. The three inputs should each be connected to the input of an edge and level detector and the output of each of these detectors should be connected to the OR gate. The output of the OR gate should be connected to the output pin already in the editing window.

Figure 24. Arrange the elements to create a circuit that looks like this.

7. We now need to set each edge and level detector to sense either a falling edge or a rising edge. Double click one of the edge and level detectors, bringing up the window in Figure 25. Type E in the setting box and then click OK. This will mean that the detector will output 1 whenever there is either a falling edge or a rising edge of its input. Repeat this step for the two remaining edge and level detectors.

| 💾 Object Pro                                                     | perties                                         |                          |

|------------------------------------------------------------------|-------------------------------------------------|--------------------------|

| General Paran                                                    | neters                                          |                          |

| Parameter<br>Name:<br>Setting:<br>Description:<br>Existing param | Reset<br>Reset All<br>re<br>its.<br>ters:<br>e, |                          |

| Name:                                                            | Setting:                                        | Configurable at runtime: |

|                                                                  | Detector Pattern E                              | Always                   |

| Pipeline                                                         | 0                                               | Never                    |

|                                                                  |                                                 | OK Cancel                |

Figure 25. Type E in the setting box so that the function triggers on both rising and falling edges.

8. To test this Advanced trigger condition, compile the designed circuit again and load it onto the DE2 board. Then run Signal Tap as described in the previous section. You should note that the Analyzer should sense every time you change one of the first three switches on the board.

## 5 Sample Depth and Buffer Acquisition Modes

In this section, we will learn how to set the Sample Depth of our analyzer and about the two buffer acquisition modes. To do this, we will use the previous project and use segmented buffering. Segmented buffering allows us to divide the buffer into a number of separate, evenly sized segments. We will create a sample depth of 128 bits and divide this into four 32-sample segments. This will allow us to capture 4 distinct events that occur around the time of our trigger.

- 1. Change the trigger condition back to Basic and have only one trigger level. Make the trigger condition to be at either edge of SW[0].

- 2. In the Signal Configuration pane of the SignalTap II window, in the Sample depth section of the pane select 256 from the dropdown menu. This option allows you to specify how many samples will be taken around the triggers in your design. If you require many samples to debug your design, select a larger sample depth. Note, however, that if the sample depth selected is too large, there might not be enough room on the board to hold your design and the design will not compile. If this happens, try reducing the sample depth. At a sample depth of 256 you should have no problems in compiling our example design.

- 3. In the Signal Configuration pane of the SignalTap II window, in the Buffer Acquisition Mode section of the pane select Segmented. The default option for Buffer Acquisition Mode is circular, and this is the mode that would have been selected in the previous parts of this tutorial. In the dropdown menu beside Segmented, select 8 32 sample segments. This will result in a pane that looks like Figure 26.

| Clock: CLOCK_50                                                                               |

|-----------------------------------------------------------------------------------------------|

| Data:<br>Sample depth: 256 💌 RAM type: Auto                                                   |

| Buffer acquisition mode:<br>Circular: Pre trigger position<br>Segmented: 8 32 sample segments |

| Trigger:                                                                                      |

| Trigger levels: 1                                                                             |

| Source: SW[0]                                                                                 |

| Pattern: Don't Care                                                                           |

| Trigger out:                                                                                  |

| Target: auto_stp_trigger_out_0                                                                |

| Level: Active High                                                                            |

| Latency delay: 4 cycles                                                                       |

|                                                                                               |

Figure 26. Select Segmented buffer acquisition mode with 8 32 sample segments

- 4. Recompile and load the designed circuit onto the DE2 board. Now, we will be able to probe the design using the Segmented Acquisition mode.

- 5. Go back to the SignalTap II window and click Run Analysis. Now, flip SW[0] up and down, and in between flips change the values of the other 7 switches. After you have done this 8 times, the values in the buffer will be displayed in the data window, and this will display the values that the 8 switches were at around each trigger. A possible waveform is presented in Figure 27. This resulted from the user flipping up one more switch between each flip of SW[0].

| log: 2007/05/28 13:27:02 #0 |       |        |   | click to insert time bar |   |  |    |      |      |   |  |    |   |  |     |    |   |

|-----------------------------|-------|--------|---|--------------------------|---|--|----|------|------|---|--|----|---|--|-----|----|---|

| Node                        |       |        | 0 |                          | 1 |  | 2  | 3    | 3    | 4 |  | 5  | e |  | 7   |    | 8 |

| Туре                        | Alias |        | 0 | 16                       | Q |  | Q. | 16 C | ) 16 |   |  | 16 |   |  | , O | 16 | 0 |

|                             |       | SW[0]  | Г |                          |   |  | Γ  |      |      |   |  |    |   |  |     |    |   |

|                             |       | SW[1]  | Г |                          |   |  |    |      |      |   |  |    |   |  |     |    | ٦ |

|                             |       | SW[2]  |   |                          |   |  | 1  |      |      | 1 |  |    |   |  | 1   |    | ٦ |

|                             |       | SW[3]  | L |                          |   |  |    |      |      |   |  |    |   |  |     |    | ٦ |

|                             |       | SVV[4] | Ĺ |                          |   |  | Ì  |      |      |   |  |    |   |  |     |    | ٦ |

|                             |       | SW[5]  | Ĺ |                          |   |  |    |      |      |   |  |    |   |  | 1   |    | ٦ |

|                             |       | SVV[6] | Ĺ |                          |   |  |    |      |      |   |  |    |   |  | 1   |    | ٦ |

|                             |       | SW[7]  | Ĺ |                          |   |  |    |      |      |   |  |    |   |  |     |    | ٦ |

Figure 27. Possible waveforms that could result when using the Segmented Acquisition mode.

Copyright ©2007 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

This document is being provided on an "as-is" basis and as an accommodation and therefore all warranties, representations or guarantees of any kind (whether express, implied or statutory) including, without limitation, warranties of merchantability, non-infringement, or fitness for a particular purpose, are specifically disclaimed.