Audio

Visualization

Final

Project – ECE 5760

Michael

Lyons – mpl56

Darbin

Reyes – der34

Introduction

The goal of our project was to input

a signal in the DE2 board, whether it be music, conversation, or noise, and be

able to analyze the signal to display visuals on the VGA output in real time. The

main focus and testing for this project was done on music being played through

a computer. The setup used for the project was a DE2 board, the on board audio codec,

and VGA display driver with an external monitor. The setup would have the user

input their music on the board line in and then the logic of our project would

output visuals on the VGA port according to the signal coming in. Once the

signal was input into the line in signal differentiation was needed and done by

amplitude, frequency, and period. Using these different measures for the

incoming signal the user selected from various visualization schemes to

display. The amplitude of the incoming signal over time was converted to a

logical mapping for the VGA and allowed for different size objects on the VGA

display. Frequency and period being very closely related were dealt with in

different ways. For frequency we used five filters in order to separate the

incoming signal into three bands. The bands corresponded to bass, cymbal, and

vocals and depending on amplitude and content in each band the display showed

different patterns and colors accordingly. The final measurement, period, was

used in a different way for the variation of the pixel colors on the VGA

display. Depending how long the period was the color schemes would change

according to that pace. The variation of pixel color was also done at faster

paces, so if the beat detected occupied quarter notes pace the colors could

change with a quarter note, half note, whole note, and two half notes. The

exact timing of each note is not necessarily accurate; however, relative pacing

or beats per minute (bpm) of the music was the goal. The reason this project

was chosen was because audio visualizes are common to find but do not

necessarily correspond to the music being played. The goal of this project was

to create visuals that actually followed the music for a better listening

experience.

High Level Design

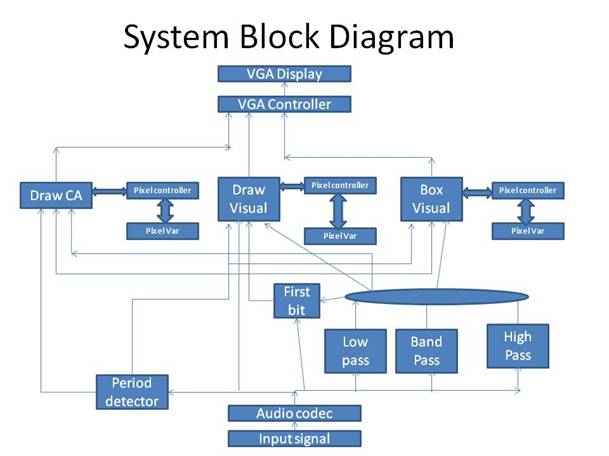

The critical path of this project

was to take an input signal from the audio codec and then send this signal

through various calculation and visualization modules to produce an output on

the VGA display. The block flow diagram of the high level design can be seen

below in Figure 1.A second more precise visualization unit was also created and

is explained in the hardware section and used for obtaining accurate and simple

results. The first unit that the audio input signal was sent to the period

calculation unit in the top module. The period calculation unit repeatedly

finds the period on the expiration of a timer and stored the largest period

found in a register. The period calculation was done through the method of zero

crossing. Before detecting zero crossing the audio signal had to be low passed

and down sampled so that only low frequencies could be used to figure out the

period. Using the low frequencies is beneficial because it gives a good

estimate of the beat of the song. With the beat of the song one can change

images and colors in a period manner with the music being played. In order to

accomplish finding the period to estimate beats per minute a CIC filter was

used to low pass and down sample to the audio clock. From there the signal was

down sampled even more using a thousand hertz. According to the Shannon’s

sampling theorem this would only allow frequencies of up to 500 Hz to be

detected. A frequency from 500 Hz and down is the bass range of the music where

the beats can usually be found. After the filtering and down sampling are

completed three zero crossings are found so that an entire period is traversed

and the resulting number of clock cycles is used to judge beats per minute

which is then used to change the image as well as the color on the screen.

The

audio signal is also sent into three low pass chebychev filters each with a

different cutoff frequency for their respective ranges of: bass, cymbal, and

voice. The filters used were all infinite impulse response filters. The cymbal

filter used a four pole eighteen bit infinite impulse response filter which was

for the highest frequency range. The bass and voice filters both used a four

pole twenty seven bit infinite impulse response filter because the cutoffs

needed to be very exact considering the ranges were tight on the lower end. Details

about the filters can be found in the hardware description section below. The

cymbal and voice filters required two filters to create a pass band while the

bass filter was a single low pass filter

At

the same time the audio input enters the three filters the signal also goes

into an absolute value unit and then a height mapping unit. The absolute value

unit takes the absolute value of the incoming signal and then sends it to the

mapping unit where the height is converted to a height mapping of the VGA

screen. The absolute value unit takes

the absolute value of the current input signal by checking the first bit and

makes sure that it is zero. Once the signal has been made positive it goes into

the height mapping module which looks for the highest order one and once found the

unit outputs height that corresponds to a pixel quantity for the y axis on the

VGA display. The resulting height allows visuals to be drawn with heights that

are proportional to the incoming audio signal. The three audio filters

mentioned in the paragraph above are also put through these two units to output

their corresponding heights.

Figure 1: High Level Flow Diagram

After the filtering, period

calculation, and height mapping the audio signal is then sent into three

different display modules selectable by the user. The first of these modules is the “Cellular

automaton module” which takes the period, the audio input, and the three

filtered signals. The Cellular automaton unit draws a cellular automaton on the

VGA display. A Cellular automaton is an algorithm where the next line on the

VGA screen depends on the previous line on the VGA screen. How the next line on

the screen is determined is based on the current line’s values. Beginning with

an initial value, which in the case of our implementation could be either one

block in the center or a horizontal line of random values, the next horizontal line

will be set values based on the horizontal line that came before it. How the

next horizontal line is set based on the previous line is done with a rule that

is from zero to two hundred and fifty five or eight bits. Each rule can be

represented by an eight bit number. Each bit in that eight bit sequence can be

reached with a three bit number that represents its offset within the eight

bits. For instance the fourth bit has the sequence 3’b100 associated with it. When

given a rule in eight bits the offset sequence is contained in the previous

line. When traversing a horizontal line the three bits or pixels in this case when

referring to an LCD screen, the pixel above the current one is checked as are

the pixels immediately to the left and right of the pixel right above. If any

of these pixels is encoded as drawn then that bit is set high in the three bit offset.

If the bit offset into the rule is a one then the current pixel on the screen

is to be filled in. If the bit offset into the rule is a zero then the current

pixel is to be black. In our implementation of the Cellular Automaton the rule

is dictated by the high order bits of the period and the color of the current

pixel is not black or white but based off either output from a pixel value

controller or from the various audio signals contained within the project. The

various rules calculated and colors generated produce an array that is stored

in SRAM. The VGA then reads the values out of the SRAM if the Cellular Automaton

visualization is selected by the user.

The second of the visualization module

is the “draw bars” module which takes in the period of the signal, the audio

input, the three filter outputs, and the height bit mapping of the audio input

signal, the bass filter, cymbal filter, and voice filter outputs. Once all of

these calculated values are read into this module the current section of the

screen VGA is trying to set is traversed and as it is the draw bars

visualization figures out what to draw in the current location the VGA is

looking for. In other words the VGA looks over the entire screen from the top

left down to the bottom right. The module for the VGA outputs the current

location that it is looking for and this is an input into the module. Based on

this value the module finds out its current offset across the screen and the

corresponding height bit mapping for that location on the screen and if the

height mapping includes the current location then the pixel controller unit

outputs a new pixel value to the VGA display. The draw bars visualization draws

one hundred bars across the VGA display representing past values of the audio

input signal. The current sample of the audio signal is stored in the first

height map register and as more samples are loaded in, the sample in the first

register is passed to the next bar height register. In this manner the height map

value is passed down the bar height register chain and the height is propagated

across the screen. In this manner the magnitude of various parts of the input

audio signal can be seen over one hundred redraws of the screen at one time. In

addition to the bars being drawn across the screen there are two “eyes” at the

top of the screen that change in size with respect to some of the height

registers of the bars to represent the frequency of change in the magnitude of

the current signal being displayed by the bars. The colors in which both the

bars and “eyes” are filled in with can be changed by the user. The user can

choose to have the pixel controller run through its basic algorithm to change

the pixel colors or the user may select the available audio signals to dictate

the current color change. With this unit it is very clear to tell the

magnitudes and how the waveform progresses over time but the period is a bit

abstract since it is only used in the default algorithm to change the pixel

color scheme. When this visualization and color scheme are selected by the user

the unit will produce red, green, and blue pixel values which are output by the

unit and onto the VGA display.

The third of the visualization

modules is the “box visual module” which takes in the current calculated

period, the input audio signal, and the filtered bass, cymbal, and voice signals.

The “box visual module” also takes in the coordinates being traversed by the

VGA controller and tracks the current position on the screen and divides the

screen up into four concentric rectangles instead of draws bars and eyes. The

concentric rectangles are drawn using a grid fashion and depending on the rectangle

in the grid the VGA controller is currently traversing it is filled in with

pixel values from the pixel controller. Each rectangle on the grid not only can

change its color using the pixel controller but it can change in size. The grid

is divided up to the various audio input signals. The outer most edge’s blocks

in the grid all have their widths modulated from the left and right by the audio

input signal’s, from the line in, top four bits not including the sign bit. The

inner most grid component in the center of the screen has its width and height,

of both sides, modulated by the filter voice signal’s top four bits not

including the sign bit. The second most inner rectangle has its width modulated

from both sides by the top four bits of the cymbal input signal. The height on

the other hand is not modulated in all section of this rectangle. Only in the

bottom and top row of the second most inner rectangle is the height adjusted

for the top four bits of the cymbal audio input. The second most outer

rectangle works in a similar manner as the last rectangle but the width in both

direction modulated by the top four bits of the bass input signal. Only the

bottom and top rows of this rectangle are modulated in height by the top four

bits of the bass input signal. The top four bits of the inputted signals do not

include the sign bit so that magnitude is the measure seen when changing the

grid block size.

After all the visualization modules

red, green, and blue pixel values are all set and read into the VGA controller

appropriately to the visualization scheme selected by the user. The VGA

controller then outputs the created display onto the LCD display in the lab. The

pixel color values seen on the VGA display are drawn either from audio and

filter inputs or from the pixel controller instantiated along with each

visualization module. The goal of the pixel controller is to dictate how

quickly the “pixel variater” steps through its various pixel encoding schemes. The

“pixel variater” steps through the different combinations of colors over time

based on the current scheme passed in by the pixel controller. The speed at

which the schemes change is dictated by a counter that terminates by a multiple

of the period. Finally, other than the filters and filter generated code, audio

codec, and VGA modules given to us previous in the ECE5760 lab, there are no

existing patents, copyrights, or trademarks associated with our project. There

are also no standards used in our project.

Hardware

Referring the high level design flow

and starting from the input signal we can begin to traverse the hardware used

for this project. The input signal goes into the audio codec which is then

input into the FPGA chip on the DE2 board which allows the audio signal

available for manipulation and analysis. The inputted audio signal in our

design can be directly placed on the output line depending on the selection of

switches 16 through 14. This is a three bit value that when that choose the

output to be the output of the CIC filters, the audio signal input, the cymbal

filter output, the bass filter output, the voice filter output, and the 1000 Hz

sampling of the audio input signal for the numbers zero to five respectively. If

none of these values are selected using the switches then nothing is output on

the left channel of the line out. On the right channel the same content is

placed as was placed on the left channel.

The input from the audio codec is

also used in a top module section of code known as the period calculator. The

period calculator takes the audio input signal from the left channel and

attempts to find the low frequency periodicity of the signal. The first step in

completing this task is to filter the audio signal input through a second order

CIC filter. CIC filters were used in lab two of ECE5760 and won’t be discussed

in great detail here. The purpose of the second order CIC filter is to low pass

the signal using the twenty seven megahertz clock and the audio clock. The second

order CIC filter also down samples the signal to the audio clock and then

outputs the corresponding signal on the ‘oCIC’ wire. After the low major section of the period calculator

code is entered, which is an always blocks in the top level module at the

positive edge of the fifty megahertz clock. The first task for the period

calculation is to down sample the second order CIC filter output even further. In

this loop the count, hzCount, is used to create a 1000 Hz clock by switching

the register value of clk1000 every 25000 clock cycles. This creates a 1000 Hz

clock signal which will be used to, based on the Nyquist sample rate, to remove

all frequencies above 500 Hz. With all the high frequencies removed the hardware

can now calculate the period of this low frequency signal by looking for three

zero crossings in a row. Three zero crossings in a row traverses one period

because in one period a sinusoid will cross the time axis three times. The

crossing of the time axis can occur in the sequence of below, above, below or

above, below, above and the period is the number of cycles between the going

below samples or the going above sample respectively.

Before

looking into the state machine it is worth noting that when the system is reset

the maxPerLength, prevSample, and newMax are all set to zero and state1000 is

set to firstSample. The maxPerLength is

the maximum period length recently measured. The prevSample is the previous

sample that was in the register sample1000 and newMax is a counter that

dictates when a new value should be placed in maxPerLength. Other registers

used are periodCount, periodLength, state1000, and modIn which are the period

cycle count, current period length measured, the current state of the period

calculator, and the down sampled audio signal from 50 MHz to 27 MHz. After the

reset is no longer being pressed the state machine samples the sinusoid when

the 1000 Hz clock is high and then goes to second state of fristCross which

checks to see if between the pervious sample and the current sample if there

was a change in sign. When there is a change in sign it shows that there is a

crossing of the time axis because the magnitude goes from positive to negative.

If there is no change then the current sample is stored in previous sample and

the firstSample state is returned to. If a zero crossing is detected in either

direction the periodCount is reset to zero. The periodCount is a 32 bit

register which is used to measure how many clock cycles the period is. The

current sample (sample1000) is stored in the prevSample register and the

state1000 progresses to secondSample. In secondSample a similar action as in

firstSample is taken where if the clk1000 signal is high then a new sample from

the second order CIC filter is obtained and the secondCross state is entered. The

secondCross also attempts to see if there is a zero crossing and returns to the

secondSample state if there is no zero crossing. If there is a zero crossing

then sample1000 is stored in prevSample and the state1000 is changed to

thirdSample. In state thirdSample it also waits to obtain a new sample when the

clk1000 is high and otherwise simply wait until the clk1000 is high. Once the

clk1000 is high the thirdCross state is entered and if no zero crossing is

detected then it returns to the thirdSample state. If a zero crossing is

detected then the periodCount is stored in periodLength. The periodLength is

compared to maxPerLength which stores the maximum period measured in this

interval so far. Storing the maximum period allows us to obtain the lowest

frequency possible which is useful for measuring the amount of time between the

bass beats in the music. Then the newMax value is increment and checked to see

if it has reached 1000 yet. If the newMax register has reached 1000 then maxPerLength

is step to 1000 and newMax is set back to zero. The newMax count is implemented

because most audio signals are dynamic and will have a constantly changing

lowest frequency so it is useful to want to measure a new maxPerLength every so

often to allow the visualization to keep pace with the current audio signal. The

maxPerLength register is then put on the hex displays for the user to view.

Audio/Video

Synchronization

A

filtering scheme was developed to facilitate synchronization of the music to

what is being drawn on the screen. While common audio visualizations do not

stress synchronization, this scheme does. We found that for the user to easily

notice the synchronization between the music and the screen, the drawing had to

remain simple. As such, the visualization schemes for which the audio and video

are visually in synch the drawing was kept simple. On the other hand, to add

visually complex visualizations, we had to sacrifice synchronization with the

audio. With the complex scenes, the synchronization is not immediately obvious,

but the presented visualization is modulated by the audio to produce variation

on the screen. The following explains the filtering scheme developed to produce

audio visualizations for which the synch is obvious. The visualization schemes

that focused intensely on simplicity of visuals and synchronization with the

music are explained below under the simple visualization section.

Filtering

Scheme

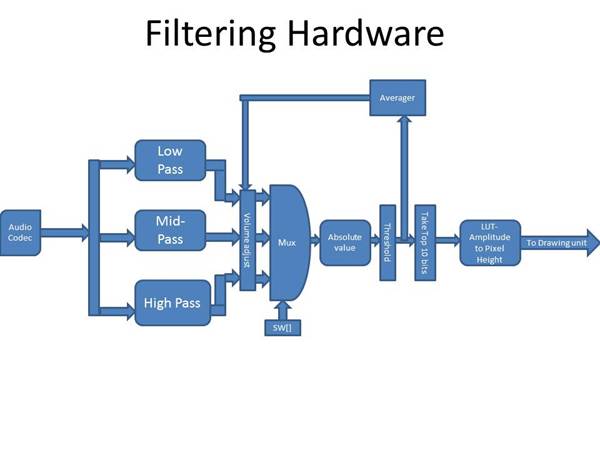

Figure 2: Filtering Hardware

The filtering

scheme seen above was used in a separate hardware module for simple

visualization and is separate from the main part of the hardware shown in the

flow diagram in the high level design. The filtering scheme has five main

components:

1)

A

filter bank with 3 filters. Low pass, band-pass, High Pass.

2)

Volume

adjustment module.

3)

Absolute

value unit

4)

Thresholding

5)

Conversion

to bar height

The

filter bank contains three Chebychev, fourth order, infinite impulse response

(IIR) filters. The verilog implementation of these filters was taken from the

ECE5670 website here:

http://instruct1.cit.cornell.edu/Courses/ece576/DE2/fpgaDSP.html

The cut-off

frequencies were chosen by testing the filters in Matlab on various songs. The cheby1() function in Matlab was used to

do this. The final normalized cutoff frequencies used were:

Chebychev Low Pass: .03

Chebychev Band Pass: .02-.05

Chebychev High Pass: .5-.6

With the audio

codec running at 16bit resolution and 48KHz.

During

testing of the filter output, we observed that although the desired frequencies

were filtered, each filter unequally attenuated the input. For example, even

when the high pass filter input contained significant amounts of high frequency

sounds (e.g. cymbal beats), these frequencies were barely audible relative to

the other filter outputs. This problem

was easily solved by manually increasing the volume, however we found that it

easy to develop a method for automatically adjusting the volume. The scheme for

volume adjustment is simple. We take the average of the absolute value of the

filter output and increase the volume if it is below a certain threshold. The

amount of volume increase is proportional to how far the filter output is from

the threshold. The absolute value unit then takes the absolute value of its

input. This is a significant step toward visualizing the audio. It is easier to

modulate visuals on the screen with a signal that is proportional to the

absolute value of the audio amplitude.

Using a threshold comparison on the absolute

value of the audio signal is used to accomplish three tasks. First, it is used

to prevent noise because even when there is no audio input, the audio line-in

produces non-zero values due to noise. This caused unwanted random modulation on the

screen. This issue was solved by continuously averaging the absolute value of

the input over a half second period which acts as a low pass filter. If this

average is below a certain threshold, the input is considered zero. We also

threshold the absolute value of the filter output to ensure that the modulation

used for drawing is not too hectic. This makes it easier to identify drum beats

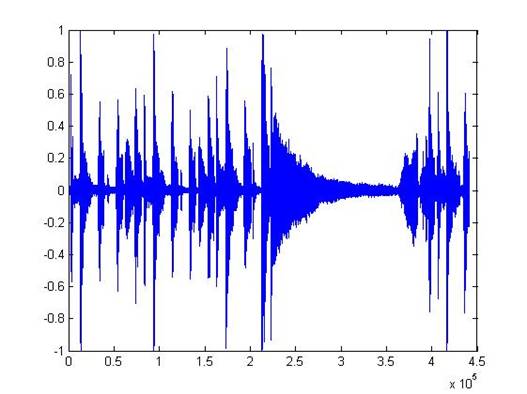

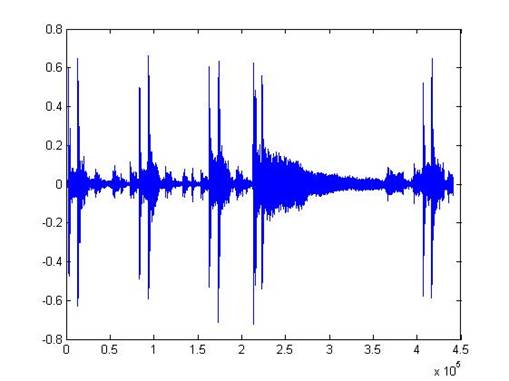

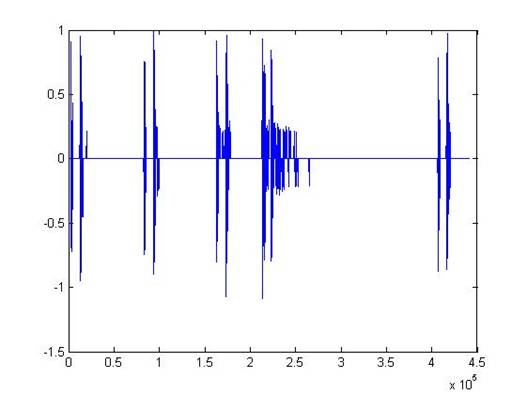

in the signal. This can be easily illustrated in Matlab. The following figures show the original

input, the low pass filtered input, and the thresholded low pass filtered

input. The peaks in the figure where a threshold is used correspond very

closely to the drum beats in the music. The resulting signal can be used

successfully to create audio visualizations which are in sync with the music.

In general, this scheme allowed us to isolate drum beats from the low pass

filter, voice and guitar from the band pass filter, and cymbal beats with the

high pass filter.

Figure 3: Raw audio input.

Figure 4: Low pass filtered

Figure 5: Low Pass filtered with

threshold

Lastly,

to implement a bar visualization scheme, the filter with a threshold output was

run through a look up table (LUT) to associate it with a bar height. The final

place where the audio input signal is used besides the visualization module is

in the height mapping process. The three filter range outputs are also put

through the height mapping process as well. The first step for all four of the

signals to be height mapped is to send them all through an absolute value unit.

Each absolute value unit makes sure the highest order bit is zero or that each

output from the absolute value unit is positive. These outputs are then fed

into firstHbit height mapping module. This module finds the highest order bit

that is a one and then sets the corresponding mapping to a pixel amount

vertically on the screen. The mapping computed here is used to send data to the

VGA controller that is coordinate specific and is described below in the simple

visualization section.

Audio

Codec

The audio codec used for this project

included five files which were AUDIO_DAC_ADC.v, I2C_AV_Config.v,

I2C_Controller.v, Reset_Delay.v, and VGA_Audio_PLL.v. The use of this hardware

was to be able to send and receive sixteen bit signals from the line out and

line in ports on the DE2 board. The input audio signal is run into the DE2

board for calculation and then can be output again by the user on the speakers

in lab so both listen and watch the music unfold in front of you.

VGA

Controller

The VGA controller used for this

project included four files VGA_Controller.v, VGA_Param.h, Reset_Delay.v, and

VGA_Audio_PLL.v. The reset delay and PLL files are duplicate files used between

both the audio codec and the VGA controller. The VGA controller had a clock

that was used to coordinate the cellular automaton drawing. Also the VGA

controller’s current x and y coordinates were used to place pixels to of a

certain color on the screen. If the coordinate values were in between

particular ranges then a certain color scheme could be used to fill in the LCD

display. The pixel values were read into the VGA controller using the mVGA_R,

mVGA_G, and mVGA_B tens bit signals.

SRAM

The SRAM in this project is

implemented as a bunch of wires in the top module. The SRAM_ADDR is set using

the eighteen bit addr_reg register which is assigned by the Cellular automaton

visualization unit. The SRAM_DQ is either tri-stated to read out of memory or

set to the sixteen bit data_reg register to write the value to memory. The

write or read functionality is done with the we register which dictates whether

a write to memory is enabled or not. The rest of the wires, such as SRAM_UB_N,

SRAM_LB_N, SRAM_CE_N, and SRAM_OE_N are set to zero. The SRAM is used for

writing an image to the SRAM and then reading it out onto the VGA display using

the Cellular automaton visualization unit.

Cellular

Automaton Visualization

The Cellular Automaton Visualization

is an instantiated processing unit in the top module since the attempt to place

it in separate module was unsuccessful. Towards the beginning of this unit is

where the reset wire is assigned. The reset is set to ~KEY[0] so that the

entire system can be restarted based on the users input. After the reset wire

there is one other wire instantiated which is x_low_bit which is used for the

pseudo random number generator. The pseudo random number generator which takes

a thirty one bit registers (x_rand) and xors the thirteenth and twenty seventh bit

together and shifts this value in the bottom of the x_rand. This pseudo random

number generator is used to instantiate a random first line for the cellular

automaton initial condition to be used to progress the cellular automaton

across the screen. The registers created for this visualization were addr_reg,

data_reg, we, state, lock, rule, randinit, x_walker, y_walker, and sum. The

addr_reg is eighteen bits and used to send address to the SRAM module. The

data_reg is sixteen bits and used to send data to the SRAM over the SRAM_DQ

bus. The we register is used to dictate the SRAM_WE_N wire and can tell the

SRAM whether or not to write the value on the data bus or not. The state

register is four bits and is used to move through the state to draw the current

cellular automaton image. The lock register is one bit and used to lock in a

calculation of another cellular automaton pixel. The rule register is eight

bits long and is used to dictate the current cellular automaton rule to

implement. The randinit one bit register is used to tell the visualization

scheme to start with a random initial condition or not. The x_walker and

y_walker registers are both eight bits and are used to traverse the SRAM to

write values into SRAM so they can be read appropriately and sent to the VGA

display. The final register, sum, is a three bit register which is used to

index into the rule to figure out if the pixel currently being looked at is to

be colored or made black.

The Cellular Automaton function runs

as an always block on the posedge of the VGA_CTRL_CLK and the first thing done

in this section is to sample the audio in and bass, cymbal, and the voice filtered

audio signals. These are sampled at both five bits and fifteen bits. These

values are used later on for color schemes to be written to the SRAM for

display on the VGA display. Upon reset the address register is set to the current

coordinates of the VGA controller. The we, data_reg, and rand are set to zero. If

the randinit is high or then start the x_walker and y_walker either start in

the top left or over by one pixel to draw the intial condition respectively. The rule on reset is set to one and the state

is set to test1. If reset is not pressed then the module will check to see if randinit

is pressed and the rand register is high then we assign a random sequence of

pixels to the first line of the LCD display. A random line is done by checking

the highest bit in the x_rand register and if one it places color in the pixel location

and otherwise it makes the pixel black. After the addr_reg and data_reg are set and we

is set to write the value will be written and this short section will increment

x_walker until it reaches the end of the line and resets the x_walker and y_walker

to the top left corner at (1,0) and sets the randinit low and we high to stop

writing memory. If rand is not high then a single pixel in the center of the

screen is written as another initial condition possibility. The data written in

this cellular automaton is not white or black pixels but pixel color is chosen

either from the current audio signals or from a pixel controller unit but when

a pixel is filled in the most significant bit is still written in as one and

that is used to check for how to fill in the next line on the screen.

After the randinit section the main

state machine can be seen that is run when either the VGA vertical and

horizontal sync is active low which reduces the jitter in the image. The state

machine then begins where it enters the state test1. This state does not allow

a memory write, sets the lock bit high so we know a pixel is being calculated,

the sum is reset to zero, the addr_reg is set to the {x_walker, y_walker}, and

finally the state is set to test2. In test2 we check the lock bit and if it is

not high then we return to start test1. If the lock bit is set then we place

the most significant bit of the SRAM_DQ into sum[1] for the first part of the

rule offset. The addr_reg is set to {x_walker-1, y_walker} and then the state

is set to test3. In test3 Once again the lock bit is tested similarly as

before. Once again the SRAM_DQ’s most significant bit is checked and place into

sum[2]. The addr_reg is set to {x_walker+1, y_walker} and state is moved to

test4. In test four we once again do the lock bit and then SRAM_DQ’s most

significant bit is placed in sum[0] and then the state is change to

draw_walker. In draw_walker we also check the lock bit and if it is set then we

set a memory write the addr_reg is set to {x_walker,y_walker+1}. Next the rule

is offset with sum (rule[sum])and if it is one then a pixel combination is written

into SRAM based on what the user selected. If the user selectes zere, one, two,

three, or four the pixel value written is either sample of all three filter

outputs, base filter output, cymbal filter output, voice filter output, or

audio inputs. If none of the options before are selected then a pixel

controller output is written to SRAM. If the sum offset into rule is not one

then a black pixel is written to SRAM. If the lock bit is not set then the state

machine remains in the draw_walker state but if a pixel is written to memory

then the update_walker state is entered where the x_walker and y_walker are

incremented appropriately across the screen. The x_walker is incremented by one

if it is less than 318 and then test1 is returned to. If the x_walker has

reached the end of the line or the value 318 then the y_walker is increment if

it is less than 237. The x_walker and y_walker are incremented as such until

they reach the end of the screen where the user_wait state is entered. In the

user_wait state if the user has selected this visualization then SW[1] &

SW[12] will be set high. The SW[1] is to select the CA module and the SW[12] is

to pause the progression if a cool image has appeared but that is a subjective

component on the user end. Also in user wait state the number of CA’s drawn is

larger than the maxPeriodLength then it is time to draw a new CA on the screen.

The countCA is set to zero and if SW[2] is high then the rule simply increments

otherwise the rule is dictate but bits 20 to 13 of the maxPerLength register. If

the rule is the max value and SW[2] is high then the rule is reset to one but

if not then the maxPerLength bits are used to dictate the rule. After this the x_walker and y_walker are reset

to zero. If rand is high then randinit is set and state is returned to test1. If

countCA has not reached the maxPeriodLength then this module remains in the

user_wait state until the timer has terminated. Finally if the reset, randinit,

or (~VGA_VS | ~VGA_HS) conditions are not met the CA sets the lock bit to zero,

sets the memory to read, and set the address register to the coordinates from

the VGA unit. This module will display CA’s at the beats of audio input and

images of this can be seen below in the results section.

Draw

Bars

The second visualization module

included in this project is draw bars which essentially shows the progression

of the audio codec inputs over time. The draw bars module has a lot of inputs

as it was actually capable of being placed in a sub module. The inputs into

this module are iHeight, iX, iY, iVGA_VS, iVGA_HS, CLK, VGACLK, AUDCLK, CLK27,

audIn, bass, cymbal, voice, RST, period, bassH, cymbalH, voiceH, and sigSel. The

iHeight, bassH, cymbalH, and voiceH are the all height mapping of the

audio_inL, the output from the bass filters, the cymbal filters, and the voice

filters after being run through the height mapping module. The iX and iY inputs

are the current coordinates coming from the VGA controller and are used to

detect which region we are currently writing to. The iVGA_VS and iVGA_HS are

the vertical and horizontal sync signals of the VGA controller and are used to

reduce jitter, if possible, and know when to redraw the screen. The CLK is the 50 MHz clock input. The VGACLK

is the VGA _CTRL_CLK input. The AUDCLK is the AUD_DACLRCK clock input. The

CLK27 is the CLOCK_27 clock input. The audIn, bass, cymbal, and voice inputs

are the sixteen bit audio signals from the audio input signal or one of three

filters. The RST is the reset from ~KEY[0]. The period is the period of the current

waveform. The outputs from this module are the state which was used for

debugging and the three ten bit VGA color outputs for red, green, and blue.

There are also a large number of

wires and register declared in this module. The wires red, green, and blue are

used for output from the pixel controller module and placed into the output to

the VGA controller if the current coordinates of the VGA controller wants are

to be colored. The next on the set of wires is one hundred one bit c wires

which are used for detection to see if the VGA controller is currently viewing

the coordinates within one of the columns to be drawn. After the declaration of

the hundred column wires there is the instantiation of one hundred ten bit

height registers which are used to keep track of the current magnitude of the

waveform and shift that magnitude across the screen as time increases. There is

one module instantiated inside of the draw bars and that is the pixelController

which is used to cycle through pixel schemes to keep the display fresh and new

all the time. After the instantiation of the pixelController all of the column

registers are assigned based on the current coordinates from the VGA

controller. Each column wire checks to make sure the y coordinate is above the

height register value and the x coordinate is between the six pixel bound

placed on the current column. There are

also two other wires used in this module to create eyes on the screen. The eyes

are two rectangles near the top of the screen and their condition is modified

based on either the bottom four bits of height_reg10 or height_reg20 depending

on whether it is eye1 or eye2. The conditions checked for the eyes vary the

rectangles size with each sample to pace their flashes with the music sampling.

The main part of this visualization

module is the always block on the positive edge of the 50 MHz clock. In this

section if the reset is high then all the height registers are set to zero and

the draw_state is set to init. If the reset is not high then a sampleCount is

incremented by one on each positive edge of the clock. In the init state if the

sampleCount is large than the bottom fourteen bits of the period then new

samples of the audio signals are taken. Also the first height register

(height_reg0) is set to one of the four height maps inputted into this module. If

the user selection is zero, one, two, or three then the height register used is

one for the audio input signal, the bass filter output, the cymbal filter

output, or the voice filter output respectively. The rest of the init state is

shifting all the registers values up one register which allows for the

progression of height across the screen. Finally the draw_state is set to

color. Then the color state is entered where we check if one of the one hundred

column conditions has been met or one of the eye conditions has been met and

not when the y coordinate from the VGA controller is divisible by ten. The

check to make sure the y coordinate is not divisible by 10 makes the bars

discretely different and significantly easier to draw. If this condition is met

then the current location from the VGA controller is shaded in with a color

which depend on the user input from SW[10:8]. If the switch value is zero then

the pixel controller values are outputted and if a value that is not checked

comes in then the pixel controller values are outputted. If the switch value is

one, two, three, or four then the audio input signal, bass filter output,

cymbal filter output, or voice filter output are used to output pixel values

respectively. In each case the red is set to the top ten bits of the signal

excluding the sign bit, the green is set to the inverse of the 12 to 3 bits,

and the blue is set equal to the bottom ten bits. If one of the eye conditions

are met and the SW[10:8] is zero then the pixel controller values are used with

eye1 using the inverse of blue and eye2 using the inverse of green. If the eye1

and eye2 have five, six, or seven as the selected input then top ten bits

without the sign bit are used in the following inverted combinations: bass,

cymbal, voice and cymbal, voice, bass and voice, bass, cymbal respectively. If

a column or eye condition is not met then a black pixel is sent to the VGA

controller. Finally in this module we wait in this state until the vs_sig is

set high and then the state moves back to init. The vs_sig register is set to

note the completion of the screen drawing which help remove as much jitter from

the screen as possible. The vs_sig is set using another state machine on

vs_state which waits for the falling edge of the VGA_VS clock to set vs_sig

high and then on the next cycle when it goes to state one sets the value back

to zero which allows for all the height registers to shift by one and then the

screen is drawn. Once the VGA_VS goes high again the state goes back to waiting

for the VGA_VS to fall again before shifting the height registers. At the end

of this module there are three assignments to output the pixel values on oR,

oG, and oB. This module successfully draws the height of the current signal

selected across the screen with two fluctuating eyes. Images of this can be

seen in the results section below.

Simple

Visualization

In the filtering section above

precise visual synchronization was a direct goal as part of this project. The

more complicated abstract visuals seen in the high level design worked out very

well but for precise coordination simpler visuals were needed. The simpler

visuals were drawn using a module similar to the draw bars module explained

above. For the simple visualization module which included the bars module but

in the simple module there were only twelve columns that were used and made a

simpler version of the draws bars seem above that followed a low passed version

of the height mapping. Another visualization scheme used was to draw a floating

box on the screen. On each run through of the draw bars state machine the

current x. On the other hand the y coordinate was added to by a larger quantity

based on the threshold of the music. Essentially the purpose was to have a box

gently float back and forth horizontally and when the beats passed over a

threshold the y coordinates of the box would be boosted and then slowly fall

again when the music did not surpass the threshold. This gave a very good

measure of the bass of the music. One final simple scheme used in this lab was to

create a single box in the center of the screen and fill it in with green

color. The coloring in the box varied, however, with the high frequency of the

music so you could get a feeling of the energy of the high frequencies in the

music being played. The code for this simple visualization can be found in the

appendix.

Box

Visuals

The third visualization module used is

the box visualization which shows the magnitudes of the audio input signal and

the output of all three filters implemented in the top module. The inputs into

this module are reset, CLK50, AUDCLK, VGA_VS, VGA_HS, audIn, cymbal, bass,

voice, coordX, coordY, and period. The reset is the reset from ~KEY[0]. The

CLK50, AUDCLK, VGA_VS, and VGA_HS are 50 MHz clock, the audio clock, and the

vertical and horizontal sync of the VGA respectively. The audIn, cymbal, bass,

and voice inputs are all sixteen bit audio signals from the audio codec and

three filters. The coordX and coordY or

the current coordinates from the VGA controller. Finally, period is the current

value of maxPerLength from the period calculator. This module only has three

outputs which are red, green, and blue which are all ten bit pixel values. The

boxVisual module has a number of registers called state, sample, sampleCymbal,

sampleBass, sampleVoice, region, redValue, greenValue, blueValue, and audCount.

The audCount is used to count a larger number of clock cycles before sampling

the audIn, cymbal, bass, and voice signal again to make the visuals do not move

too rapidly to destroy the user experience. The sample, sampleCymbal,

sampleBass, and sampleVoice are all the registers where the current samples are

kept for each of the respective input signals. The region register is used to

tell which region on the screen the VGA controller is currently traversing.

Where the VGA controller is will dictate what the pixel values that are

outputted will be. Finally the redValue, greenValue, and blueValue are all ten

bit registers that are set depending on the current region and output from the

module to the VGA controller. Finally

this module has twelve wires which are four red lines, four green lines, and

four blue lines which are used for the different color outputs of the pixel

controller to set four different colors depending on the region. The r0, r1,

r2, and r3 wires correspond to regions zero, one, two, and three which really

correspond to audio input signal, bass filter out, cymbal filter out, and voice

filter out.

The main part of this module is run

on the positive edge of the 50 MHz clock and the first item in this block is the

sampling section which was described above with the audCount. Next checking the

reset the state is set to locate. If the reset is not high then the locate

state is entered. In the locate function the VGA screen is divided up into a

grid of rectangle that are each 35 by 48 (y, x) pixels in size with grid blocks

on the end truncated if necessary. The purpose of locate is to set the register

region to know where we are on the screen. On top of the grid detection there

are four large concentric rectangles on the screen. The outer most rectangle

visualizes the audio input signal, then the bass filter output, then cymbal

filter output, and finally in the center and smallest voice filter output. For

each location check we first check what our current X coordinate from the VGA

controller is. Then after the X coordinate is checked the Y coordinate is

checked and from there we can tell which region we are in. The region can take

one of four values (but default cases are provided for assurance) in which zero

refers to the audio input signal, one refers to the bass filter output, two

refers to the cymbal filter output, and three refers to the voice filter

output. To add some variability in the regions

the current column corresponding signal has its four most significant bits (not

the sign bit) subtracted from the bounds of the column. This allows for the

thickness of each column to change. Furthermore the top and bottom rows of each

section also have the same top four bits subtracted from them. As a result each

of the four concentric rectangles changes their size differently depending on

the magnitude of their respective signal. Once the region register has been set the

state moves to color in which a case statement is used on the region. Depending

on the region a different color from a different pixel controller is used to

shade in that region. Not only do you have four different regions changing in

width and height differently but they also change in color differently. After

the appropriate color is placed in the redValue, greenValue, and blueValue

registers then the state goes back to locate. If none of the four regions are

satisfied the VGA displays black. The ten bit pixel values are output to the

top module and into the VGA controller.

Pixel

Controller & Pixel Variation

The three visualization units each

used this unit’s outputs to for color the pixel values to output to the VGA

controller. The goal of this module is to cycle through a variety of schemes

and output a long sequence of pixel values that do not repeat frequently. The

inputs into this module reset, VGA_VS, VGA_HS, CLK, CLK27, AUDCLK, schemeReset,

audIn, and periodIn. The reset is the ~KEY[0] from the top module. The VGA_VS,

VGA_HS, CLK, CLK27, and AUDCLK are all basic sync or clocks. The schemeReset

however is the value that the pixel controller sets to its schemeCycle register

when the hardware is reset. The schemeReset value is used so the controller can

start offset within the sequence of pixel values from another pixel variation

unit. The audIn in the audio input signal and the periodIn is the period of the

current audio signal from the period calculator. This module has three outputs

of red, green, and blue which are the pixel values to whatever module

instantiated it. The module also has three wires (redValue, greenValue, and

blueValue) that grab the pixel values from the pixel variation unit. This module does have a number of registers

called wtPrd, realPeriod, schemeCycle, and schemeCount. The wtPrd dictates the

current wait period selection for the pixel variation unit. The real period is

the period sent to the pixel variator which compensates for the change in color

taking 2^7 cycles and shifts the period down by that much to maintain the

colors and bass beat synchronization. The schemeCycle is the current scheme

wanted from the pixel variation unit. The schemeCount is the number of clock

cycle until the period is reached to increment the scheme to be sent to the

pixel variator.

The main chunk of this unit occurs

in the 50 MHz always block on the positive edge where is reset is pressed the

schemeCount goes to zero and the schemeCycle is set to the schemeReset value. If

the reset is not pressed then the schemeCount increments until it is larger

than eight times the period input which allows the user to enjoy a scheme for a

long period of time before changing the scheme. Once the schemeCount exceeds

its value it increments the schemeCycle by one and checks to see if the

schemeCycle is large than 254 and if it is the schemeCycle is set to zero. Also

when the schemeCycle reaches its last value the wait period is changed. The

wtPrd is incremented which allows for a different count time in the pixel

variation unit. The final operation the

pixel controller unit is to shift the periodIn down.

The pixel variation unit is similar

to the pixel controller unit in that it outputs the red, green, and blue pixel

values. The inputs into this unit at reset, VGA_VS, CLK, scheme, wtPer, and

period. The only inputs that are new here are the scheme and wtPer. The scheme

is the schemeCylce from the pixel controller and the wtPer is the waiting

period selector from the pixel controller. The scheme value is then dissected

into its meaningful values. Reverse, stat, alt, thirdVal, and mode are

extracted from the following from scheme as scheme[4], scheme[1], scheme[0],

scheme[3:2], and scheme[7:5] respectively. The pixel values in this unit are

set on the positive edge of the clock. Upon reset the count and all pixel

registers are set to zero. If the reset is not set and when the VGA_VS is low

the scheme values are extracted and then parsed into the pixel value wanted. First

the wtPrd chooses between how long to count clock cycles till outputting new

pixel values to slow the change in color or else it would change too fast and

make the users eyes hurt. After the wait period is selected the mode case cased

which dictates one of the following schemes in order from zero to seven: (red up, green down), (blue up, red down),

(green up, blue down), (blue up, green down), (green up, red down), (red up,

green up), (red up, blue up), and (green up, blue up). Once a mode is selected

we wait for the counter to increment past countMax. Once the countMax is

surpassed the first color is either added or subtracted depending if reverse is

set. Next if the scheme dictates that the second color is stationary that value

is checked. If the second color is to be stationary then the second color will

cycle by modulo 1000 by increments of 200 if the alternate value is high

otherwise it is not manipulated at all. If the second color is not to be

stationary the reverse is checked again and the second color is either added or

subtracted appropriately. If the second color is not stationary then the third

color (third color being the one note mentioned in the modes listed above) is

checked as to whether it should alternate or be set by the thirdVal register.

If the alternate bit is set high then the third color cycles through module

1000 by increments of 200 else the thirdVal case statement dictate the current

value as either zero, 250, 500, or 750. This logic is simply repeated for all eight

modes and then the red, green, and blue registers are outputted on wires and eventually

to the VGA controller for one’s viewing pleasure.

Software

There

was no software used in the functionality for our project but Matlab code was

used to generate the Draw Bars module since it involved a lot of repetitive

lines be created. See the appendix for this code.

Testing

Hardware

The assembly of the hardware for our

project implementation involved quite a few debugging techniques. The filtering

part of the project had several ways to test whether it worked or not. The

signal generator was used to input a signal with a known frequency and it was

passed into the DE2 board using the audio codec. Once the signal was inside the

FPGA it was victim to being manipulated by a large number of filters. Many

filters were used and tested and the outputs on the audio codec output were

switched using the switches on the DE2 board. Two signals could be checked at

the same time using the right and left channels on the output. The signals that

were checked on the line out were put into the oscilloscope to see what they

looked like. The value of the signal could be display on the red LEDs. The

signal generator was also used at this point to confirm how good the cutoffs

were and whether the filters were actually working. For example a 47 Hz wave

was place on the input channel and was barely seen after the cymbal and voice

filters. Although it was still seen after the bass filter.

The period calculation unit also

used a similar technique. In order to confirm the functionality of the period

calculator the signal generator output a known frequency and as a result the

period could be calculated and the order of magnitude for the number cycles

could be found. It was found at first that doing only two zero crosses only resulted

in the half period so three zero cross measurements were needed to get the same

order of magnitude for our period calculations. The period length was also

output on the HEX displays so the value could be updated when the frequency was

changed. Indeed when the frequency increased the period displayed decreased. It

was also discovered that some error could occur in measuring the period as down

sampling from audio rate to one thousand hertz could sometimes shift the zeros

around so max periods were kept for more accuracy.

When first trying to use the audio

codec and VGA controller modules it was necessary to use the red LEDs, the

green LEDs, the switches, and the HEX displays to be able to display as much

information as possible. Problems experienced with these units were undeclared

signals and clocks that were required to drive the controlling units. Once these

modules work the LEDs and hex displays were still used to display information

about the VGA display being updated. For example the Cellular automaton visualization

wouldn’t work at first so the coordinates were put on the red LEDs and the

state on the green LEDs and it was seen that incrimination of the address

halted part way through execution which turned out to be a side effect of

having moved the logic into a sub module. There was quite a bit of wasted time

during this lab in attempting to take logic that worked perfectly fine in the

top module and trying to move that logic into a sub module and having it no

longer work. The filters had a known problem of a critical timing error but

this did not show for other unit such as the Period Calculator and Cellular

Automaton modules that were attempted. Due to the lack of time these large

sections of code of were left in the top module. The oscilloscope was also used

here to see if the CIC module was work in a sub module but it appeared not to

be. Also much time was spent change various critical values inside certain

modules to see how the display would change or how closely synchronized the

music was with the visualization on the LCD display.

When creating the visualization

modules it was very helpful to try simple algorithms at first and check how

they looked visually using the VGA controller and LCD display in the lab. Numerous

additions could be made to visualization modules and displayed on the LCD

display to fine tune and ensure the correct behavior. Also the use of speakers

in the lab allowed us to see that the music was synced up fairly well with the

visualizations. The final form of testing that was used for logic that could

not be moved to sub modules and for strange behavior over the entire board Signal

Tap logic analyzer was used. The signal tap logic analyzer uses M4k blocks to

store the values of signals on the FPGA over time. As a result I could keep

track of how some of my modules were either not incrementing correctly or a

variable was being set incorrectly. Particularly when there are SRAM and VGA

display issues Signal Tap will help find the problem quickly.

Software

No software was used in our project

implementation. The software used was matlab script to write verilog which

contained all print statement so if there was an error it was printed in the

console and visibly correctible.

Results of Design

We

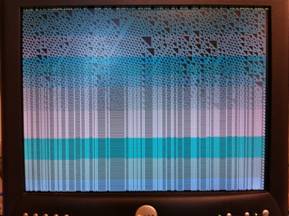

successfully implemented four different visualizations, depicted in the figure

below. Each visualization runs smoothly

with variations dictated by the audio input. The “boxes” visualization consists

of several boxes whose size and color is modulated by the audio. Cellular

automata visualization draws a random cellular automata rule on a periodic

basis depending on the bass frequencies in the audio input. The bars visualization draws 100 bars, each

representing a past sample of the audio input. It also has two boxes near the

top of the screen which are intended to appear like “eyes” whose size is

modulated by the audio amplitude. In

addition, the color is periodically altered. We also have a simple, single bar

visualization. This visualization is intended to show how our internal

filtering facilitates video synchronization with the audio. In addition to the

bar visualization there is also an LED visual that flashes with the bass beat.

One final visualization that moves a single square around the screen back and

forth in the horizontal direction. In the vertical direction the square will go

higher based on the bass beat and slowly falls when there is no bass in the

incoming audio signal.

The boxes visualization contains

some small visual artifacts (not visible in the figure) but otherwise each visualization

is displayed as desired. The filters used performed adequately. We were able to

extract bass, voice/guitar, and cymbal beats relatively well. Combined with

thresholding, our filtering displays relatively accurate synchronization with

the music beats. This is especially visible in the single bar visualization. Our project did not require safety

considerations nor did it cause interference with other designs in the lab. The

resulting project is usable by anyone, simply connect audio input to the board

and use the switches to select a visualization scheme.

Figure

6: Visualizations – Boxes (Left) – Cellular Automata (Right)

Figure

7: More Visualization – Bars (Left) – Single Bar (Right)

Figure

8: Visualization - Bars (left) – Cellular Automaton (right)

Figure

9: Visualization – Cellular Automaton (left) – Box Visual (right)

Figure

10: Visualization – Cellular Automaton on both screens

Conclusion

Our

goal was to implement audio visualization on the Altera DE2 board. Overall, we

have achieved a satisfactory end result.

Six different visualization schemes were implemented: two amplitude

modulated bar schemes, one LED mimic, single box, beat triggered cellular

automata, and amplitude modulated boxes. In addition, we implemented a

filtering scheme to improve visual and audio synchronization. Our filtering schemes utilized both period

and amplitude measurements.

Given

more time, we would have liked to explore more sophisticated filtering schemes.

We found that for complex visualizations, it was difficult to synchronize the

music with the drawing. With an improved filtering scheme, we may have been

able to synchronize better. For instance, it would be interesting to explore

filtering schemes intended to isolate single instruments from music. More time

would have also been helpful because the number of visualization schemes is

essentially endless and it would have been enjoyable to spend more time

implementing more algorithms.

There

are no standard schemes for audio visualization. In fact, we did not find

adequate documentation on any specific audio visualization implementation.

However, we can compare our audio visualization to others. The Atari Video

Music device developed by Atari Inc. in 1976 was one of the first audio

visualization devices. We believe that our implementation is comparable to the

Atari Video Music device.

Regarding

intellectual property, our IIR filters were adapted from those provided on the

ECE5760 website. Our code also uses the audio codec driver and VGA driver from

the ECE5760 website. Finally, there are no legal considerations to address

regarding our project.

APPENDIX

/////////////////////////////////////////////////////////////

/////////

Audio Visualization ///////////////////////////////

////////

ECE 5760 - Final Project ///////////////////////////

////////

Michael Lyons - mpl56 //////////////////////////////

////////

Darbin Reyes - der34 ///////////////////////////////

/////////////////////////////////////////////////////////////

wire

[31:0] mSEG7_DIG;

reg [31:0] Cont;

wire VGA_CTRL_CLK;

wire AUD_CTRL_CLK;

wire

[9:0] mVGA_R;

wire

[9:0] mVGA_G;

wire

[9:0] mVGA_B;

wire

[19:0] mVGA_ADDR; //video

memory address

wire

[9:0] Coord_X, Coord_Y; //display coods

wire DLY_RST;

assign TD_RESET = 1'b1; // Allow

27 MHz input

assign AUD_ADCLRCK = AUD_DACLRCK;

assign AUD_XCK = AUD_CTRL_CLK;

//modules

needs for Audio codec and VGA

Reset_Delay r0 (.iCLK(CLOCK_50),.oRESET(DLY_RST) );

I2C_AV_Config

u3 ( // Host

Side

.iCLK(CLOCK_50),

.iRST_N(KEY[0]),

// I2C Side

.I2C_SCLK(I2C_SCLK),

.I2C_SDAT(I2C_SDAT) );

VGA_Audio_PLL

p1 ( .areset(~DLY_RST),.inclk0(CLOCK_27),.c0(VGA_CTRL_CLK),.c1(AUD_CTRL_CLK),.c2(VGA_CLK) );

//////////////////////////////////////////////////////////

//

output to audio DAC

wire

signed [15:0] audio_outL, audio_outR ;

//

input from audio ADC

wire

signed [15:0] audio_inL, audio_inR ;

AUDIO_DAC_ADC

u4 ( // Audio

Side

.oAUD_BCK(AUD_BCLK),

.oAUD_DATA(AUD_DACDAT),

.oAUD_LRCK(AUD_DACLRCK),

.oAUD_inL(audio_inL),

// audio data from ADC

.oAUD_inR(audio_inR),

// audio data from ADC

.iAUD_ADCDAT(AUD_ADCDAT),

.iAUD_extL(audio_outL),

// audio data to DAC

.iAUD_extR(audio_outR),

// audio data to DAC

// Control Signals

.iCLK_18_4(AUD_CTRL_CLK),

.iRST_N(DLY_RST),

.isel(SW[17])

);

//////////////////////////////////////////////////////////

VGA_Controller u1 ( // Host

Side

.iCursor_RGB_EN(4'b0111),

.oAddress(mVGA_ADDR),

.oCoord_X(Coord_X),

.oCoord_Y(Coord_Y),

.iRed(mVGA_R),

.iGreen(mVGA_G),

.iBlue(mVGA_B),

// VGA Side

.oVGA_R(VGA_R),

.oVGA_G(VGA_G),

.oVGA_B(VGA_B),

.oVGA_H_SYNC(VGA_HS),

.oVGA_V_SYNC(VGA_VS),

.oVGA_SYNC(VGA_SYNC),

.oVGA_BLANK(VGA_BLANK),

// Control Signal

.iCLK(VGA_CTRL_CLK),

.iRST_N(DLY_RST) );

//

assign VGA outputs

assign

mVGA_R = SW[1] ? {SRAM_DQ[14:10], 5'b0} : SW[0] ? barR : boxR;

assign

mVGA_G = SW[1] ? {SRAM_DQ[9:5], 5'b0} : SW[0] ? barG : boxG;

assign

mVGA_B = SW[1] ? {SRAM_DQ[4:0], 5'b0} : SW[0] ? barB : boxB;

///////////////////////////////////////////////////////////////

//

SRAM_control

assign

SRAM_ADDR = addr_reg;

assign

SRAM_DQ = (we)? 16'hzzzz : data_reg ;

assign

SRAM_UB_N = 0; //

hi byte select enabled

assign

SRAM_LB_N = 0; //

lo byte select enabled

assign

SRAM_CE_N = 0; //

chip is enabled

assign

SRAM_WE_N = we; //

write when ZERO

assign

SRAM_OE_N = 0; //output

enable is overidden by WE

//

reset wire

assign

reset = ~KEY[0];

///////////////////////////////////////////////////////////////

//boxvisual

instantiation /////////////////////////////////////

wire

[9:0] boxR, boxG, boxB;

//module

boxVisual(reset, CLK50, AUDCLK, VGA_VS, audIn, cymbal,bass,voice, coordX,

coordY, period, red, green, blue);

boxVisual

box1(reset, CLOCK_50, AUD_DACLRCK, VGA_VS, VGA_HS,

audio_inL,IIR4outL_cymbal2,IIR4outL_bass2,IIR4outL_voice2,Coord_X[9:1],Coord_Y[9:1],maxPerLength,boxR,boxG,boxB);

////////////////////////////////////

//

bar pixel values

wire

[9:0] barR, barG, barB;

//module

drawBars(iHeight,iX,iY,iVGA_VS,iVGA_HS,oR,oG,oB,CLK,VGACLK,AUDCLK,CLK27,audIn,RST,state,period);

//module

drawBars(iHeight,iX,iY,iVGA_VS,iVGA_HS,oR,oG,oB,CLK,VGACLK,AUDCLK,CLK27,audIn,RST,state,period,bassH,cymbalH,voiceH,sigSel);

drawBars

uBars(.iHeight(hbitamp), //draw bars

.iX(Coord_X),

.iY(Coord_Y),

.iVGA_VS(VGA_VS),

.iVGA_HS(VGA_HS),

.oR(barR),

.oG(barG),

.oB(barB),

.CLK(CLOCK_50),

.VGACLK(VGA_CTRL_CLK),

.AUDCLK(AUD_DACLRCK),

.CLK27(CLOCK_27),

.audIn(audio_inL),

.bass(IIR4outL_bass2),

.cymbal(IIR4outL_cymbal2),

.voice(IIR4outL_voice2),

.RST(~KEY[0]),

.state(blank),

.period(maxPerLength),

.bassH(bassHbit),

.cymbalH(cymbalHbit),

.voiceH(voiceHbit),

.sigSel(SW[10:6])

);

////////////////////////////////////////////////

/////////////

CA visualization /////////////////

////////////////////////////////////////////////

//////////////////////////////////////////////////////////////////////

//most

important vars to know about

wire

reset;

reg

[17:0] addr_reg; //memory address register for SRAM

reg

[15:0] data_reg; //memory data register

for SRAM

reg

we ; //write

enable for SRAM

reg

[3:0] state; //state machine

reg

lock; //did we stay in sync?

reg

[7:0] rule; // to store the CA rule

reg

randinit; //signal to init the first line to random black/white

reg

[30:0] x_rand; //shift registers for

random number gen

wire

x_low_bit; //rand low bits for SR

reg

[8:0] x_walker; //current position coords

reg

[8:0] y_walker;

reg

[2:0] sum; //neighbors state

///////////////////////////////////////////////////////////////////////

//right-most

bit for rand number shift regs

//your

basic XOR random # gen

assign

x_low_bit = x_rand[27] ^ x_rand[30];

///

pixel controller logic

wire

[9:0] CAR, CAG, CAB;

//module

pixelController(reset, schemeReset, CLK, CLK27, AUDCLK, VGA_VS, VGA_HS, audIn,

periodIn, red, green, blue);

pixelController

unit1(reset, 8'd16, CLOCK_50, CLOCK_27, AUDCLK, VGA_VS, VGA_HS, audio_inL,

(maxPerLength>>4), CAR, CAG, CAB);

//state

names for machines that draws automata

parameter test1=4'd1, test2=4'd2, test3=4'd3,

test4=4'd4,

draw_walker=4'd5,

update_walker=4'd6, user_wait=4'd7;

//state

names for machine tha copies bottom line to top line

parameter

cinit=4'd0, cread=4'd1,csave=4'd2, cwrite=4'd3;

reg

[31:0] countCA;

reg

rand;

reg

[4:0] bassColor, cymbalColor, voiceColor;

reg

[14:0] bassFull, cymbalFull, voiceFull, audioFull;

//

on VGA control clock run CA

always

@ (posedge VGA_CTRL_CLK) begin

bassColor <=

IIR4outL_bass2[15:11];

cymbalColor <=

IIR4outL_cymbal2[15:11];

voiceColor <=

IIR4outL_voice2[15:11];

bassFull <=

IIR4outL_bass2[14:0];

cymbalFull <=

IIR4outL_cymbal2[14:0];

voiceFull <=

IIR4outL_voice2[14:0];

audioFull <=

audio_inL[14:0];

if (reset) begin //synch

reset assumes KEY0 is held down 1/60 second

//clear

the screen

addr_reg

<= {Coord_X[9:1],Coord_Y[9:1]} ; //

[17:0]

we

<= 1'b0; //write

some memory

data_reg

<= 16'b0; //write

all zeros (black)

rand

<= 1'd0;

if(rand)begin

//init top line of screen to random black white

x_walker

<= 9'd0; //start at 0,0 to make sure every pixel is assign a random color

y_walker

<= 9'd0;

randinit

<=1'b1;

end else begin

x_walker

<= 9'd1; //otherwise start one pixexl to the right to force a black border

y_walker

<= 9'd0;

randinit

<=1'b1;

x_rand

<= 31'h55555555;//init random number generator to alternating bits

end

//get

rule from switches

rule

<= 8'd1;//SW[7:0];

state

<= test1; //first state

in drawing state machine

end

else if(randinit)

begin// assign the top line random colors if SW17 is high, else single dot at

top center

if(rand)

begin//random colors

if(x_walker

<=9'd319) begin//entire line

x_rand

<= {x_rand[29:0], x_low_bit} ; //update the x,y random number gens

addr_reg

<= {x_walker,y_walker}; //write to the pixels on the top line

we

<= 1'b0; //write

if(x_rand[30])

data_reg <= SW[3] ? {1'b1,bassColor,cymbalColor,voiceColor} :

{1'b1,CAR[9:5],CAG[9:5],CAB[9:5]} ; //white pixel

else

data_reg <= 16'b0; //black pixel

x_walker

<= x_walker+9'd1; //next pixel

end

else begin

x_walker

<= 9'd1;

y_walker

<= 9'd0;

we

<= 1'b1; //stop writing to mem

randinit<=

1'b0; //done drawing random line

end

end

else begin//single dot at top center

addr_reg <= {9'd160,9'd0} ; //init to single dot

//write

a white dot in the middle of the screen

we <= 1'b0;

data_reg <= {1'b1,

CAR[9:5],CAG[9:5],CAB[9:5]} ;

randinit<= 1'b0;

end

end else if ((~VGA_VS |

~VGA_HS)) begin //sync is active low //modify display during sync*/

case(state)

test1:

begin//read self

we

<= 1'b1; //no

memory write

lock

<= 1'b1; //set the

interlock to detect end of sync interval

sum

<= 3'b0; //init

neighbor state

addr_reg

<= {x_walker,y_walker};//read self

state

<= test2 ;

end

test2:

begin//check self and read left neighbor

if(lock)

begin//must check lock before reading to make sure the right value is read

we

<= 1'b1; //no memory write

sum[1]

<=SRAM_DQ[15];

//read

left neighbor

addr_reg

<= {x_walker-9'd1,y_walker};

state

<= test3 ;

end

else state <= test1 ; //otherwise start over because addr_reg was destroyed

by VGA controller

end

test3:

begin//check left neighbor and read right neighbor

if(lock)begin

we

<= 1'b1; //no memory write

sum[2]

<=SRAM_DQ[15];

//read

right neighbor

addr_reg

<= {x_walker+ 9'd1,y_walker };

state

<= test4 ;

end

else state <= test1 ;

end

test4:

begin//check right neighbor

if(lock)begin

we

<= 1'b1; //no memory write

sum[0]

<=SRAM_DQ[15];

state

<= draw_walker ;

end

else state <= test1 ;

end

draw_walker:

begin//light up cell in next generation

if(lock)

begin// if we got this far, then the sum var it correct so spin on the lock

until you get a chance to write

we

<= 1'b0; // memory write

addr_reg

<= {x_walker,y_walker+1'b1}; //cell below this one

if(rule[sum])begin

case(SW[5:3])

3'd0:

data_reg <= {1'b1,bassColor,cymbalColor,voiceColor};

3'd1:

data_reg <= {1'b1,bassFull};

3'd2:

data_reg <= {1'b1,cymbalFull};

3'd3:

data_reg <= {1'b1,voiceFull};

3'd4:

data_reg <= {1'b1,audioFull};

default:

data_reg <= {1'b1,CAR[9:5],CAG[9:5],CAB[9:5]} ; //pixel variator unit

endcase

end

else begin

data_reg

<= 16'b0 ; //black

end

state

<= update_walker ; //move to next cell

end

else begin

state

<= draw_walker;

lock

<= 1'b1; //set the

interlock to detect end of sync interval

end

end

update_walker:

begin//update the walker

we

<= 1'b1; //no mem write

//move

to next pixel

if

(x_walker<9'd318 & y_walker < 9'd237)begin

x_walker

<= x_walker+9'd1;

state

<= test1 ;

end

else if (x_walker == 9'd318 & y_walker < 9'd237)begin

x_walker

<= 9'd1;

y_walker

<= y_walker+9'd1;

state

<= test1 ;

end

else begin

state <= user_wait;//test1 ; //done, just loop

end

end

user_wait:

begin//wait for user to do something

if

(SW[1]&SW[12]) begin

countCA

<= countCA + 32'd1;

if

(countCA > (maxPerLength)) begin

countCA

<= 32'd0;

if

(SW[2]) begin

rule

<= rule + 8'd1;

end

else begin

rule

<= maxPerLength[20:13];

end

if

(rule==8'd255) begin

if

(SW[2]) rule <= 8'd1;

else

rule <= maxPerLength[20:13];

rand

<= ~rand;

end

x_walker

<= 0;

y_walker

<= 0;

if(rand)

randinit <= 1'd1;

state

<= test1;

end

end

else begin

//randinit

<= SW[4];

state

<= user_wait;

end

end

endcase

end else begin

//show