We implemented naturally recursive Lindenmayer systems (commonly known as fractals) on an Intel Altera board to graph on a VGA screen. Our system proved to be faster than pure software programs written in both Python and C.

Introduction

There are dozens of L-Systems in existence, and for this project we implemented seven. Each was configurable via the number of iterations the system performed, the axiom to begin with, the size and color of the lines, and the starting coordinates of the system.

- Dragon curve

- Two versions of the Sierpinski arrowhead

- Two versions of the Koch curve

- Cross

- Tessellated triangles

This project was composed of two subsystems: Verilog code for the FPGA to calculate the L-Systems and graph the result, and the C code for the HPS to interface with the user. The FPGA has a faster system clock frequency and, considering the generation of L-Systems is computationally intensive, it made sense to offload that onto the faster, hardware-based part of the Altera board. Graphing on the VGA screen isn’t something that’s limited to the FPGA itself, but bandwidth would’ve been a limiting factor when transmitting large chunks of data from the FPGA to the HPS. With this in mind, graphing was kept to the FPGA, where the results were already being calculated. The HPS was instead utilized for its terminal interface, where the user was able to configure the L-System to be graphed. Any system settings were communicated to the FPGA via PIO ports to use in its computations.

High-Level Design

The formal definition of a Lindenmayer System (or L-System) is “a parallel rewriting system and a type of formal grammar.” In simpler terms, L-Systems generate fractals, which are never-ending complex patterns that are self similar at different scales such that zooming in or out will still show the same fractal pattern.

There are three main components to every L-System: an alphabet, an axiom, and rules. These configure and manipulate the strings of characters that define how the visualization should act, such as moving forward, turning 90 degrees to the right, or branching out from a previous state. The alphabet is the set of valid symbols that can be included in these strings; for example, an alphabet of {A, B} restricts any valid sentence to only contain A and B. The axiom sets the initial value for the system’s string; working within the system with alphabet {A, B}, an axiom could be “A.” Rules change the string recursively, generating new strings repeatedly and providing actions to control the movements of the growing visualization. They’re structured to take in a predecessor and a successor—the former is the input and the latter is the output after having the rule applied to it. A rule to our {A, B} system with axiom A could be “A → AB”; this would take our initial state and create the string “AB” for the next state.

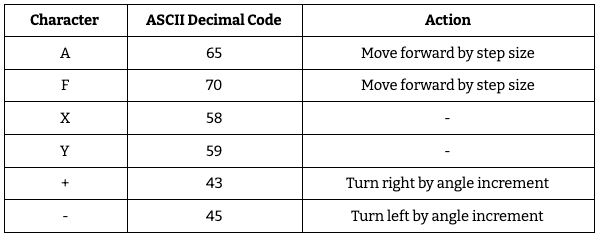

The alphabet for every phase of our design, no matter the coding language, consists of the following symbols, as shown in Table 1. Each symbol corresponds to a specific action, from graphing (which are consistent across L-Systems) to buffer characters for rule generation (specific to each L-System).

Table 1: Examples of actions associated with L-System symbols.

Though there is an infinite number of combinations of axioms and rules within the given alphabet, the seven L-Systems we developed have preset values for each. We followed these so as to ensure the graphed results would match what was expected. Table 2 shows the axioms and rules for each L-System.

Table 2: Parameters for the L-Systems in our implementation.

Baseline Design

Considering L-Systems have multiple moving parts, the most straightforward way to understand their inner mechanisms comes from our baseline designs.

Python

This Python code is an off-the-shelf implementation that we extended to incorporate the axioms and rules for

our specific L-Systems. It uses a dictionary of rules—key-value pairs where the key is the character to apply

to rule to and the value is the output string for that character—and locally declared axiom,

iterations,

angle, and step variables to iterate over a starting axiom and graph the resulting

L-System using pygame. This

is accomplished with several functions, each of which helped build the foundations for our C code and

eventually our Verilog design.

applyRule is responsible for taking in a single character and converting it to the output string

as specified

in the rules dictionary. It uses a for loop through every entry in rules to see if

any key matches the input

character. If a rule exists for this specific character, the result string is set to that rule’s value,

otherwise the result string is the original character. This exemplifies how not every character will be

expanded through a rule—at the very least it’ll just be copied into the resulting output string.

def applyRule(input): output = "" for rule, result in rules.items( ): # applying the rule by checking the current char against it if (input == rule): output = result # Rule 1 break else: output = input # else ( no rule set ) output = the current char -> no rule was applied return output

The next function is processString. Rather than take an individual character as input, it

receives an entire

string to process. Every character must be handled in order to see if a rule can apply to it, so a for loop

runs over every character and sends each to applyRule. The new string is built up with each call

to applyRule,

creating a string that will have grown in length from the original.

def processString(oldStr): newstr = "" for character in oldStr: newstr = newstr + applyRule(character) # build the new string return newstr

createSystem puts the previous two functions together to bring iterations into the mix. It takes

in axiom and

numIters as inputs, where the former is the starting string for the L-System and the latter is

the specified

number of iterations to process the string by. While processString does grow the string as it

loops over every

character, createSystem is responsible for repeating this process multiple times from iteration

number zero to

iteration number numIters-1. With each iteration, it takes the string from the previous iteration

and puts it

into processString, storing the result so that the next iteration can use it.

def createSystem(numIters, axiom): startString = axiom endString = "" for i in range(numIters): # iterate with applying the rules print("Iteration: {0}".format(i)) endString = processString(startString) startString = endString return endString

With the L-System string built through createSystem, drawTree is able to graph the

L-System using pygame. It

takes in the L-System string and the starting coordinates from which to graph. It then uses a loop to look at

every character in the string to determine what (if any) graphing functionality it needs to provide. If it

sees an ‘A’ or ‘F’ it draws forward by the length determined by step. If it sees a ‘+’ it

increments the

orientation of the system by angle, and similarly decrements the orientation of the system by

angle if it sees

a ‘-’. ‘X’ and ‘Y’ aren’t graphing characters so they, and any other characters not equal to ‘A’, ‘F’, ‘+’, or

‘-’, are skipped over.

def drawTree(input, oldpos): a = 0 # angle i = 0 # counter for process calculation processOld = 0 # old process newpos = oldpos color = (255, 255, 255) linesize = 1 for character in input: # process for drawing the l-system by writing the string to the screen i += 1 # print process in percent process = i * 100 / len(input) if not process == processOld: # print(process, "%") processOld = process if character == 'A': # magic happens here newpos = polar_to_cart(a + angleoffset, step, *oldpos) pygame.draw.line(screen, color, oldpos, newpos, linesize) oldpos = newpos elif character == 'F': newpos = polar_to_cart(a + angleoffset, step, *oldpos) pygame.draw.line(screen, color, oldpos, newpos, linesize) oldpos = newpos elif character == '+': a += angle elif character == '-': a -= angle

C

Since Python is an interpreted, high-level language, our next step was to synthesize and graph L-Systems in C code to be run on the FPGA. This did require a Quartus project to be compiled and loaded onto the board, but it wasn’t something that we changed at all. Specifically, we used the “GPU with FAST display from SRAM” project from the ECE 5760 Avalon Bus Master page.

The program layout of the Python code corresponds almost entirely with that of the C program, though it only

focuses on the dragon curve, not all seven L-Systems. First there is the applyRule_DragonCurve

function, which

is responsible for receiving a single character and outputting a character pointer to a string. This string is

built by putting the input character through a switch-case statement and seeing which condition it matches.

char* applyRule_DragonCurve(char input) { char tmp[1000000]; switch(input) { case 'X': { strcpy(tmp,"X+YF+"); break; } case 'Y': { strcpy(tmp,"-FX-Y"); break; } default: { strcpy(tmp, (char[2]) { (char) input, '\0' } ); break; } } return tmp; }

processString_DragonCurve follows the same logic as processString in the Python. It

takes in a

character

pointer to a string and then iterates on every character to put it through applyRule_DragonCurve.

The result

string from each call to applyRule_DragonCurve is concatenated together in memory.

char* processString_DragonCurve(char* prev) { int i = 0; char *tmp; char *check; int length = strlen(prev); for (i = 0; i < length; i++) { check = prev; tmp = applyRule_DragonCurve(prev[i]); strcat(prev, tmp); } return prev; }

createSystem_DragonCurve needs the number of iterations and the starting axiom to function. For

every number

in the range [0, numIters-1] it calls processString_DragonCurve on the string from

the previous

iteration.

char* createSystem_DragonCurve(int numIters, char* axiom) { char start[1000000]; strcpy(start, axiom); char end[1000000]; *end = ""; int i = 0; char *check; for (i = 0; i < numIters; i++) { check = processString_DragonCurve(start); *start = end; } return start; }

Finally, the dragon curve is drawn through the aptly named function draw_DragonCurve. It loops

through each

character in the character pointer of the L-System string and checks to see what graphing functionality that

character possesses. This leans on VGA drawing functions written by Bruce Land.

void draw_DragonCurve(char* input, int old_x, int old_y) { int a = 0; // 0 degrees is straight up vertically int length = 10; int new_x = old_x; int new_y = old_y; int i = 0; char *check = input; printf("GRAPHING STRING: "); while(*check!='\0') printf("%c",*check++); printf("\n"); for (i = 0; i < strlen(input); i++) { if(input[i] == 'X') { continue; } else if (input[i] == 'Y') { continue; } else if (input[i] == 'F') { if (a % 360 == 0) { VGA_line(new_x, new_y, new_x, new_y - length, red); new_x = new_x; new_y = new_y - length; } else if (a % 270 == 0) { VGA_line(new_x, new_y, new_x - length, new_y, yellow); new_x = new_x - length; new_y = new_y; } else if (a % 180 == 0) { VGA_line(new_x, new_y, new_x, new_y + length, red); new_x = new_x; new_y = new_y + length; } else if (a % 90 == 0) { VGA_line(new_x, new_y, new_x + length, new_y, yellow); new_x = new_x + length; new_y = new_y; } } else if (input[i] == '+') { a = a + 90; } else if (input[i] == '-') { a = a - 90; } } }

Full-System Design

Structure

Boasting a faster internal clock and configurable hardware, the FPGA is the core computational power for the

system. This power is directed towards two main functionalities: calculating the L-System and graphing the

L-System. The former relies on string manipulation, while the latter uses enable and address signals to write

to the VGA screen. Since this system serves two distinct purposes, it was useful to split each into a separate

Verilog file: rules.v for the calculations and DE1_SoC_Computer.v for the graphing.

This modular approach not

only made it simpler to visualize how each module connects, but it also made the testing process easier to

take step by step.

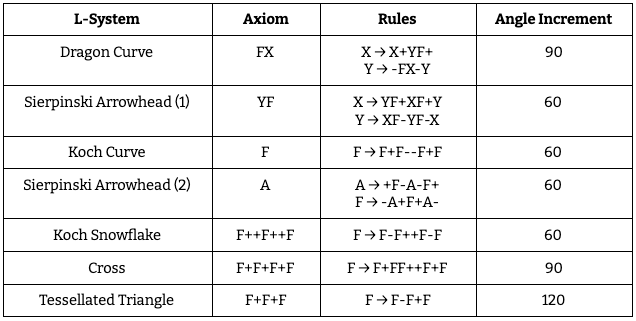

The C code running on the ARM side establishes the serial input control for the L-System’s settings, such as the L-System in question and the starting coordinates for graphing. There was the opportunity to use this for graphing as well, but the bandwidth and PIO port size limitations would’ve hindered our speedup. There was the additional thought of housing the L-System calculations on the ARM side, but this was also scrapped due to the FPGA’s faster clock frequency and opportunity for large amounts of data to be stored through M10Ks.

Bridging the gap between the ARM and FPGA is the Avalon bus, visualized and configured using QSYS. The ARM

takes in settings from the user and outputs them to the FPGA through output PIO ports, while the FPGA sends

over timing information through an input PIO port. These ports have to be programmed on both ends; the ARM

code memory maps their address spans, and the FPGA instantiates wires to connect the ports of the ARM module

(called Computer_System in the Verilog) to relevant inputs/outputs in Verilog modules.

The interweaving of these two technologies and the emphasis on each system’s strengths led to the development of responsive, visualizable L-Systems. Figure XX below shows how each connects via input and output signals and wires.

Figure 1: Block Diagram of signal flow between modules.

Computation

The bulk of the code used to create these L-Systems is found in rules.v across four modules:

dual_clock_ram,

signed_mult, rules, and create_system.

dual_clock_ram

dual_clock_ram is the memory unit of our system that allows our system to be recursive. Each

instantiation of

the module is composed of eight M10k blocks in a 8-bit by 8K configuration, with each block holding one of the

eight blocks. The module performs one cycle writes and two cycle reads. Thus, in the cycle that a memory

operation is called, a write would finish the following cycle, and a read would finish after the second

positive edge of the clock. However, it is possible for these memops to still take the same amount of time

because the read and write operations are processed on different clocks, both of which are taken as inputs

(clk1, clk2). The other inputs are write enable (we),

read_address, write_address, and write data (d). The

sole output is read data (q). When graphing, this module is the limiting factor for the number of

iterations

which can be performed. With a fixed memory size, at some point, we will run out of space to write a new

iteration. We settled on 8K memory locations because we calibrated our system to fit a 10-11 iteration dragon

curve.

signed_mult

This module performs 11.21 fixed point signed multiplication. This means that there are 11 bits of integer and 21 bits of decimal in the inputs and output. Our reasoning behind 11.21 for the fixed point representation was that there were ample integer bits, so as to avoid overflowing during computation. For the purposes of this project, we felt the ranges of integer and floating point provided good resolution. This module is instantiated in our top level code for use in calculating the necessary vertical distances for diagonal lines.

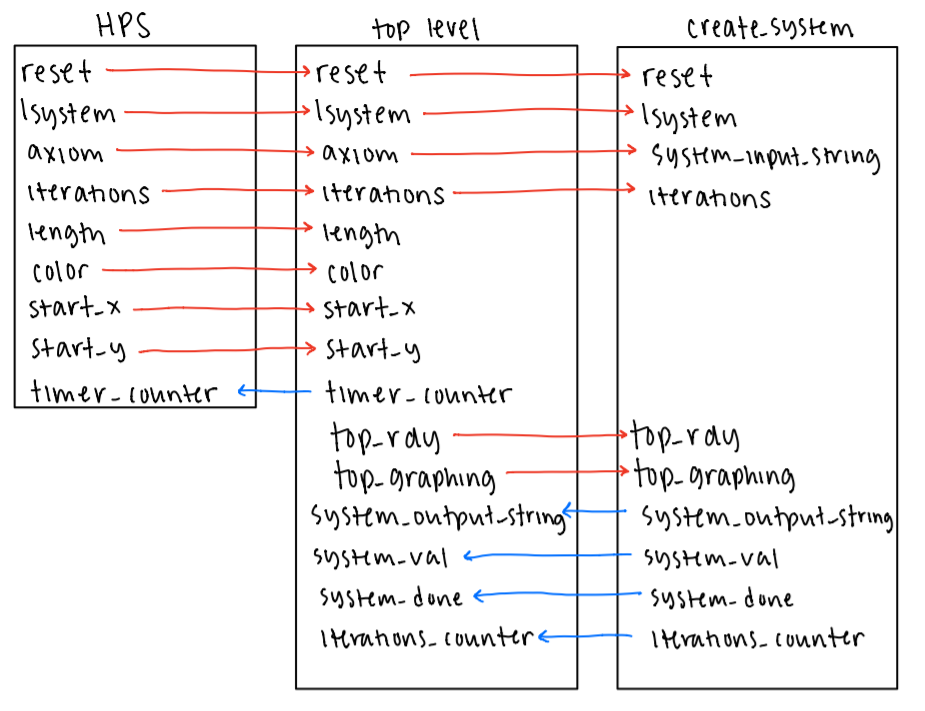

rules

rules is a clocked module which applies a specific update rule to an input character.

Specifically it takes

in an 8-bit character, and, depending on the specified L-system, will convert the input to an up to ten

character output string. To interpret the character inputs properly, the alphabet of all valid characters for

the available L-systems is defined with local parameters. The module operates by sitting in an initial wait

state until a valid signal is asserted, indicating that the input is valid. The module then transitions to the

appropriate update state depending on the input L-system signal. Within the specified state, only the rules of

that system are available. If there exists a rule for that character, the corresponding conversion will be

written to the result. If not, then the character is written to the result with 72 zeros appended to the end

to fit the ten character buffer size.

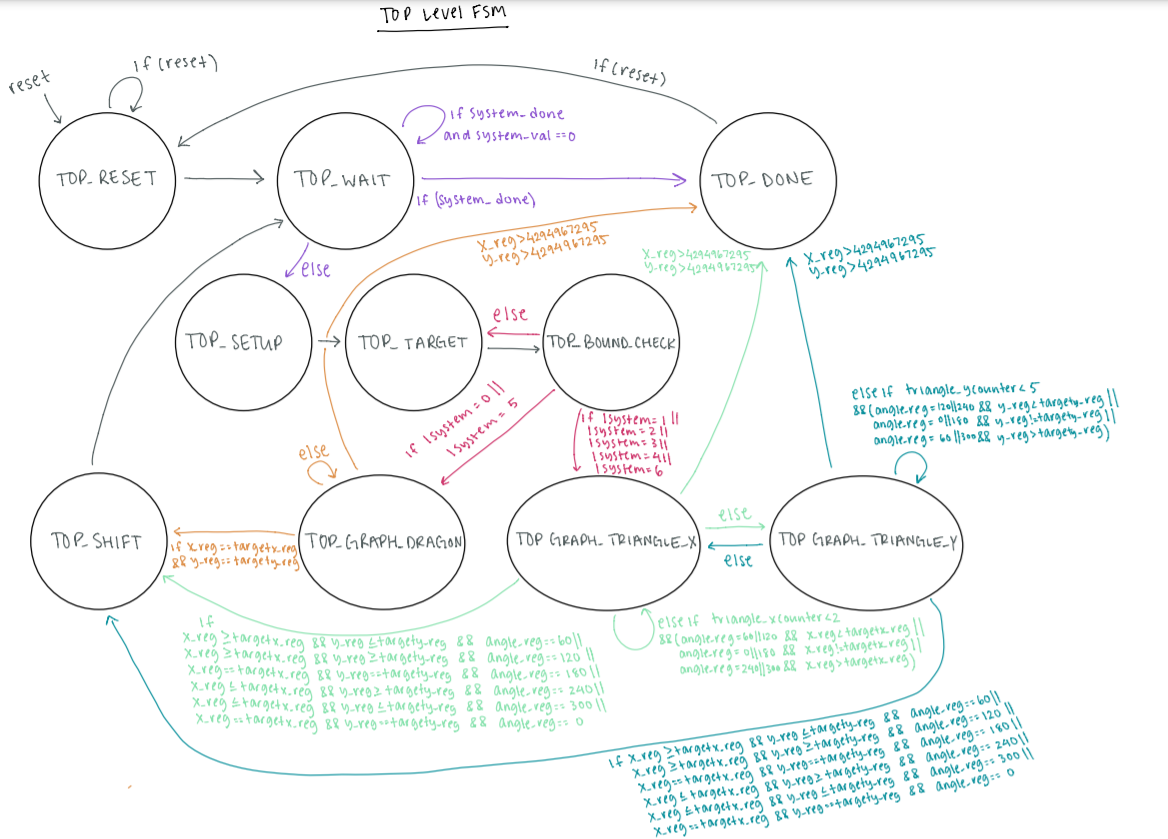

Figure 2: Diagram of the Finite State Machine used to apply rules to each character.

This scheme makes it fairly easy to add new L-Systems. We merely have to expand the alphabet and add an extra state to handle this new case. Below are examples of some of the systems we generated. We currently have 7 systems encoded. They are the dragon curve, two versions of the Sierpinski arrowhead, Koch curve, Koch snowflake, cross, and tessellated triangle.

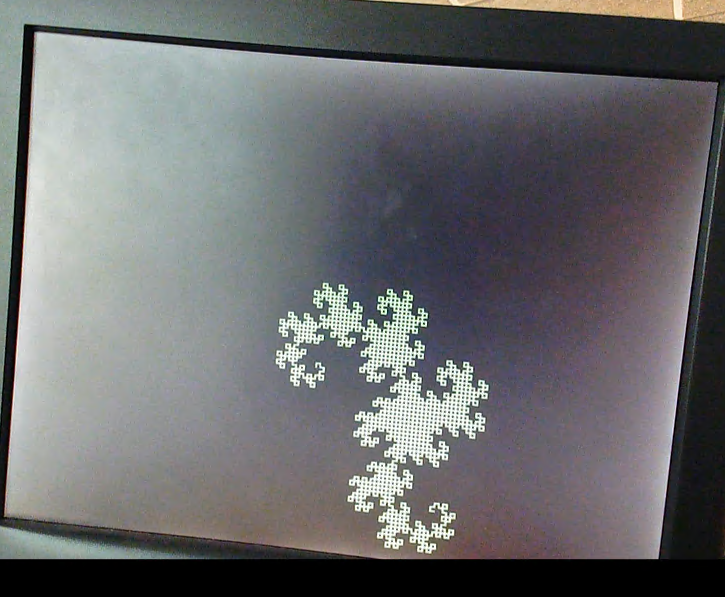

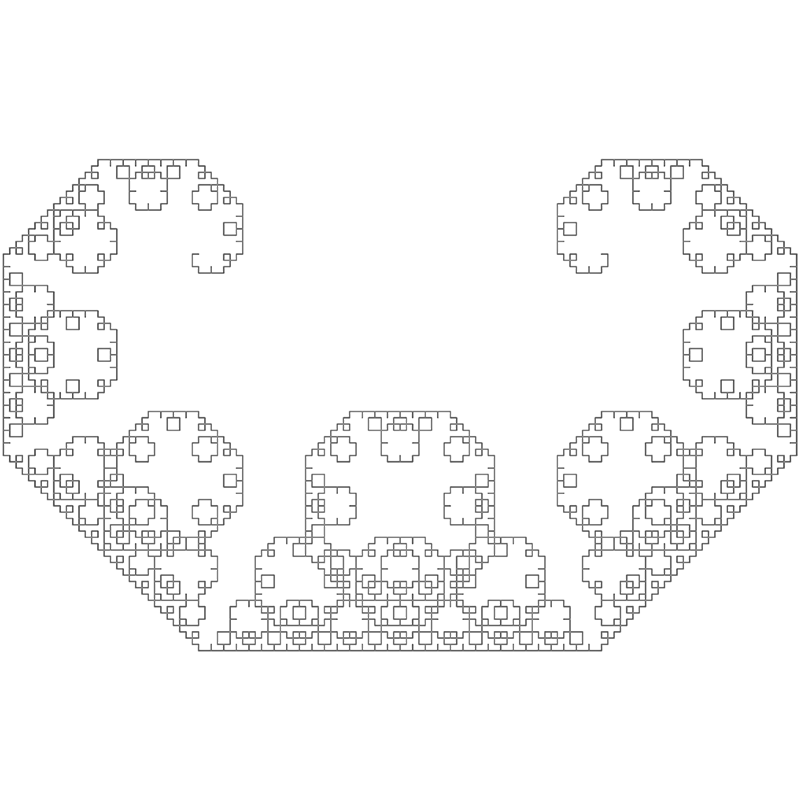

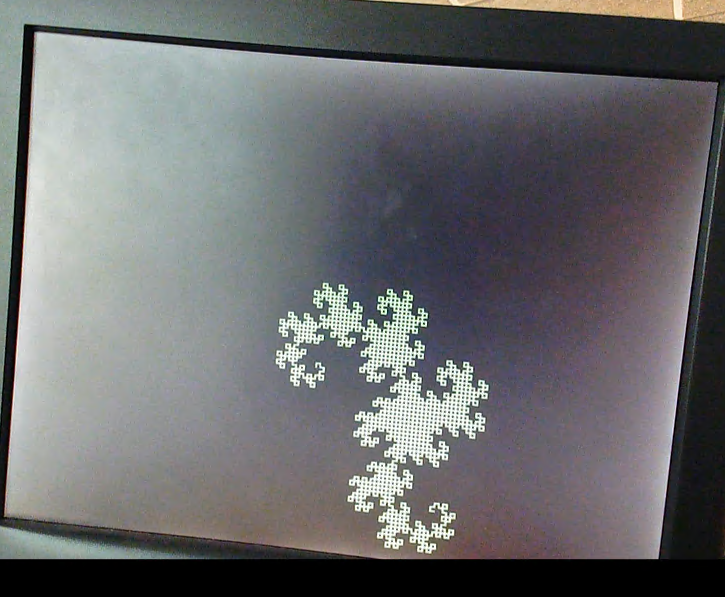

Figure 3: The Dragon Curve with 11 iterations (the largest possible in our implementation), with a length of 4, graphed in the center of the screen (300,300).

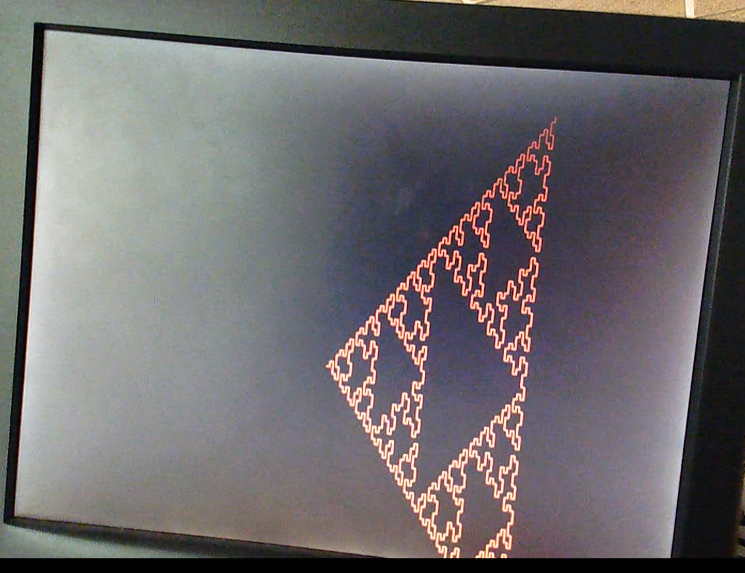

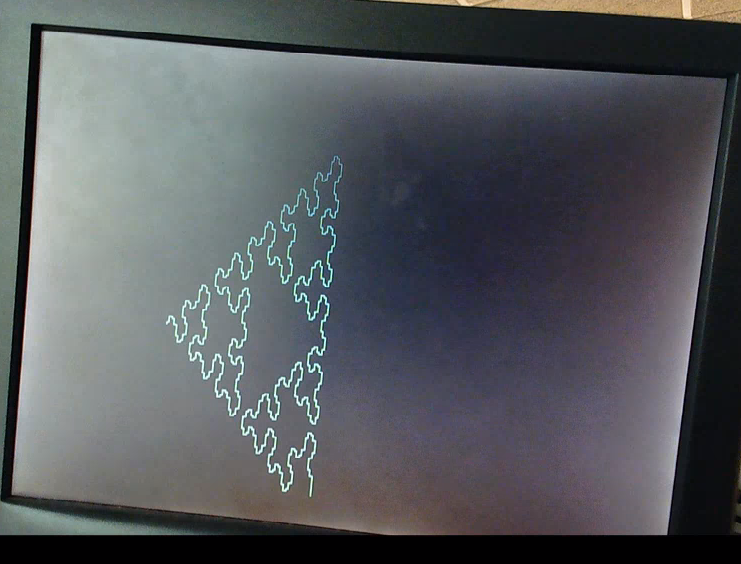

Figure 4: Sierpinski Arrowhead (2), with 6 iterations, a length of 7, graphed in the center of the screen (300,300).

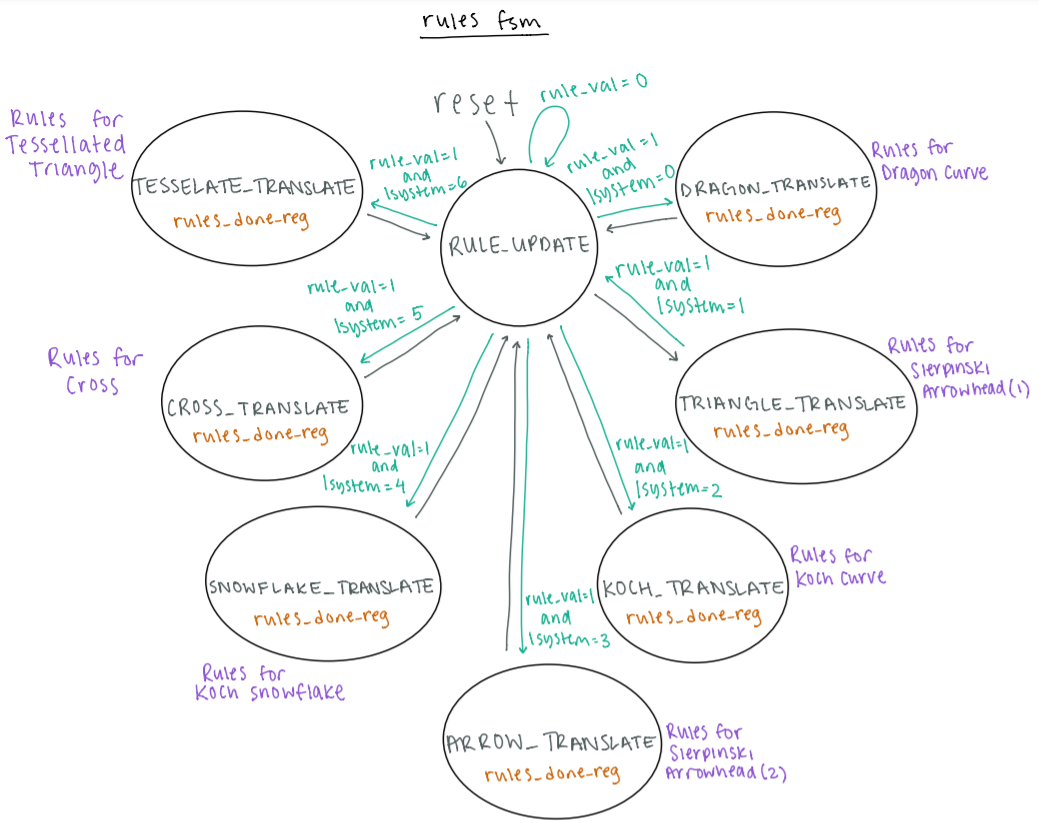

create_system

create_system in particular does the heavy lifting, instantiating two

dual_clock_ram modules and

one rules

module in order to receive a 32-bit axiom, perform the calculations necessary to convert that starting string

into a set of characters representing a fractal of that requested L-System, and output the entire result

string byte by byte to the top level.

create_system requires a plethora of input and output values in order to function. The typical

one bit clk

and reset signals are inputs to the system, dictating when the internal FSM is allowed to restart

and at what

frequency it can run. system_input_string is the starting axiom, limited to 32 bits due to the

maximum width

of the PIO ports sending over this string from the HPS. A three bit signal lsystem chooses which

of the seven

L-Systems to calculate and graph, and four bit value iterations provides the number of recursive

iterations

the L-System will be required to make. As the module hops from state to state,

system_output_string is set to

a byte of the outputted result in order to somewhat parallelize the math being performed with the graphing

being done. iterations_counter is another output, this time four bits; it’s updated to be equal

to the

iteration create_system is on so as to let the top level know when it’s appropriate to graph.

The handshake interface between create_system and the top level FSM for graphing worked with

four signals:

top_rdy, top_graphing, system_val, and system_done. Those

outputted by the top level—top_rdy and

top_graphing—were received as inputs, indicating that the top level was ready for the next byte

to be graphed

and in what stage of graphing the top level was in, respectively. system_val and

system_done are outputs, set

appropriately to show that there’s a new valid output from create_system and that

create_system has completed

its L-System entirely.

Two dual_clock_ram modules are instantiated to hold the L-System as it passes through every

iteration. The

first loop through the L-System string is performed on the axiom, which is a hard-coded value set by the user

through the HPS. The expanded result string, created by running each character through the rules

module, is

then stored in an M10K block connected to one of the dual_clock_ram modules (let’s call it A).

The next

iteration takes this processed result string from A, runs each character through the rules

module, and stores

the new result in an M10K block created by the other dual_clock_ram module (designated as B).

From then on,

every iteration of create_system will read the previous iteration’s result from one

dual_clock_ram and write

the result to the other, alternating between A being read and B being written to B being read and A being

written. Considering that iterations_counter—the register used to keep track of the

iterations—starts at zero,

here’s a simple rule of thumb: every even iteration writes to A and reads from B (except in the case of the

zeroth iteration, which reads from axiom), and every odd iteration writes to B and reads from A. The

dual_clock_ram modules will be referred to as A and B from now on.

Aptly named rule, an instance of the rules module is connected to the appropriate

inputs and internal

registers. It needs the lsystem input to choose the correct L-System rules to apply to each

character of the

L-System string, the character in question (stored in input_char), and a valid signal

rule_val to

indicate the

next character is ready to be processed. It outputs a maximum 80 bit value to rule_result after

applying the

relevant L-System rules to input_char, and a done signal rule_done used to

acknowledge that it’s

done

processing.

The mechanism propelling the creation of the requested L-System is composed of 13 states, as seen in the FSM

below. The state logic and transitions are handled within an always block clocked on the positive triggering

edge of the clk signal.

Figure 5: Diagram of the create_system Finite State Machine.

The reset signal is active high and is sent across the PIO ports from the HPS once the user has

configured

all of the desired characteristics of the L-System. On reset, all of the internal registers (most notably the

read/write addresses and write enables of both A and B, and the system_done signal) are cleared

and

system_input_string is loaded into the axiom register. The defined

RESET_SYSTEM does this as well. The

difference between the actions triggered by the reset signal and the RESET_SYSTEM

state is that

the former

only occurs once at the very beginning of the program, and the latter is what the FSM returns to after

completing an L-System and waiting for the next request from the user.

Both the reset signal condition and RESET_SYSTEM transition to

CLEAR_M10KS (though the latter

waits until

reset is high again, indicating the new L-System characteristics have been sent from the HPS). Since the

L-System strings during and between iterations are stored in M10K blocks, it’s necessary to clear them before

embarking on the next L-System. Until the write address values for A and B have reached the last possible

memory address 0h1FFF (8191 in decimal), both write enable signals are set to one and the data values set to

zero. This will result in every byte of the M10Ks being set to 8’b0. The state stays within itself until this

process is complete, then moves on to GET_CHAR.

GET_CHAR is responsible for grabbing the next character in the string to pass into the

rule

module. However,

it must wait until the top level is ready (equivalent to the top level finishing graphing the previous

character sent over from create_system) so it doesn’t set the value of input_char

for the rules

module until

the top_rdy signal is set to one. When this condition is met, how the state proceeds depends on

what iteration

the system is on, shown in iterations_counter. If the system is on the zeroth iteration, the

hardcoded axiom

is being processed so input_char is the least significant (rightmost) byte of axiom

and the FSM can

immediately transition to COMPUTE_DRAGON. If the system hasn’t reached the inputted value of

iterations, it

proceeds to READ_M10K to read a byte from the string written to either A or B’s M10K memory. If

the system has

performed the required number of iterations, the FSM goes to DONE.

READ_M10K chooses which set of M10Ks to read from based on whether

iterations_counter is even or odd. Based

on the setup of the dual_clock_ram, there’s no read enable signal; instead it takes three cycles

to read the

requested address in the M10K. Originally, we thought this meant our FSM would require some number of buffer

states to ensure three clock cycles passed before the value was ready to be used, but the fact that our FSM is

13 states means that enough time passes between individual characters being processed to absorb those three

clock cycles. We take advantage of this by incrementing the read address for the appropriate

dual_clock_ram

module within READ_M10K based on whether iterations_counter is even or odd. Since

this is the

only state to

change the value of the read addresses, A and B will read at their corresponding incremented address and the

value at that address will be ready to grab the next time the FSM goes to READ_M10K.

Whether from GET_CHAR directly or READ_M10K, the next state of the FSM is

COMPUTE_DRAGON. Don’t

let the name

fool you, as this state is responsible for getting the resulting output from applying any of the seven

L-System rule configurations, not just that of the dragon curve. The rule_val signal is set to

tell rule that

another character is on its way, and rule_result is stored in another register to be shifted in

future states

of the FSM. While the done signal rule_done is equal to zero, the FSM stays in

COMPUTE_DRAGON,

waiting for the

rule module to finish processing the character. When this isn’t the case, it’s time to write the

result to the

M10Ks: A through state WRITE_M10K_A if iterations_counter is even, or B through

state

WRITE_M10K_B if

iterations_counter is odd.

WRITE_M10K_A and WRITE_M10K_B are identical, save for the fact that they’re dealing

with two different

dual_clock_ram modules. As each memory location in the M10Ks is a byte wide, we take the most

significant

(leftmost) byte of rule_result_reg (note that this is not rule_result) and load it

into either A or B’s data

register as well as system_output_string. Every rule applied to the characters can output a

maximum of ten

bytes from a single byte input, so it takes multiple cycles to write the entirety of

rule_result_reg to the

M10Ks. The simplest way to keep track of which bytes had been written back and which ones hadn’t is by

shifting out each byte of rule_result_reg after it’s written to its appropriate location in the

M10Ks. Hence,

we know the entirety of the output from rule is stored in memory once rule_result_reg equals 80

bit zero; in

this case, the write enable is set low so as to not accidentally write to any extra memory locations,

system_val is set low to indicate that there isn’t a character to be graphed by the top level,

and the FSM

transitions to NEXT_BYTE. If there are more bytes in rule_result_reg to write to the

M10Ks, the

write enable

is set high and the top_rdy is checked. top_rdy lets create_system know

when the top

level has

finished

handling the previous character sent to it and is ready for the next. When top_rdy is high,

system_val is set

high in response to say “Hey, we have a new character ready for you!” and the FSM transitions to

INCREMENT_WRITE_A (or INCREMENT_WRITE_B when in WRITE_M10K_B, writing

to the B dual_clock_ram).

Otherwise,

system_val is kept low and the FSM stays within WRITE_M10K_A.

The goal for this val/rdy handshake is to not let one part of the system get ahead of the other. We don’t

want create_system to continue chugging along with processing and storing the result string

before the top

level is done with the previous character. We also don’t want the top level to graph a character that isn’t

ready yet, lest it mess up the final design of the L-System.

Much like WRITE_M10K_A and WRITE_M10K_B, INCREMENT_WRITE_A and

INCREMENT_WRITE_B are the same except for what

dual_clock_ram they’re interfacing with. This state is responsible for incrementing either A or

B’s write

address so that the next time the FSM is in WRITE_M10K_A or WRITE_M10K_B it knows to

write to the next

available location in memory. It’s also responsible for shifting rule_result_reg. Since the

baseline Python

code looped across each string from left to right, so does this Verilog implementation by shifting the

leftmost byte out. The FSM immediately transitions back to WRITE_M10K_A or

WRITE_M10K_B.

After the entirety of rule_result_reg has been stored in the appropriate

dual_clock_ram module,

NEXT_BYTE is

responsible for shifting axiom in a similar fashion to rule_result_reg. As described

earlier,

axiom holds the

32 bit hardcoded axiom for the L-System and is the starting point for the zeroth iteration of

create_system.

Once every character of axiom has gone through the rules module, it can be shifted

out because

there is no use

for it anymore—its result is all the system needs to remember about it, and that’s already been written to the

M10Ks. In any iteration besides the zeroth, this acts more like a buffer state than anything else, but it also

serves to hold the system_val and system_done signals low, which are easy to lose

track of.

The next state is INCREMENT_ITER; as the name implies, it’s responsible for incrementing the

value of

iterations_counter once the entirety of the string has been processed. There are many checks that

must be done

before this simple task can happen, since there are multiple cycles within the FSM and the iterations

themselves are cycles. First, system_output_string must be zero, axiom must be zero,

and

top_graphing must be

two. system_output_string being zero means that the last value of rule_result_reg is

zero and the

entirety of

the string has been processed and shifted out, with system_output_string lagging and grabbing an

extra byte of

rule_result_reg in WRITE_M10K_A/B while waiting to go to NEXT_BYTE.

axiom is zero once the zeroth

iteration

has reached its end, so this check makes sure that the system has at least gotten through that.

top_graphing

is an input from the top level showing what state of graphing the top level is in: 0 before a character is

graphed, 1 during graphing, and 2 post-graphing. A value of 2 means that the last character sent over by

create_system has been fully graphed. The next check depends on iterations_counter:

if it’s zero,

no

additional logic is needed; if it’s even, B needs to be reading a value of zero; and if it’s odd, A needs to

be reading a value of zero. This is a check to see if there are more bytes to be read and processed from the

M10Ks (hence why on the zeroth iteration this doesn’t require any logic) since all bytes in the M10Ks

following the last byte of the processed string will be zero (as promised by CLEAR_M10KS). If

those hurdles

are cleared, it’s time for iterations_counter to be incremented and the write addresses for both

dual_clock_ram modules to be zeroed out. This ensures that the next iteration will write the

result from the

top of the M10Ks, overwriting the previous iteration and even going past that (since every iteration grows the

string in length). The next state will be ZERO_READ if all of the conditionals are true,

otherwise no logic is

performed at all and the FSM heads back to GET_CHAR to start the processing and storing of the

next character

in the string.

ZERO_READ is also self-explanatory: it zeroes the read addresses for the

dual_clock_ram modules.

The read

address for B is only set to zero if the system is on an even-numbered iteration, otherwise the read address

for A is set to zero. This state transitions to GET_CHAR.

The last state of the FSM is DONE. Its primary function is to set the system_done

signal to one

in order to

let the top level know not to expect any more characters from create_system as it has completed

the requested

number of iterations over the L-System string. The read/write addresses for A and B are set to zero to prepare

to handle the next L-System after heading back to RESET_SYSTEM.

Graphing

Our top level, DE1_SoC_Computer.v, serves as the bridge between the user inputs and the

create_system module.

In addition, it holds the graphing finite state machine.

Writing to the VGA screen utilizes three signals: vga_sram_write, vga_sram_address,

and vga_sram_write

is a one bit write enable signal—if it’s 1, the VGA will be written to. vga_sram_address is a

32 bit value attributed to an address in the space of the screen, where the base address is 32’b0.

vga_sram_writedata is an eight bit value corresponding to the data to be written at

vga_sram_address,

specifically the color of the pixel located at that address.

The output PIO ports (from the ARM to the FPGA) allow for user interaction through the terminal to change the

lsystem, axiom, number of iterations, length and color of lines, as well as the

initial coordinates, start_x

and start_y. There is also an output PIO port that sends the reset signal, driven by

the HPS. In

addition, an

input PIO port sends timer_counter from the FPGA to the ARM in order to calculate the timing

information of

the system.

We instantiate a module of create_system to send over required values. Particularly, the

top_rdy

and

system_val wires allow for a handshake between the modules, so that the top level FSM does not

start graphing

too early.

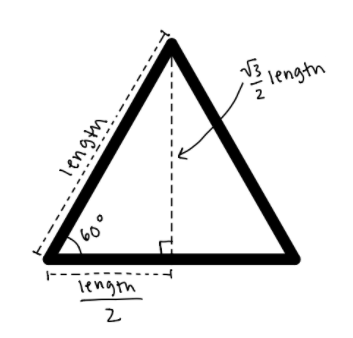

Figure 6: Annotated diagram of an equilateral triangle, to demonstrate our calculations for 60° diagonal lines.

There is also an instantiation of signed_mult, called triangle_mult, which

calculates the target pixel

required for the 60° based diagonal lines. Remembering trigonometry, we know that the horizontal step size is

length/2, which can be calculated by shifting length by 1. However, the vertical

step size is

sqrt(3)length/2,

which cannot be so easily calculated with bitwise operations. Thus, we use 11.21 fixed point multiplication.

The inputs to this module are root_three (sqrt(3) represented in 11.21 fixed point), and

x_triangle_length,

the 11.21 fixed point version of length >> 1. The output is y_triangle_length. For

use in

graphing to pixels,

the integer bits [30:21], are used in calculations. These bits omit the signed bit in the fixed point integer,

which causes a limitation in calculation values off off the screen in the negative direction.

Figure 7: Diagram of the top level (graphing) Finite State Machine.

The 10 state top level FSM is triggered on the positive rising edge of the 50MHz clock. We consider this FSM

to be modular—as in, some states are chosen based on which L-System is being graphed.

timer_counter_reg is

incremented in every state except for TOP_RESET and TOP_DONE, to provide timing

information for the whole

system.

The first state is TOP_RESET, which is entered at the reset signal from the HPS. In

this state,

angle_increment is set based on what is required for the lsystem entered. If the

reset signal is

sent again,

the FSM will stay in this state. Otherwise, it will move onto TOP_WAIT.

In TOP_WAIT, the system_done wire from create_system is checked. If it

is high, the

FSM moves

into the

TOP_DONE state. If not, there are two conditions. If the system_val wire is low, the

top_rdy_reg

is set high,

and the FSM stays in TOP_WAIT. If system_val is high, top_rdy_reg is

set low,

system_output_string_reg is set

based on the system_output_string wire from create_system, and the FSM moves into

TOP_SETUP.

The TOP_SETUP state is used to make sure all relevant registers have the most updated values. In

particular,

top_char_reg is set to system_output_string_reg, so that graphing rules can be

applied to this character in

the following state. The FSM then moves on to TOP_TARGET.

In TOP_TARGET, either the target pixels (targetx_reg and targety_reg)

or the

direction of drawing (angle_reg)

are set based on what top_char_reg is. For the drawing characters (F and A),

targetx_reg and

targety_reg are

set based on angle_reg; If angle_reg is 0 or 180 (vertical) or 90 or 270

(horizontal), either targetx_reg or

targety_reg are incremented by length. If angle_reg is 60, 120, 240, or

300, a

diagonal line is needed, and

the target coordinates are instead incremented using the step sizes calculated using the

signed_mult module

(x_triangle_length and y_triangle_length). If top_char_reg is either +

or -, angle_reg is incremented or

decremented by the angle_increment value set in TOP_RESET. In cases where the

resulting angle would be set to

360, it is reset to 0 for ease in future calculations. Next, the FSM goes into TOP_BOUND_CHECK.

TOP_BOUND_CHECK chooses which graphing state to go to based on what lsystem is. It

also chooses

to skip the

graphing states if the target coordinates are outside of the screen, and go directly to

TOP_SHIFT.

All three graphing states do an additional check on the bounds, and set the write enable,

vga_sram_write low

in the case of an offscreen pixel. This allows for a line with target coordinates outside the graphing region

to draw up until the edges of the screen.

TOP_GRAPH_DRAGON is named after our first successfully implemented lsystem, the

dragon curve,

and is the

graphing state for purely horizontal and vertical lines. In this state, either x_reg or

y_reg is

incremented

in each cycle until the graphed coordinates match the target coordinates. To graph to the screen,

vga_sram_address is set to the desired coordinates, vga_sram_writedata is set to the

color chosen

by the user,

and vga_sram_write is set high. Once the coordinates match, the FSM will move on to

TOP_SHIFT.

However, if

either the x_reg or y_reg value exceeds (2^32)-1 (the maximum value that can be held

in the 32 bit addresses),

the FSM will immediately enter TOP_DONE.

TOP_GRAPH_TRIANGLE_X and TOP_GRAPH_TRIANGLE_Y are the graphing states used for

L-Systems that require

diagonal lines. These states cycle between each other to graph 2 pixels horizontally and 5 pixels vertically,

and move on to TOP_SHIFT once the graphed coordinates has passed or is equal to the target

coordinates. This

is a limiting way to graph diagonal lines, as it requires that the minimum side length is at least 7 to result

in a line that is reasonably diagonal. However, constrained by the pixels on the screen, we found this to be a

fairly accurate way to draw lines with our desired slope.

The TOP_SHIFT state sets the top_graphing_reg to 2. This is a wire checked by

create_system before

incrementing iterations_counter_reg. After this state, the FSM returns to TOP_WAIT.

The final state in the top level graphing FSM is TOP_DONE. At this point, all graphing for the

inputted

L-System has been completed, and the final value of timer_counter_reg is used for the timing

calculations. The

FSM will stay in this state until the reset signal is sent by the HPS to bring the FSM back to

TOP_RESET.

User Interface

As previously mentioned, the HPS handles user inputs as well as printing valuable information to the terminal

window. This code can be found in graphics.c. Here is an overview of the PIO ports and the

associated actions

done by the HPS.

lsystem: before asking for a user input for this 3-bit output PIO port, the HPS prints out the

available

L-Systems and the numbers associated with them. If the user enters an invalid character, the prompt is

replayed.

axiom: Once a valid L-System has been chosen, the HPS asks for a user input for the 32-bit

output PIO port,

axiom. Before asking for it, however, the HPS prints some key information to enhance usability, including: the

default axiom for the chosen L-System, the rule-making characters in that L-System, which characters enable

drawing for that L-System, and finally, all available characters for use in the axiom. This information allows

the user to either input the default axiom (without having to look it up), or create their own unique axiom.

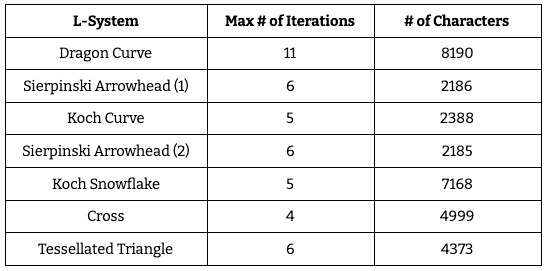

iterations: This 4-bit output PIO port holds the user inputted value for the number of

iterations. Table 3

shows our results for the largest number of iterations for each curve that can be supported by our design.

Table 3: Largest number of iterations for each curve that can be drawn in our implementation.

length: This 5-bit output PIO port holds the user inputted value for the length of each line.

This value’s

bounds are checked before moving on to the next user input. The maximum value of length is limited by the size

of the PIO port, so it must be less than 31. While that is the maximum allowed, the user must be cognizant

that lower values are often needed to project the curve within the graphable region of the screen. The minimum

length varies based on the chosen lsystem. For L-Systems that rely on purely horizontal and

vertical lines,

the minimum length is 3, in order to properly visualize squares. For L-Systems that contain diagonal lines,

the minimum length is 7, in order to properly visualize the slope of the diagonals.

color: This 8-bit output PIO port holds the user inputted value for the color of the L-System.

The HPS prints

out the available 8-colors that have been hardcoded. If the user input does not match any of the options, the

system defaults to white (0xff).

start_x and start_y: These are 10-bit output PIO ports that hold the initial

coordinates for graphing.

start_x is the horizontal coordinate, and is bounded by the left and right sides of the screen (1

to 638).

start_y is the vertical coordinate, and is bounded by the top and bottom of the screen (1 to

478).

reset: this 1-bit output PIO port allows the reset signal to be sent to the ARM.

Once the screen

is cleared,

the user can press any key to toggle this signal and begin the graphing process.

timer_counter: This 32-bit input PIO Port receives this value, which was incremented during

every cycle of

the top level FSM (except during the states TOP_WAIT and TOP_DONE). This value is

then scaled from the number

of cycles of the 50MHz clock to a recognizable time in seconds, which is printed to the terminal screen.

Once the L-System has been graphed, the user is given the option to either zoom in, zoom out, pan to new

coordinates, or begin a new L-System. The first three options modify either the length or the

starting

coordinates on the C-side of the program, and send the new values to the ARM, where the modified curve is

re-calculated and graphed again.

Testing

In the past we’ve suffered from biting off more than what we can chew, aka building a large chunk of the project before testing. This wasn’t a trap we’d be able to fall into this time, especially considering that this project is our own ideation—there’s no reference code to rely on when debugging. With this in mind, we worked through every module carefully and tested thoroughly along the way. We also initially focused our efforts on solely the dragon curve, as the 90 degree increments made for more straightforward graphing.

The first hurdle was the rules module. There were multiple ways to structure it: one module per

L-System to house

all of its specific rules, one module per character that would select between rules for each L-System, one

all-encompassing module with every single rule for every single L-System. Ultimately we chose the last design,

as we realized that it only required a single input wire to be able to toggle between rule implementations for

different L-Systems. Once that had been decided, we implemented the module as a case statement outputting to a

statically-sized register. Though we knew we wanted to utilize M10Ks for their storage capabilities, we’ve had

bad experiences with them in the past and therefore wanted to hammer down our core functionality before

complicating it with reading/writing to memory.

We used ModelSim to verify the outputs and intermediate values. The output register was simple to verify as

it simply needed to be compared to the expected output string of the L-System rule. This result wasn’t being

sent byte-by-byte either, so there were no timing issues to consider. We did run into the issue of the

characters not being accepted by the case conditions and instead falling into the default case, a behavior we

noted through displaying the rule_done signal (which, rather than being a single bit value to

toggle between

zero and one, was a two bit signal that was set to a different value in every case). This was solved by

defining the ASCII codes for each character as strict eight-bit localparams and constraining the module to

only accept a single character byte at a time.

create_system was originally broken into two modules: create_system and

process_string. Much

like the

baseline code, these separate modules iterated over a string and performed multiple iterations on a string,

respectively. We decided to combine them into a single module once we began to tackle the issue of graphing

via the top level. It wouldn’t be feasible to send over the entire result string from

process_string to the

top level because we wouldn’t know how large it was. Sending the result string byte by byte, with the top

level graphing at the same time as the computations, was a viable option, but it would be redundant for both

create_system and process_string to be handling strings byte by byte. Even more

critically, we needed to be

reading and writing to the M10Ks with every iteration, but we weren’t sure about how to have multiple modules

safely interact with the same M10Ks in parallel. Therefore, we combined the two, resulting in a rat’s nest of

FSM states and signal wires that we had to debug in ModelSim.

Before the M10Ks were in use, the result string of the overall system was limited to two bytes, hardly enough

to graph a robust L-System. While our code was operational with those limitations, there was no telling what

could happen once we allowed it to perform multiple iterations on a larger axiom. Writing to the M10Ks takes

multiple cycles per character since we have to write each byte to its own individual address, and reading from

the M10Ks requires at least three clock cycles as a buffer. ModelSim was extremely useful when debugging the

WRITE_M10K_A/B, INCREMENT_A/B, and READ_M10K states because we could

not only see what data was being

read/written but also the address at which this was occurring. Being able to see these signals informed us

that we didn’t need a separate buffer state for reading, as well as what logic should go into the transitions

out of WRITE_M10K_A/B.

Initially the axiom was hardcoded in the Verilog to not have to worry about how the terminal serial input was

being sent over the PIO ports to the FPGA. After we began to connect the C code with the Verilog, a few

confusing bugs arose. First was the issue of the order of characters in the axiom: when hardcoded, we treated

the axiom as a normal English string and processed it from left to right, but when looking at the output

signals in ModelSim we realized that they were flipped with respect to our expected values. Somehow the 32

bits of the axiom are reversed before the FPGA starts its calculations (we’re still unsure as to why this

happens, but attribute it potentially to the way memory mapping happens in the C code). In the interest of

time, we didn’t dig into the root of this problem but instead patched it by grabbing the least significant

byte of the axiom and shifting each byte out to the right, effectively reading the character string from right

to left. Another fun behavior to debug was the appearance of unexpected ones in our axiom

register as we

shifted out bytes. At first we thought it could be the way we were shifting, so we concatenated a zero byte to

a substring of the register, but that didn’t fix it. Upon closer inspection of the binary values, we realized

that the ENTER presses needed to send the serial input was being included in any input string shorter than

four bytes (the maximum length, as dictated by the PIO ports), and these enter presses didn’t have an ASCII

code of zero. Our solution was to initialize the character pointer for the axiom to four bytes of ASCII code

zero (equivalent to four spaces) so that if a byte wasn’t overwritten by the serial input, it wouldn’t affect

the register’s overall ability to be equal to zero (key in most of our transitions).

At the start of development, the modular nature of our system made it conducive to testing since all of the

signals were separated from each other and provided a good deal of information gain on their own. The

introduction of the val/rdy interface between the top level and rules.v complicated our ability

to use

ModelSim for debugging purposes since the wire values were held for too long. In the context of our full

system, ModelSim was useful for debugging the small issues that arose in individual modules but wasn’t a

viable tool when the system required more than one iteration on the string.

This is when we pivoted to SignalTap as our primary debugging tool. Though it was disadvantaged in the sense that a full compile of the Verilog was needed before SIgnalTap would read the corresponding signals, it was able to show the waveform behavior of the real system, including the Verilog and the C code. A caveat with this is the space required to store all of the hardware signals. Our design uses a good deal of memory through the M10Ks, so there’s a limit to how many data samples SignalTap can acquire. This was a detriment when testing multiple iterations, so we had to use shorter axioms and a smaller number of iterations. The discrepancies in string generation ended up stemming from smaller issues within the modules (such as the ASCII code problem) but not being able to see all of the clock cycles for more than four or five iterations made debugging more difficult.

This was especially relevant for M10K debugging, as there was a time when it seemed as though the string

being written to memory was much longer than the expected string, a problem that was exacerbated in higher

iterations. We weren't sure if it was a problem with our M10K states or M10K memory being cleared. After

noticing that this appeared on L-Systems after the first one (so not immediately after the entire board was

reset), we moved our CLEAR_M10KS state from the end of the FSM (after the DONE

state) to the beginning.

Additionally, we realized that as we grew the M10Ks we didn’t adjust the last address to which the M10K needed

to be cleared, so CLEAR_M10KS was only clearing part of memory (a pretty big problem since the

number of

iterations is incremented when an address holding a zero is reached in the M10Ks). This is a problem we had

throughout our usage of the M10Ks, as originally they were coded to have 256 memory address (meaning each

address needed eight bits) and when we expanded them to 512, 1024, and eventually 8192 we didn’t always adjust

the bit widths of the read/write memory addresses.

In regard to the top level, we were able to use the printouts to the VGA screen to debug our graphing;

particularly, this was helpful as we began to implement diagonal lines. We had decided that we would use

fixed-point signed multiplication to calculate our target pixel, and use incremented horizontal and vertical

pixels in an approximate ratio to draw lines that would appear diagonal. Our setup included separate states

for horizontal and vertical drawing, and they would alternate between each other based on a counter variable

(xcounter and ycounter). Other than a brief stint where we were accidently assigning

50-bits to one of our

32-bit fixed point variables (which caused diagonal lines to wrap all across the screen), this was mostly

smooth sailing. Eventually, we realized that our lines were not exactly the right slope for a 60° line, and

determined that we had swapped the bound check for xcounter and ycounter.

Overall, the focus on developing modular functionality made debugging a more approachable task. ModelSim and SignalTap also made looking closely at every single input, output, and intermediate value only slightly frustrating.

Future Work

There are several things that could be improved or expanded upon in future implementations of this project. First and foremost, we would refactor the top level coordinate calculations to include signed rather than unsigned variables. While graphing to the screen only requires positive pixel values, we found that calculations outside of the range of the screen would increase graphing robustness, as it would allow for the fractal to return to the screen if it curves back into the graphable region. Currently, our implementation supports calculations involving positive pixels outside the graphable region (i.e. the bottom and right side of the screen), but we encounter overflow for pixels in the negative direction (i.e. the left side and top of the screen).

Furthermore, in order to graph more robust diagonal lines, Bresenham’s line algorithm could be implemented. This algorithm would create smooth diagonal lines, and allow us to explore more L-systems based on different angle turns (such as 45° or 36°).

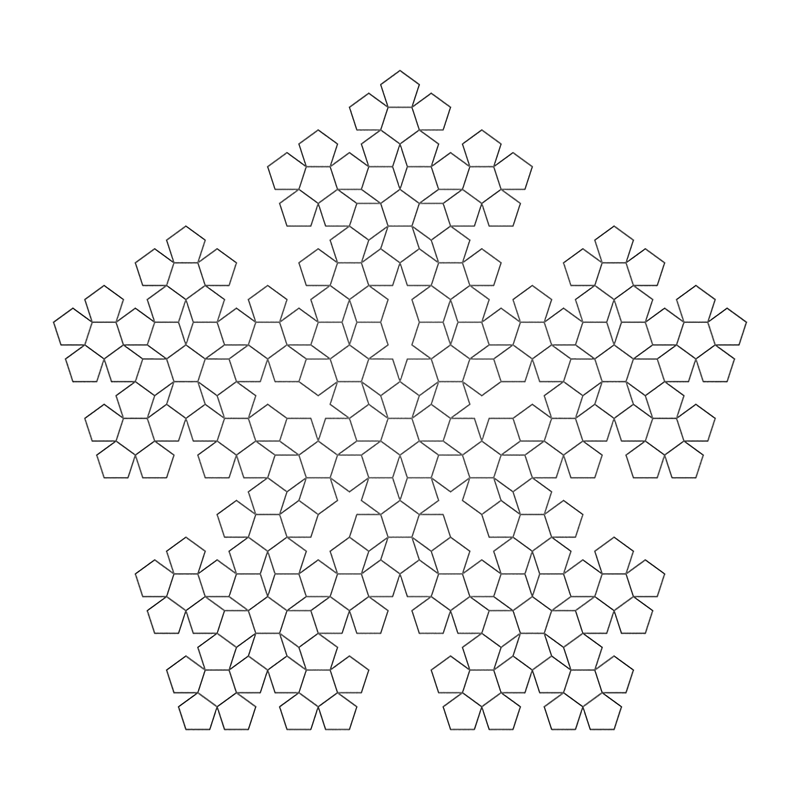

Figure 8: (A, top) Levy Curve, based on 45° angle turns. (B, bottom) Pentaplexity, based on 36°angle turns.

We would also be interested in exploring further user-customization of L-Systems. While the current system allows for customizable axioms, this could be expanded to allow users to create unique L-Systems with custom rules and customizable angle turns. This would provide ease for researchers (or other people interested in fractals) to develop new L-Systems.

Results

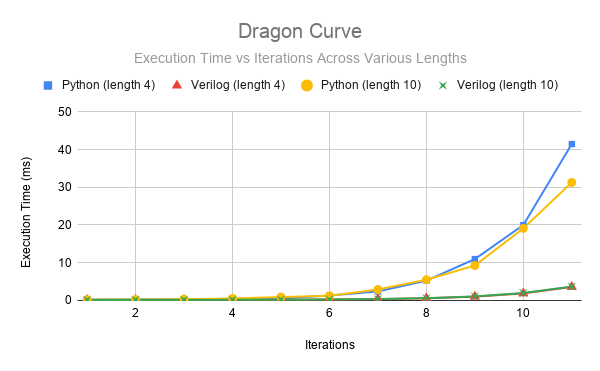

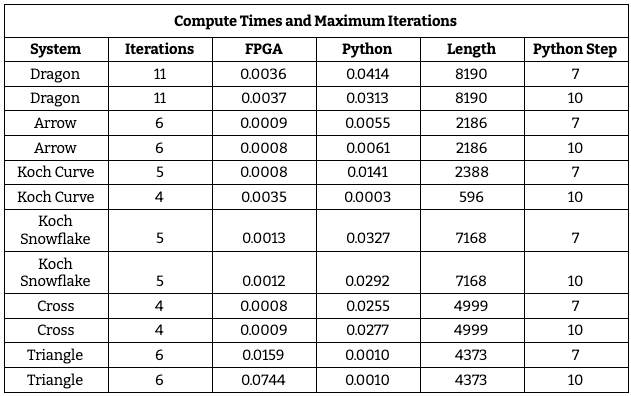

The following are some of the performance metrics of our system. Across the board, the FPGA exhibits a faster computation time than the baseline Python script. For the maximum number of iterations on each of our 6 L-systems, the worst speedup was 5.1x, and the best was 77.8x with an average of about 20.04x. This is due to a number of factors including the line length and growth rate.

.png)

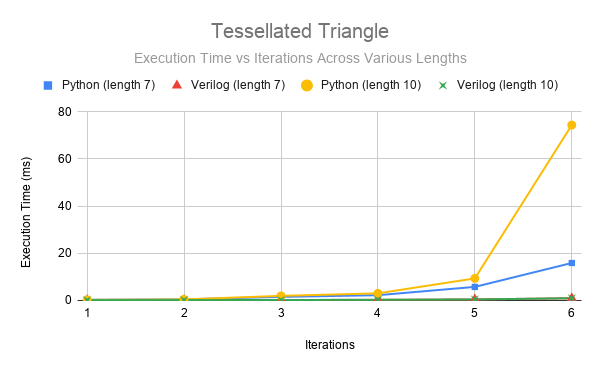

Figure 9: Execution time per character vs. Number of Iterations. Comparing the performance between the Python and FPGA when graphing the Tessellated Triangle.

Let’s take a look at this graph above. This chart shows the execution time per character for the Python and FPGA calculating the tessellated triangle. It appears that for the FPGA, there is some initial overhead with the first few iterations. This overhead is nullified by the law of large numbers at higher iterations, allowing the FPGA to settle to around 200 us per character for both the length 7 and length 10 versions. However, this does not appear to be the case for the Python code. The length 7 code takes about 3.6 ms per character, while the length 10 code takes 17ms. Additionally, although this is merely an observation, generally, the less iterations it takes to fill up the M10K blocks, i.e. a higher growth rate, the larger the disparity between the Python and FPGA.

Figure 10: The Dragon Curve with 11 iterations (the largest possible in our implementation), with a length of 4, graphed in the center of the screen (300,300).

Figure 11: Execution time per character vs. Number of Iterations. Comparing the performance between the Python and FPGA when graphing the Dragon Curve

Figure 12: Sierpinski Arrowhead (1) with 5 iterations with a length of 10, graphed starting at (300,450).

.png)

Figure 13: Execution time per character vs. Number of Iterations. Comparing the performance between the Python and FPGA when graphing Sierpinski Arrowhead (1).

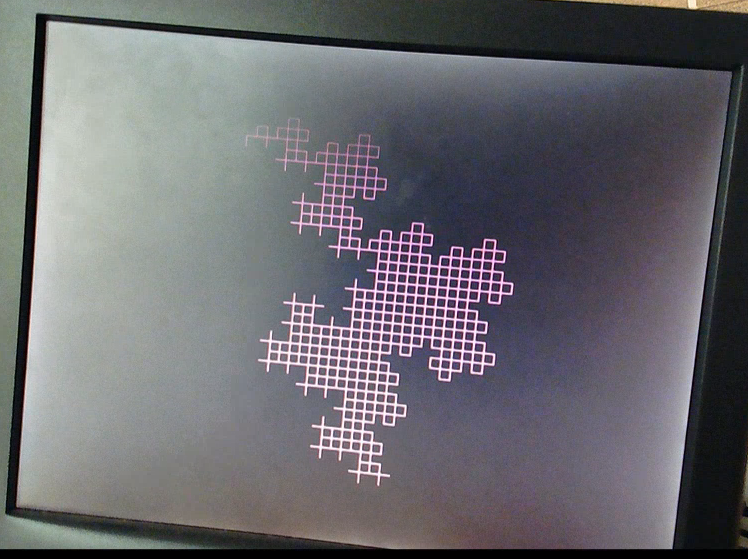

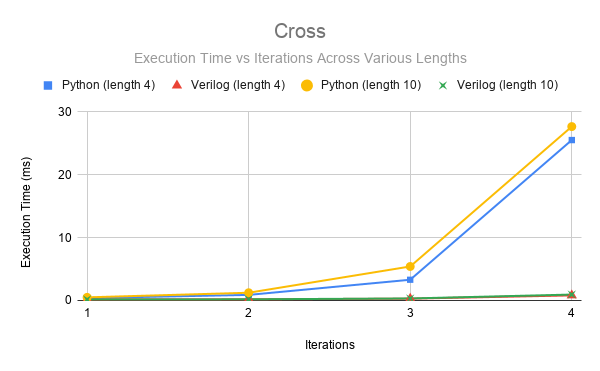

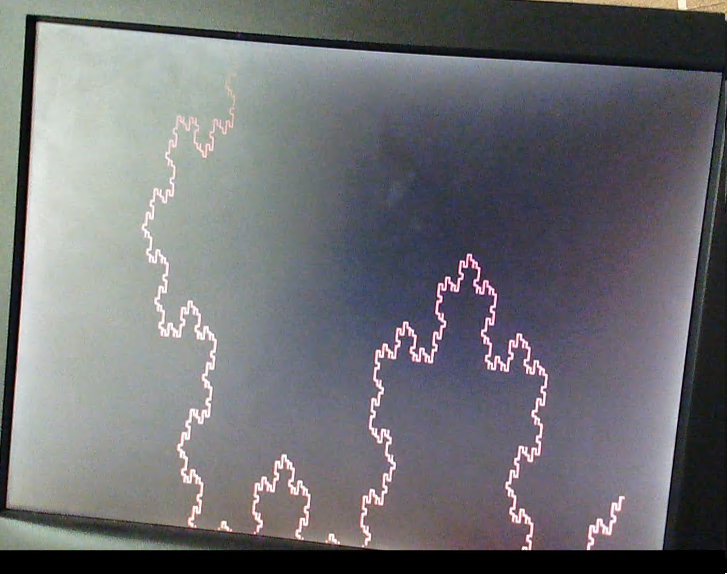

Figure 14: Cross with 4 iterations with a length of 10, graphed starting at (200,100).

Figure 15: Execution time per character vs. Number of Iterations. Comparing the performance between the Python and FPGA when graphing Cross.

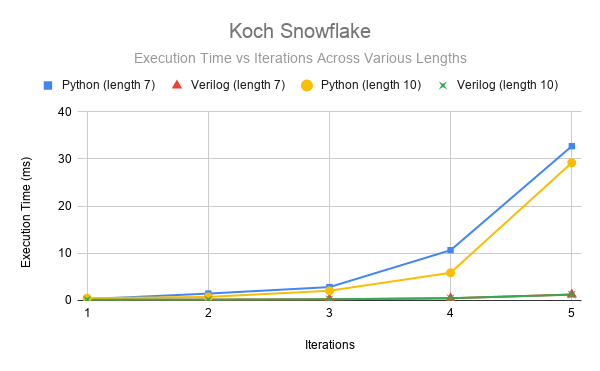

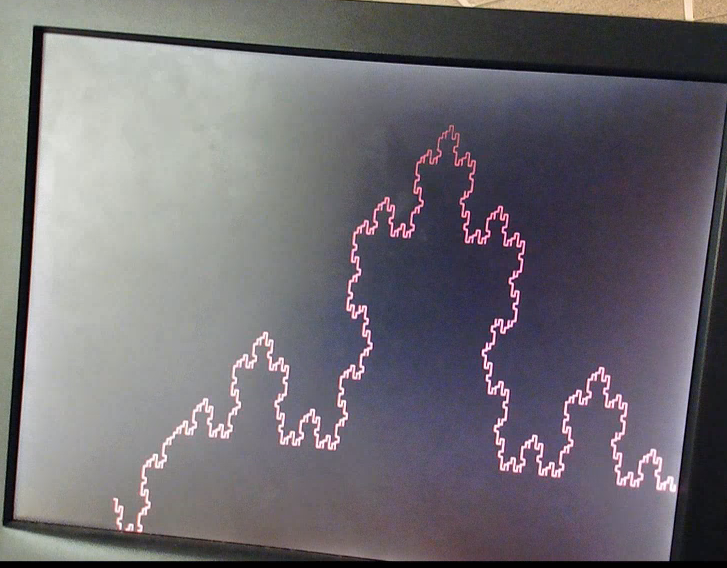

Figure 16: Koch Snowflake with 6 iterations with a length of 7, graphed starting at (600,400).

Figure 17: Execution time per character vs. Number of Iterations. Comparing the performance between the Python and FPGA when graphing the Koch Snowflake.

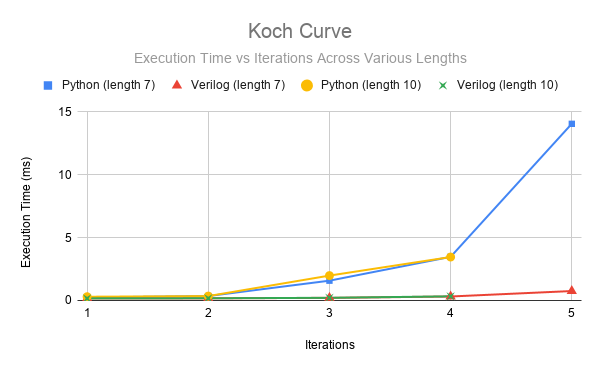

Figure 18: Koch Curve with 6 iterations with a length of 7, graphed starting at (100,450).

Figure 19: Execution time per character vs. Number of Iterations. Comparing the performance between the Python and FPGA when graphing the Koch Curve.

Figure 20: Tessellated Triangle with 6 iterations (the largest possible in our implementation), with a length of 30, graphed in the center of the screen (300,300).

Figure 21: Execution time per character vs. Number of Iterations. Comparing the performance between the Python and FPGA when graphing the Tessellated Triangle.

The M10K blocks are a limiting factor in our generation of L-Systems. As shown in these graphs, not all L-Systems are equal in terms of how fast they grow. The maximum number of characters is 8192. However, due to exponential growth, some of the largest systems we can generate are significantly less than this threshold. Additionally, we are sometimes inhibited by the negative value computation difficulty mentioned earlier. Below is a chart of the L-Systems and their maximum size on our system. Generally, there are few differences between the FPGA for edges of length 7 and length 10. For the python, it takes longer to generate the length 10 versus length 7 images. Within the results, there is only one instance of the negative values causing the FPGA to have a lower number of iterations for the length 10 graph than the length 7 graph. In all other cases, the max number of iterations is set by the M10K blocks.

A full working demo of our entire system can be found below:

Conclusion

Our original idea was to be able to animate the drawing of a fractal to the VGA screen. The user would be able to input the number of iterations and the length of the step size. They would then choose between generating a dragon curve and a fractal plant. We also envisioned adding randomness to the L-system generation. This would have been done by selecting a random rule for the given character out of a set of applicable rules, or choosing no rule and passing the character. Finally, we wanted to be able to generate multiple L-Systems simultaneously. We thought it would be interesting to have a group of trees on the screen with their own unique attributes.

Our final system is a more user driven experience. The user is allowed to select from a variety of different

L-Systems, input a desired axiom, the number of iterations, the line length, line color, and the starting

position on the screen. These values are then passed to the FPGA. The rules module is called on

the axiom,

transforming it one character at a time based on the desired L-System. This is then fed into one of the

dual_clock_ram modules. The create_system module will then ping-pong between the

dual_clock_ram

modules until

the iteration threshold is reached. The values in the M10K are then passed to the top level for graphing.

Based on the L-System, the top-level will determine the angle and coordinates of every line segment, write the

pixels to the VGA. Once this is complete, the system will be ready to accept another user input.

Unfortunately, the system is not perfect. We encountered limits on graphing in terms of the number of characters we could hold and the appearance of lines on the screen. Specifically, the M10K blocks have a finite size we cannot exceed. If we were to do this project again, we would more thoroughly investigate the size of the M10K blocks we could use in relation to access time. On the graphing end, we would implement signed registers rather than unsigned registers to mitigate the negative value issue. We would also experiment with different diagonal line drawing algorithms, at high iterations, some lines do not perfectly connect with one another. Additionally, as a feature we wish we had implemented, we would want to attempt user defined rules. This would allow a user the creative freedom to explore any L-system they desired within the character limit for rules.

In terms of safety, this project was done entirely remotely. The boards were stored in a safe, grounded environment. Students connected to them through a remote desktop to assigned computers. This was done for the health and safety of everyone involved, but also reduced the likelihood of physical damage to the boards and computers. Regarding intellectual property, the initial python code is an open source program we found. We translated this into C for our proof of concept running on the HPS. Furthermore, the base computer system module we wrote our L-system accelerator around is not ours. The base system was taken from Bruce Land’s ECE 5760 website. We modified the base as necessary for the accelerator.

Appendices

Team

Priya Kattappurath

ECE '20, MEng '21

Michael Rivera

ECE '20, MEng '20

Caitlin Stanton

ECE '20, MEng '21

Appendix A: Permissions

The group approves this report for inclusion on the course website. The group approves the video for inclusion on the course YouTube channel.

Appendix B: Work Distribution

All members contributed to the development, debugging, and demoing of the baseline and full-system designs.

- Introduction - Caitlin

- High-Level Design - Caitlin

- Baseline Design - Caitlin

- Full System Design - Priya, Caitlin, Michael

- Testing - Caitlin, Priya

- Future Work - Priya

- Results - Michael

- Conclusion - Michael

- Commented Code - Caitlin

- Diagrams - Priya

- Graphs - Caitlin, Michael

Appendix C: References

- Wikipedia: L-System

- Wolfram Alpha: Lindenmayer Systems

- What are Fractals?

- Coding a Dragon Curve

- Coding a Fractal Plant

- Wikipedia: Dragon curve

- Drawing nice L-Systems

- Drawing nice stochastic plants

- ECE 5760: VGA examples

- Recursive Modules

- Avalon Bus Master

Appendix D: Code

Here are the major files referenced in this lab report. The entirety of our code repository can be found in this Github repository.

rules.v