Abstract:

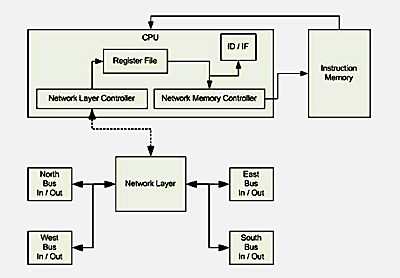

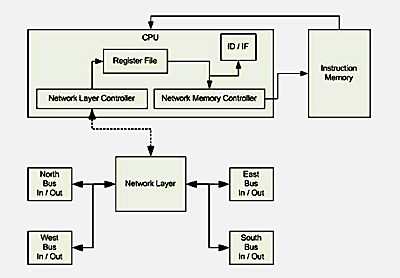

This project consisted of the design of a fully integrated extendible multi-

processor architecture and system. This included the design of the compiler,

assembler, linker, boot loader, and handshake interfacing protocols for

peripheral modules which all may or may not lie on di®ering clock domains.

The architecture is a single simple cycle RISC CPU with independent data

and instruction memories such that it is as close to pure RISC as possible.

The network layer works under the CPU transparently in a self-timed

fashion utilizing a handshake. Network communication is solely based on

instruction dispatching where each CPU is essentially capable of writing to

another CPU's instruction memory. The network is also adaptive utilizing

a unique register-thru design and message passing algorithm which allows

each node on the network to behave either as a packet switched network or

an evolved circuit switched network and a broadcast can be used to reset

the network.

Full Report (PDF)

Source code (PDF)

Source code (250 MByte ZIP)