Cornell University ECE4760

Power Managment

PIC32MX250F128B

Power Managment on PIC32

Power managment is difficult to understand because the docmentation is scattered throughout the Reference Manual, data sheet, and PLIB.

Each different peripherial section describes how the power modes effect that specific peripherial.

The following material may help in understanding power managment. Sources are from

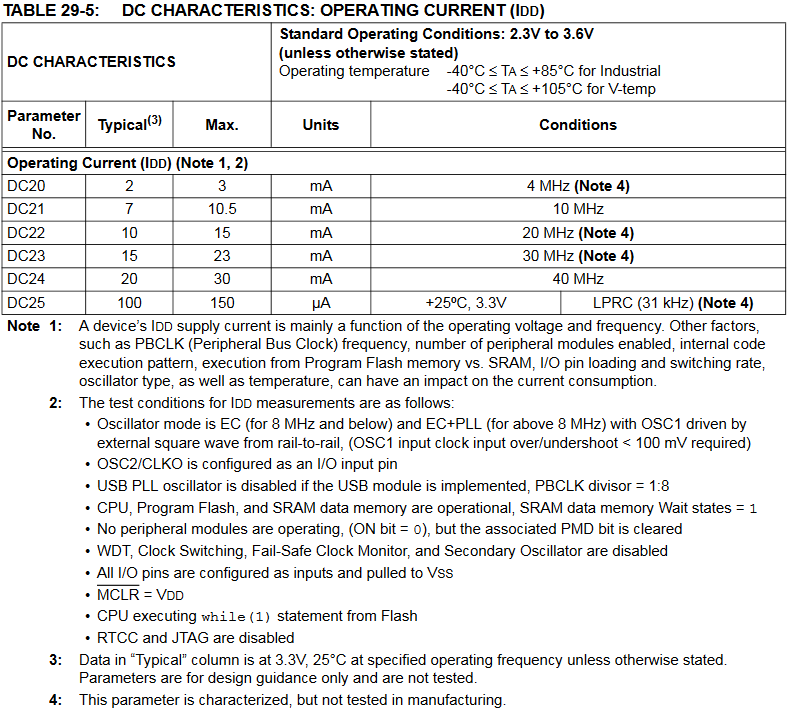

Normal operation mode:

• CMOS logic has a power requirement proportional to operating frequency.

• You can operate the CPU down to DC at reduced power.

For this cpu the constant is 0.5 mA/MHz clock when the core is running normally, but with peripherials shut down.

From the datasheet, but note the conditions!

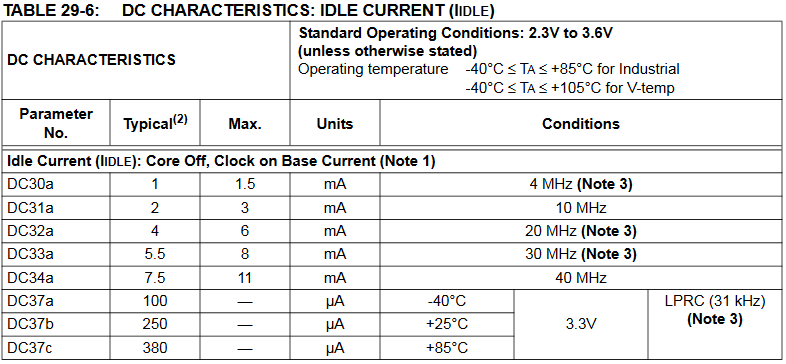

Idle mode:

• Turning off the cpu core, but leaving the clocks on lowers the power.

• This is the effect of mPowerSaveIdle()

• The clock is running and peripherials can be turned on, raising power above the values

shown below. Again,

note that power drops as you lower the frequency.

• Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit.

In general, there is a section in each peripheral chapter entitled "Operation in Power-Savings Modes"

-- For example:Timer Operation in Idle Mode. When the device enters Idle mode, the system clock sources remain functional and the CPU stops executing code. The timer modules can optionally continue to operate in Idle mode. The setting of the SIDL bit (TxCON<13>) determines whether the timer stops in Idle mode, or continues to operate normally. If SIDL = 0 , the timer continues operation in Idle mode. If SIDL = 1 , the timer stops in Idle mode.

• Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

• The processor will wake or exit from Idle mode on the following events:

-- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU.

-- On any form of device Reset

-- On a WDT time-out interrupt

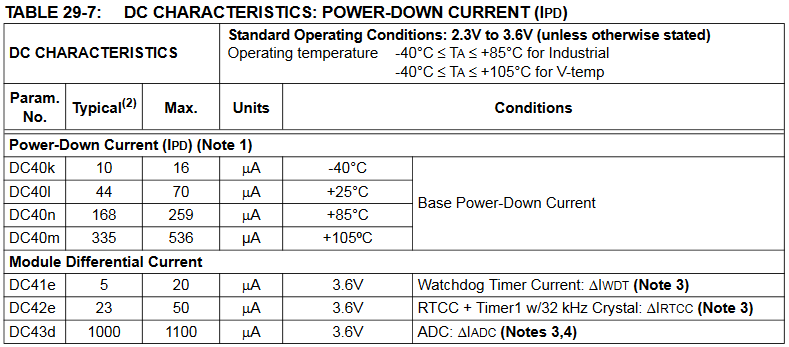

Sleep Mode:

• Turning off the system clocks puts the sustem in Sleep mode:

• This is the lowest power mode for the device. To set this mode call mPowerSaveSleep()

• The CPU, the SYSCLK source and any peripherals that operate from the SYSCLK source are halted.

• There can be a significant wake-up delay based on the oscillator selection.

• Some peripherals can cont inue to operate at limited functionality in Sleep mode.

These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an

external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

• I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep.

• The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

• Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption.

• See the individual peripheral module sections.

-- For example:

I/O pins. As the device enters Sleep mode, the system clock is disabled; however, the change notification (CN) module continues to operate. The CN pins provide PIC32 devices the ability to generate interrupt requests to the processor in response to a change of state on selected input pins. If one of the enabled CN pins changes state, the CNIF bit (IFS1<0>) will be set. If the CNIE bit (IEC1<0>) is set, and its priority is greater than current CPU priority, the device will wake from Sleep (or Idle) mode and execute the CN Interrupt Service Routine. If the assigned priority level of the CN interrupt is less than or equal to the current CPU priority level, the CPU will not be awakened and the device will enter Idle mode.

• The processor will exit, or ‘wake-up’, from Sleep on one of the following events:

--

On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

--

On any form of device Reset

--

On a WDT time-out

• The differential currents below should be added to the base Ipd current.

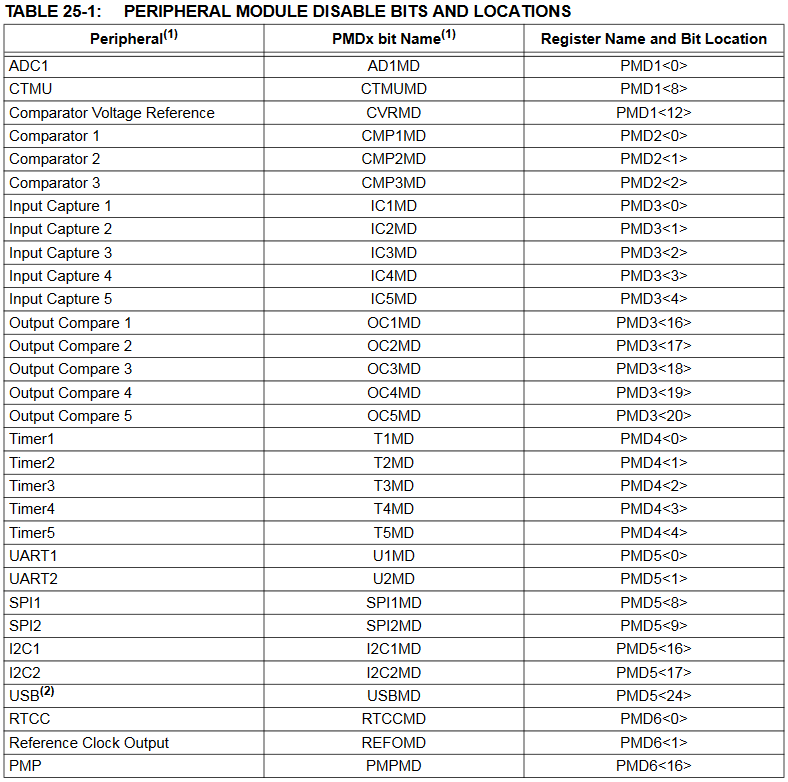

Turning off individual peripherials:

• The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

• Disabling a peripheral module while it’s ON bit is set, may result in undefined behavior.

The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

• To disable a peripheral, the associated PMDx bit must be set to ‘ 1 ’.

• To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 25-1 below.

• Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes. To set or clear PMDLOCK, an unlock sequence must be executed. Refer to Section 6. “Oscillator” in the “PIC32 Family Reference Manual” for details on the lock mechanism.

• As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PM DL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to RESET.

Commentary on PIC32 power down:

PIC32 Low power operation in which the author (Roving Dynamics) points out all of the ways

you can accidently draw current and what to do about it.

Also how to save power by slooowing down the cpu without actually putting it to sleep.

(local copy because the load time of the original is too long)

Copyright Cornell University

November 1, 2018