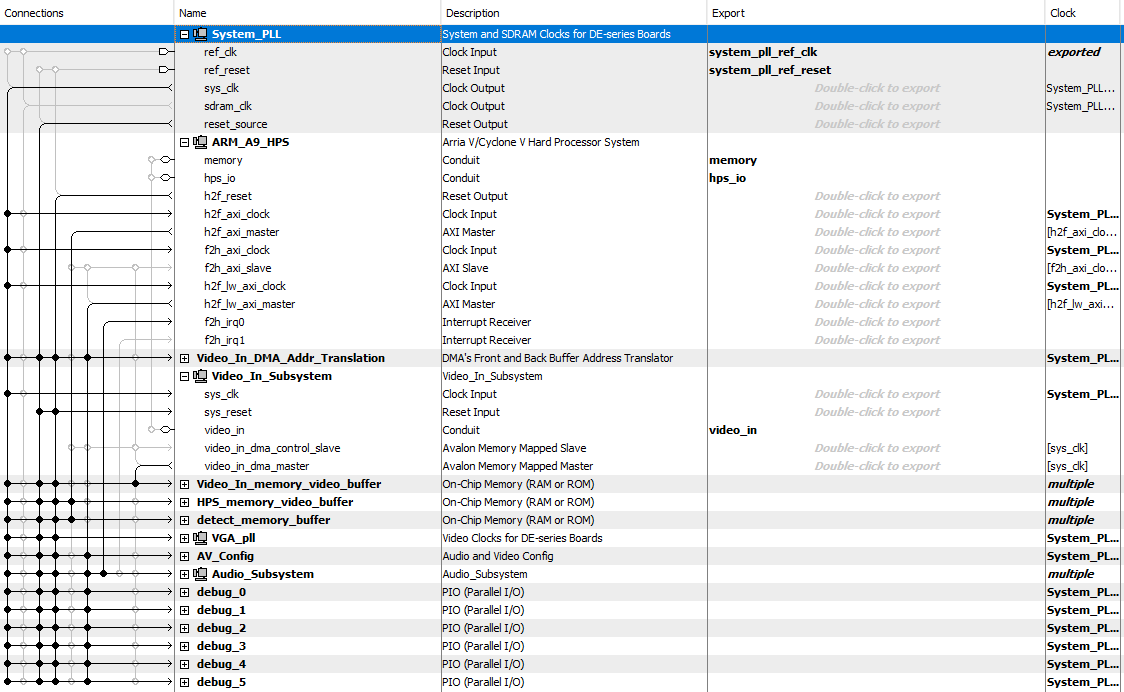

Qsys Implementation

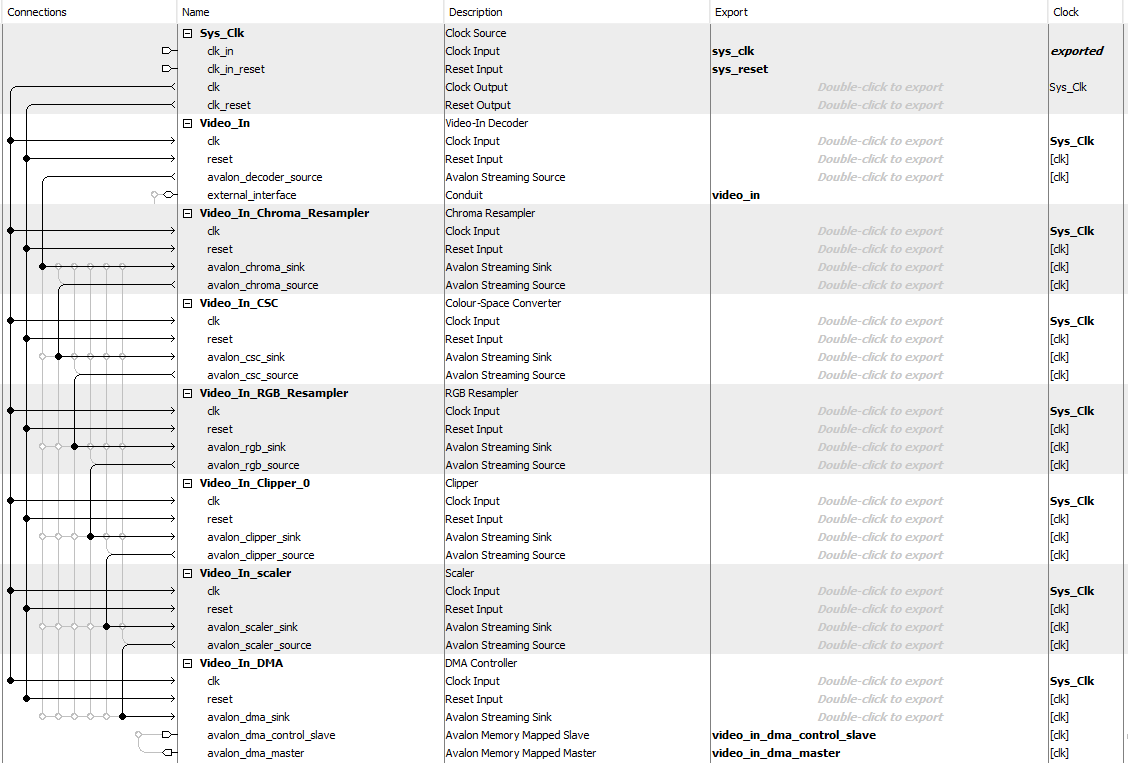

The Qsys component of the project is integral to the system’s functionality. Qsys essentially the system PLL with the logic to provide timing via the 25.175 Mhz clock, interconnects the ARM processor (HPS) to the FPGA via the heavyweight and lightweight axi busses, and integrates the camera feed (video_in), audio subsystem, and memory buffers.

The top level Qsys module - De1SoC - interconnects the system PLL, ARM, DMA

address translator, video_in subsystem (camera feed), memory buffers, audio subsystem,

and debug PIO ports. When the program is activated from the HPS, the HPS sends a signal to the

video in subsystem to turn on video capture via the lightweight bus. There are three on-chip

memory modules instantiated: video in memory buffer, detect memory buffer, and HPS memory

buffer. The video in memory buffer stores the camera feed, the HPS memory buffer stores the

graphics data, and the detect memory buffer holds the data that resembles which pixels have

been flagged when blue (or red/green) is sensed.