Appendix

Appendix A

The group approves this report for inclusion on the course website.

The group approves the video for inclusion on the course youtube channel.

The existing project we refrenced

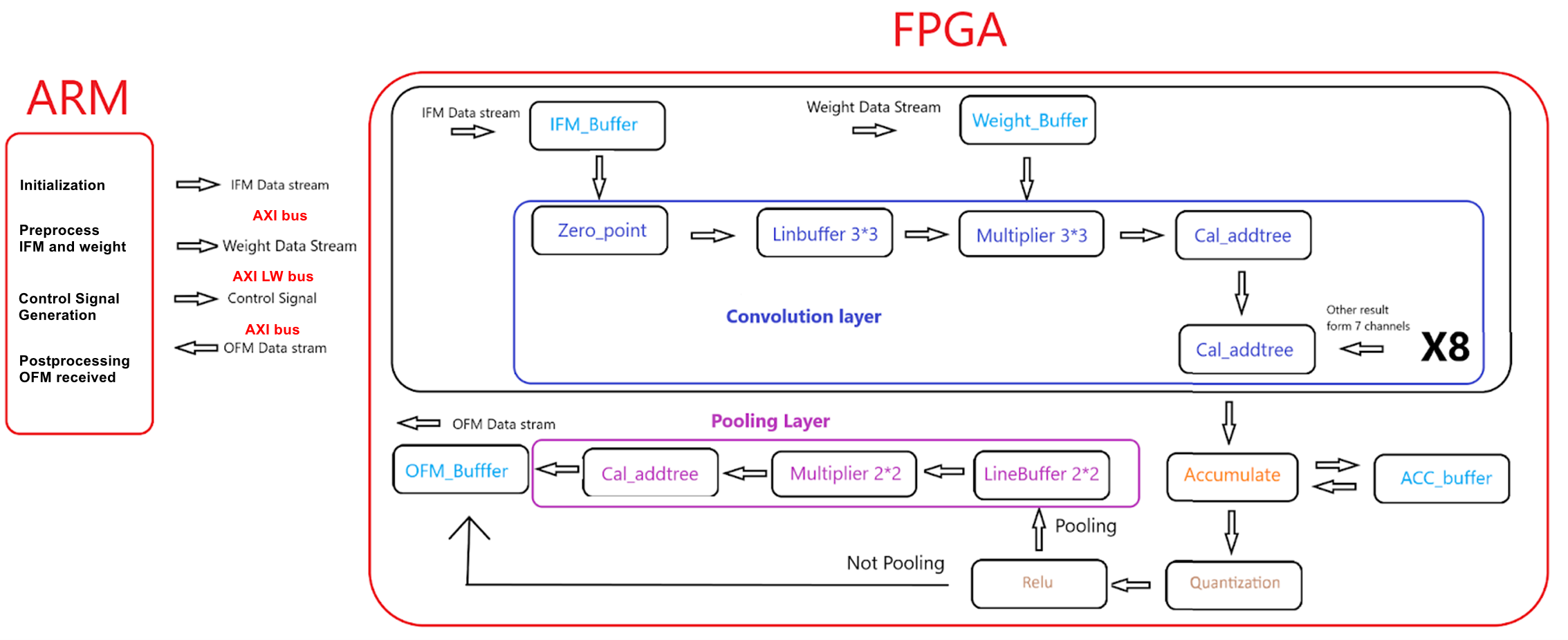

The design was based on an existing project(source: https://gitcode.com/adamgallas/fpga_accelerator_yolov3tiny/blob/main/README.md )

We reference the following source code from the existing project, utilizing them akin to an IP core to construct our own conversion layer: Module_sub_zero_point_1x8.v, module_quant.v, module_pool_kernel.v, linebuffer_3x3_type_x6.v, linebuffer_3x3_collect.v, linebuffer_2x2_type_x6.v, conv.v, com_shift_reg.v, com_mux_int8_6sel1.v, cal_sub_zero_point.v, cal_scale_shift.v, cal_scale_mul.v, cal_scale.v, cal_sat_int18_int16.v, cal_sat_int16_int8.v, cal_relu.v, cal_max_2x2.v, cal_comparator.v, cal_addtree_int18_x8.v, cal_addtree_int16_x9.v, and cal_acc.v.

Reference

[1] LeNet Visualization by Alex Lenail. Available at: https://alexlenail.me/NN-SVG/LeNet.html. Accessed on May 15th.

[2] Spatial Programming Language. Available at: https://spatial-lang.org/con. Accessed on May 15th.

[3] Max Pool Layer in NumPyNet. Available at: https://nico-curti.github.io/NumPyNet/NumPyNet/layers/maxpool_layer.html. Accessed on May 15th.

[4] GPTQ Paper on Machine Learning Systems. Available at: https://www.mlsys.ai/papers/gptq.html. Accessed on May 15th.

[5] Aranda, Luis & Reviriego, Pedro & Maestro, Juan Antonio. (2018). Protecting Image Processing Pipelines against Configuration Memory Errors in SRAM-Based FPGAs. Electronics. 7. 322. 10.3390/electronics7110322.

[6] Bruce Land, "FPGA/HPS communication," Cornell University, ECE 5760, accessed May 16, 2024, https://people.ece.cornell.edu/land/courses/ece5760/DE1_SOC/HPS_peripherials/FPGA_addr_index.html.

[7] "Accelerating YOLOv3-Tiny on FPGA." Gitcode. Available at: https://gitcode.com/adamgallas/fpga_accelerator_yolov3tiny/blob/main/README.md.